#### **Features**

- Supports Pentium or Pentium II CPUs

- Spread spectrum capability reduces EMI

- Low power consumption

- Four CPU Clocks with Vddq2 of 3.3V or 2.5V

- Seven PCI synchronous clocks (3.3V)

- One IOAPIC Clock @14.31818 MHz with Vddq1 of 3.3V or 2.5V (power from pin 46)

- Two 48/24 MHz clocks (3.3V)

- Six/eight SDRAM clocks (3.3V)

- Three Ref. Clocks @14.31818 MHz (3.3V)

- Ref. 14.31818 MHz crystal oscillator input

- Separate 66/60# MHz select pin

- Separate power management MODE control pin

- I<sup>2</sup>C 2-Wire Serial Interface

- 48-pin SSOP Package (V48)

# **Clock Generator for Pentium Notebooks** with I<sup>2</sup>C and SDRAM Support

#### Description

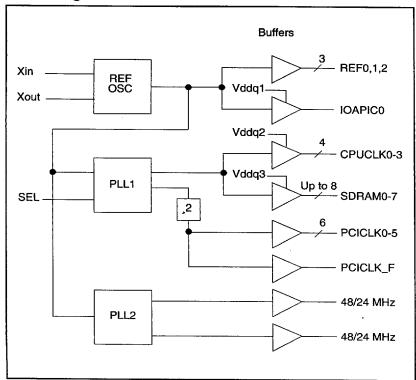

The PI6C671E is a mixed-voltage clock generator designed to provide all timing signals for Intel Pentium/Pentium II based motherboards. It provides four CPU, seven PCI, and up to eight SDRAM clocks. Additionally, three reference clocks (same frequency as the crystal) and two selectable 24/48 MHz clocks are available.

Pericom design improvements resulted in a low-power device. A special spread-spectrum feature may be enabled to minimize EMI.

The two-wire I<sup>2</sup>C serial interface can be used to reduce circuit noise and power consumption. I<sup>2</sup>C control lets you enable/disable each clock output driver, change CPU frequencies, and select 24 or 48 MHz outputs.

A power-down function (pin 44) puts the whole system in a lowpower mode by stopping the crystal oscillator and both PLLs. CPU and PCI clocks may also be stopped by the "CPU stop" (pin 27), and "PCI stop" (pin 26) functions.

Note: Purchase of  $I^2C$  components from Pericom conveys a license to use them in an I2C system as defined by Philips.

#### **Block Diagram**

### **Pin Configuration**

| REF1 [ 1        | $\bigcirc$ | 48 🖸 Vdd            |

|-----------------|------------|---------------------|

| REF0 [ 2        |            | 47 REF2             |

| Vss ☐ 3         |            | 46 D Vddq1          |

| Xin ☐ 4         |            | 45 DIOAPICO         |

| Xout ☐ 5        |            | 44 PWR_DWN#         |

| MODE ☐ 6        |            | 43 🛚 Vss            |

| Vddq3 ☐ 7       |            | 42 CPUCLKO          |

| PCICLK_F [ 8    |            | 41 CPUCLK1          |

| PCICLK0 [] 9    |            | 40 DVddq2           |

| Vss ☐ 10        | 48-Pin     | 39 CPUCLK2          |

| PCICLK1 [] 11   |            | 38 CPUCLK3          |

| PCICLK2 12      | V48        | 37 🗍 Vss            |

| PCICLK3 [ 13    |            | 36 SDRAMO           |

| PCICLK4 [] 14   |            | 35 SDRAM1           |

| Vddq3 ☐ 15      |            | 34 D Vddq3          |

| PCICLK5 16      |            | 33 D SDRAM2         |

| Vss ☐ 17        |            | 32 DSDRAM3          |

| SEL66/60# [] 18 |            | 31 🗍 Vss            |

| SDATA [] 19     |            | 30 SDRAM4           |

| SDCLK [ 20      |            | 29 SDRAM5           |

| Vddq3 ☐ 21      |            | 28 Uddq3            |

| 48/24MHz 22     |            | 27 SDRAM6/CPU_STOP# |

| 48/24MHz [ 23   |            | 26 SDRAM7/PCI_STOP# |

| Vss ☐ 24        |            | 25 🛘 Vdd            |

| L               |            |                     |

All trademarks are of their respective companies.

9002174 0002784 014

PS8116C 09/05/97

### **Pin Descriptions**

| Signal Name         | Туре   | Qty | Pin                 | Description                                                                                               |

|---------------------|--------|-----|---------------------|-----------------------------------------------------------------------------------------------------------|

| Xin                 | I      | 1   | 4                   | Crystal oscillator input or input for externally generated reference signal.                              |

| Xout                | 0      | 1   | 5                   | Crystal oscillator output. Connect to external parallel resonant crystal.                                 |

| SEL 66/60#          | I      | 1   | 18                  | Select pin for enabling 66 MHz or 60 MHz.<br>H=66 MHz, L=60 MHz. Has an internal pull-up resistor.        |

| CPUCLK (0-3)        | 0      | 4   | 42,41,39,38         | CPU & Host clock outputs. Powered by Vddq2, can be 2.5V or 3.3V.                                          |

| SDRAM               | 0      | 6   | 29,30,32,33,35,36   | SDRAM clocks 60/66 MHz. Powered by Vddq3 (3.3V).                                                          |

| SDRAM6/CPU_         | bi-dir | 1   | 27                  | MODE=1: SDRAM6, MODE=0: CPU_STOP#.                                                                        |

| SDRAM7/PCI_         | bi-dir | 1   | 26                  | MODE=1: SDRAM7, MODE=0: PCI_STOP#.                                                                        |

| MODE                | I      | 1   | 6                   | Mode Select pin for enabling power management features at pins 26 & 27. Has an internal pull-up resistor. |

| PCICLK(0-5)         | 0      | 6   | 9,11,12,13,14,16    | Low skew PCI clock outputs. TTL compatible. Powered by Vddq3 (3.3V).                                      |

| PCICLK_F            | 0      | 1   | 8                   | Free running synchronous PCI clock. Stops when in shut down mode.                                         |

| REF0,REF1,RE-<br>F2 | O      | 3   | 2,1,47              | 14.318 MHz buffered reference clock outputs.                                                              |

| IOAPIC0             | 0      | 1   | 45                  | IOAPIC0 clock outputs. Powered by Vddq1, can be 2.5V or 3.3V                                              |

| PWR_DWN#            | I      | 1   | 44                  | PWR_DWN#, active LOW.                                                                                     |

| 48/24MHz            | 0      | 2   | 22,23               | Selectable 48/24 MHz clock output. Powered by Vddq3 (3.3V).                                               |

| SDATA               | I      | 1   | 19                  | Serial data input for I <sup>2</sup> C control.                                                           |

| SDCLK               | I      | 1   | 20                  | Clock input for I2C control.                                                                              |

| Vss                 | Ground | 7   | 3,10,17,24,31,37,43 | Ground pins for the device.                                                                               |

| Vdd                 | Power  | 2   | 25,48               | Power supply for analog circuits and core logic.                                                          |

| Vddq3               | Power  | 5   | 7,15,21,28,34       | 3.3V I/O power supply.                                                                                    |

| Vddq2               | Power  | 1   | 40                  | CPUCLK power supply. Can be either 2.5V or 3.3V.                                                          |

| Vddq1               | Power  | 1   | 46                  | I/OAPIC power supply. Can be either 2.5V or 3.3V.                                                         |

### **Driver Types**

| Pin                         | Driver Type | Symbol              | Description                               |

|-----------------------------|-------------|---------------------|-------------------------------------------|

| 2,47                        | D           | REF0                | 14.318 MHz clock output.                  |

| 1                           | С           | REF1, REF2          | 14.318 MHz clock output.                  |

| 8                           | Е           | PCICLK_F            | Free running clock during PCICLK stopped. |

| 9,11,12,<br>13.14,16        | E           | PCICLK              | PCI clock outputs TTL compatible 3.3V.    |

| 22,23                       | С           | 48/24MHz            | 48/24 MHz clock output 3.3V selectable.   |

| 26,27,29,30,<br>32,33,35,36 | D           | SDRAM               | SDRAM clocks 60/66 MHz.                   |

| 38,39,41,42                 | A           | CPUCLK              | CPU and host clock outputs: 2.5V or 3.3V  |

| 45                          | В           | IOAPIC0,<br>IOAPIC1 | IOAPIC clock output: 2.5V or 3.3V.        |

📰 9002174 0002785 T50 📰

### **Power Management Functions**

Any or all clocks can be enabled or shut down via the I <sup>2</sup>C control interface. All clocks stop in the LOW state. CPU, SDRAM, and PCI clocks wait for one rising edge of PCICLK\_F followed by a falling

edge of the clock of interest before settling in the LOW state. To reduce power consumption the PI6C671E clocks may be disabled in accordance with thefollowing table.

| CPU_STOP# | PCI_STOP# | PWR_DWN# | CPUCLK, SDRAM | PCICLK    | Other Clocks | Crystal & VCOs |

|-----------|-----------|----------|---------------|-----------|--------------|----------------|

| X         | X         | 0        | LOW           | LOW       | LOW          | Off            |

| 0         | 0         | 1        | LOW           | LOW       | Running      | Running        |

| 0         | 1         | 1        | LOW           | 33/30 MHz | Running      | Running        |

| 1         | 0         | 1        | 66/60 MHz     | LOW       | Running      | Running        |

| 1         | 1         | 1        | 66/60 MHz     | 33/30 MHz | Running      | Running        |

### 2-Wire I<sup>2</sup>C Control

The I<sup>2</sup>C interface permits individual enable/disable of each clock output and test mode enable.

The PI6C671E is a slave receiver device. It can not be read back. Sub addressing is not supported. All preceding bytes must be sent in order to change one of the control bytes.

Every bite put on the SDATA line must be 8-bits long (MSB first), followed by an acknowledge bit generated by the receiving device. During normal data transfers SDATA changes only when SDCLK is LOW. Exceptions: A HIGH to LOW transition on SDATA while SDCLK is HIGH indicates a "start" condition. A LOW to HIGH transition on SDATA while SDCLK is HIGH is a "stop" condition and indicates the end of a data transfer cycle.

## I<sup>2</sup>C Serial Configuration

Byte 0: Functional and Frequency Select Clock Register (1 = enable, 0 = disable)

| Bit    | Pin No. | @ Powerup | Description                                       |

|--------|---------|-----------|---------------------------------------------------|

| 7      |         | 0         | (Reserved)                                        |

| 6      |         | 0         | (Reserved, don't change)                          |

| 5      |         | 0         | (Reserved, don't change)                          |

| 4      |         | 0         | (Reserved, don't change)                          |

| 3      | 23      | 1         | 48/24 MHz (Freq Select)<br>1 = 48 MHz, 0 = 24 MHz |

| 2      | 22      | 1         | 48/24 MHz (Freq Select)<br>1 = 48 MHz, 0 = 24 MHz |

| 1<br>0 |         | 0<br>0    | Bit1 Bit0  1 1 : Tri-State 1 0 : Spread Spectrum  |

|        |         |           | 0 1 : Test Mode<br>0 0 : Normal Operation         |

Each data transfer is initiated with a start condition and ended with a stop condition. The first byte after a start condition is always a 7-bit address byte followed by a read/write bit. (HIGH = read from addressed device, LOW= write to addressed device). If the device's own address is detected, PI6C671E generates an acknowledge by pulling SDATA line LOW during ninth clock pulse, then accepts the following data bytes until another start or stop condition is detected.

Following acknowledgement of the address byte (D2), twomore bytes must be sent:

- 1. "Command Code" byte, and

- 2. "Byte Count" byte.

Although the data bits on these two bytes are "don't care," they must be sent and acknowledged.

The I<sup>2</sup>C interface is disabled when the PWR\_DWN# pin is LOW. Preset control register contents are retained.

9002174 0002786 997 📟

# Byte 1: CPU 24/48 MHz Active/Inactive Register (1 = enable, 0 = disable)

| Bit | Pin No. | @Powerup | Description                 |

|-----|---------|----------|-----------------------------|

| 7   | 23      | 1        | 48/24 MHz (Active/Inactive) |

| 6   | 22      | 1        | 48/24 MHz (Active/Inactive) |

| 5   |         | X        | (Reserved)                  |

| 4   | N/A     | X        | CPUCLK4 (Active/Inactive)   |

| 3   | 38      | 1        | CPUCLK3 (Active/Inactive)   |

| 2   | 39      | 1        | CPUCLK2 (Active/Inactive)   |

| 1   | 41      | 1        | CPUCLK1 (Active/Inactive)   |

| 0   | 42      | 1        | CPUCLK0 (Active/Inactive)   |

# Byte 2: PCI Active/Inactive Register (1 = enable, 0 = disable)

| Bit | Pin No. | @Powerup | Description                |

|-----|---------|----------|----------------------------|

| 7   |         | X        | (Reserved)                 |

| 6   | 8       | 1        | PCICLK_F (Active/Inactive) |

| 5   | 16      | 1        | PCICLK5 (Active/Inactive)  |

| 4   | 14      | 1        | PCICLK4 (Active/Inactive)  |

| 3   | 13      | 1        | PCICLK3 (Active/Inactive)  |

| 2   | 12      | 1        | PCICLK2 (Active/Inactive)  |

| 1   | 11      | 1        | PCICLK1 (Active/Inactive)  |

| 0   | 9       | 1        | PCICLK0 (Active/Inactive)  |

# Byte3: SDRAM Active/Inactive Register (1 = enable, 0 = disable)

| Bit | Pin No. | @Powerup | Description              |

|-----|---------|----------|--------------------------|

| 7   | 26      | 1        | SDRAM7 (Active/Inactive) |

| 6   | 27      | 1        | SDRAM6 (Active/Inactive) |

| 5   | 29      | 1        | SDRAM5 (Active/Inactive) |

| 4   | 30      | 1        | SDRAM4 (Active/Inactive) |

| 3   | 32      | 1        | SDRAM3 (Active/Inactive) |

| 2   | 33      | 1        | SDRAM2 (Active/Inactive) |

| 1   | 35      | 1        | SDRAM1 (Active/Inactive) |

| 0   | 36      | 1        | SDRAM0 (Active/Inactive) |

Byte 4: SDRAMActive/Inactive Register (1 = enable, 0 = disable)

| Bit | Pin No. | Description               |

|-----|---------|---------------------------|

| 7   | N/A     | SDRAM15 (Active/Inactive) |

| 6   | N/A     | SDRAM14 (Active/Inactive) |

| 5   | N/A     | SDRAM13 (Active/Inactive) |

| 4   | N/A     | SDRAM12 (Active/Inactive) |

| 3   | N/A     | SDRAM11 (Active/Inactive) |

| 2   | N/A     | SDRAM10 (Active/Inactive) |

| 1   | N/A     | SDRAM9 (Active/Inactive)  |

| 0   | N/A     | SDRAM8 (Active/Inactive)  |

# Byte 5: Peripheral Active/Inactive Register (1 = enable, 0 = disable)

|     |         |          | F                        |

|-----|---------|----------|--------------------------|

| Bit | Pin No. | @Powerup | Description              |

| 7   |         | X        | (Reserved)               |

| 6   |         | X        | (Reserved)               |

| 5   |         | 1        | (Reserved)               |

| 4   | 45      | 1        | IOAPIC (Active/Inactive) |

| 3   |         | Х        | (Reserved)               |

| 2   | 47      | 1        | REF2 (Active/Inactive)   |

| 1   | 1       | 1        | REF1 (Active/Inactive)   |

| 0   | 2       | 1        | REF0 (Active/Inactive)   |

# Byte 6: Optional Register for Possible Future Requirements

| Bit | Pin Number | Description |

|-----|------------|-------------|

| 7   | Х          | (Reserved)  |

| 6   | X          | (Reserved)  |

| 5   | Х          | (Reserved)  |

| 4   | X          | (Reserved)  |

| 3   | Х          | (Reserved)  |

| 2   | X          | (Reserved)  |

| 1   | Х          | (Reserved)  |

| 0   | х          | (Reserved)  |

9002174 0002787 823 📟

PS8116C 09/05/97

#### **Byte 7: Frequency Control**

| Bit | @ Power up | Description |

|-----|------------|-------------|

| 7   | X          | (Reserved)  |

| 6   | X          | (Reserved)  |

| 5   | X          | (Reserved)  |

| 4   | X          | (Reserved)  |

| 3   | X          | (Reserved)  |

| 2   | 1          | FSEL2       |

| 1   | 1          | FSEL1       |

| 0   | 1          | FSEL0       |

| FSEL2 | FSEL1 | FSEL0 | Frequency          |

|-------|-------|-------|--------------------|

| 0     | 0     | 0     | (Reserved)         |

| 0     | 0     | 1     | (Reserved)         |

| 0     | 1     | 0     | (Reserved)         |

| 0     | 1     | 1     | 33 MHz             |

| 1     | 0     | 0     | 50 MHz             |

| 1     | 0     | 1     | 55 MHz             |

| 1     | 1     | 0     | 60 MHz             |

| 1     | 1     | 1     | From SEL66/60# pin |

## **DC Specifications**

### **Absolute Maximum DC Power Supply**

| Symbol | Supply Voltage  | Min. | Max. | Units |

|--------|-----------------|------|------|-------|

| Vddq3  | 3.3V Core & I/O | -0.5 | 4.6  |       |

| Vdd    | 3.3V Core       | -0.5 | 4.6  | ] ,,  |

| Vddq2  | 2.5/3.3V I/O    | -0.5 | 4.6  | V     |

| Vddq1  | 2.5/3.3V I/O    | -0.5 | 4.6  |       |

# DC Operating Requirements (Vdd, Vddq3=3.3V $\pm 5\,\%$ , Vddq2=2.5V $\pm 5\,\%$ , Ta=0 to 70°C)

| Symbol | Parameter                    | Condition                              | Min. | Type. | Max. | Units |

|--------|------------------------------|----------------------------------------|------|-------|------|-------|

| Voh2   | 2.5V Output<br>High Voltage  | Ioh = -1mA                             | 2.1  |       |      |       |

| Voh3   | 3.3V Output<br>High Voltage  | Ioh = -1mA                             | 2.4  |       |      |       |

| Vol2   | 2.5V Output<br>Low Voltage   | Iol = 1mA                              |      |       | 0.4  | V     |

| Vol3   | 3.3V Output<br>Low Voltage   | Iol = 1mA                              |      |       | 0.4  | ,     |

| Idd    | Dynamic Supply<br>Current    | 66MHz<br>Unloaded<br>Outputs           |      | 55    | 70   | mA    |

| Ipd    | Power Down<br>Supply Current | PWR_DWN# = 0<br>MODE = Float<br>(High) |      | 14    | 20   | μА    |

Note: Typical values are at room temperature

9002174 0002788 76T 1

### **Driver Specifications**

| Symbol | Parameter                                   | Condition     | Minimum       | Typical | Maximum | Units |  |

|--------|---------------------------------------------|---------------|---------------|---------|---------|-------|--|

|        | Type A: CPU 2.5V Buffer                     |               |               |         |         |       |  |

| Iohmin | Pull-up Current                             | Vout = 1.0V   | -49           |         |         |       |  |

| Iolmin | Pull-down Current                           | Vout = 1.2V   | 48            |         |         | mA    |  |

|        |                                             | Type A: CPU   | 3.3V Buffer   |         |         |       |  |

| Iohmin | Pull-up Current                             | Vout = 1.0V   | -69           |         |         | A     |  |

| Iolmin | Pull-down Current                           | Vout = 1.6V   | 63            |         |         | mA    |  |

|        |                                             | Type B: IOAPI | C 2.5V Buffer |         |         |       |  |

| Iohmin | Pull-up Current                             | Vout = 1.4V   | -36           |         |         |       |  |

| Iolmin | Pull-down Current                           | Vout = 1.0V   | 36            |         |         | mA    |  |

|        |                                             | Type B: IOAPI | C 3.3V Buffer |         |         |       |  |

| Iohmin | Pull-up Current                             | Vout = 1.0V   | -58           |         |         | _     |  |

| Iolmin | Pull-down Current                           | Vout = 1.9V   | 57            |         |         | mA    |  |

|        | Type C: REF1, REF2, 48/24 MHz (3.3V) Buffer |               |               |         |         |       |  |

| Iohmin | Pull-up Current                             | Vout = 1.0V   | -29           |         |         |       |  |

| Iolmin | Pull-down Current                           | Vout = 1.95V  | 29            |         |         | mA    |  |

|        | Type D: REF0, SDRAM (3.3V) Buffer           |               |               |         |         |       |  |

| Iohmin | Pull-up Current                             | Vout = 2.0V   | -54           |         |         | A     |  |

| Iolmin | Pull-down Current                           | Vout = 1.0V   | 54            |         |         | mA    |  |

|        | Type E: PCI Clock Buffer                    |               |               |         |         |       |  |

| Iohmin | Pull-up Current                             | Vout = 1.0V   | -33           |         |         | mA    |  |

| Iolmin | Pull-down Current                           | Vout = 1.95V  | 30            |         |         | шл    |  |

- **=** 9002174 0002789 6T6 **=**

#### **AC Timing**

| Symbol     | Parameter                                                                                  | Minimum | Maximum | Unit |

|------------|--------------------------------------------------------------------------------------------|---------|---------|------|

| tRF        | Host CLK rise/fall time, 0.4V - 2.0V                                                       | 0.4     | 1.6     | ns   |

| tJITTER    | Host CLK Jitter                                                                            |         | 250     | ps   |

| Duty Cycle | Measured the rising edge CLKs at 1.25V for the 2.5V clocks and at 1.5V for the 3.3V clocks | 45      | 55      | %    |

| tHSKW      | Host Bus CLK skew                                                                          |         | 250     | ps   |

| tHSKSD     | Host to SDRAM                                                                              |         | 500     | ps   |

| tPKPS      | PCI CLK period stability                                                                   |         | 500     | ps   |

| tPSKW      | PCI Bus CLK skew                                                                           |         | 500     | ps   |

| tHPOFFSET  | Host to PCI Clock Offset                                                                   | 1       | 4       | ns   |

| tSTB       | CLK Stabilization at power-up                                                              |         | 3       | ms   |

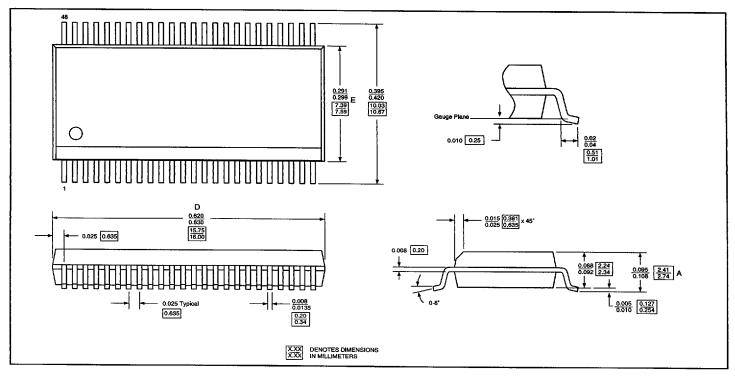

# **48-Pin SSOP Package Data** Table of Dimensions

| Body      |      | E (Width) | D (Length) | A (Height) | e (Pin-to-Pin pitch) |

|-----------|------|-----------|------------|------------|----------------------|

| 48 pins   | Min. | 0.291     | 0.620      | 0.095      | 0.025                |

| (300 mil) | Max. | 0.299     | 0.630      | 0.110      | _                    |

### **Ordering Information**

| P/N       | Description         |

|-----------|---------------------|

| PI6C671EV | 48-pin SSOP Package |

### **Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com

9002174 0002790 318 1

PS8116C 09/05/97