June 1997

# **Audio Link Processor**

### Features

- Performs ITU G.711, G.722, and G.728 Audio Compression for H.320 Video Conferencing

- Provides Sub-Band Acoustic Echo Cancellation to Support High Quality Video Teleconference Audio and Speaker Phone Interfaces

- PCI 2.1 Compliant Interface

- Glueless Interface to Industry Standard Audio Codec (CS4231A, AD1845)

- Glueless Interface to Harris Video Codec (HMP8364)

- I<sup>2</sup>C Bus Master Port

- · Plug and Play Support

- · Complete H.320 Reference Design Available

- 3.3V Operation with 5V Tolerant Inputs

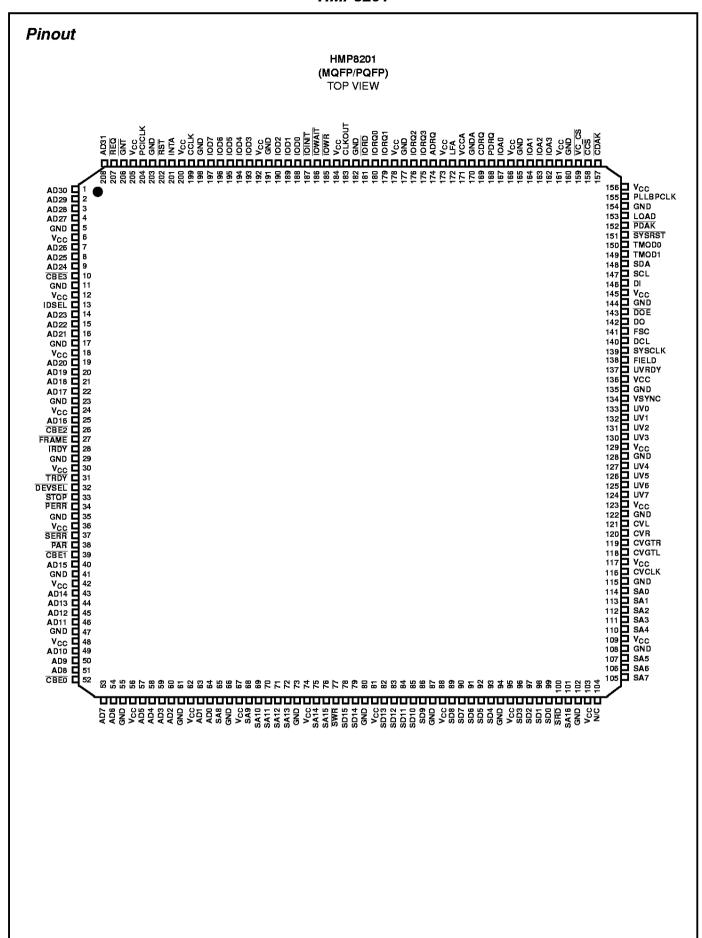

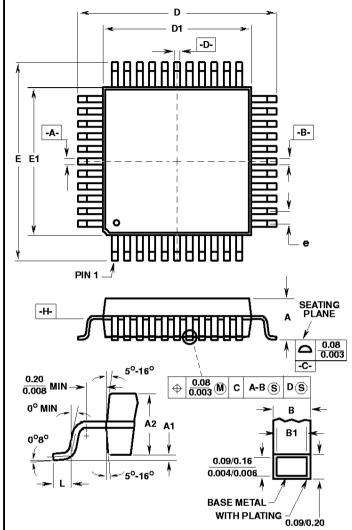

- 208 Lead PQFP Package

# **Applications**

- ITU H.320 Video Conferencing

- Audio Processing for Speaker Phone Applications

- Multimedia PC Applications

- Related Products

- H.261 Video Codec: HMP8364

- NTSC/PAL Video Decoder: HMP8112

NTSC/PAL Video Encoder: HMP8156

- H.320 Video Conferencing Reference Design

### Description

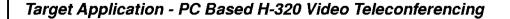

The Harris Audio Link Processor (ALP) combines high performance audio processing with a PCI bus interface to support implementation of ITU H.320 Video Conferencing using the Harris Video Conferencing Chipset.

The ALP provides a complete solution for the audio layer of ITU H.320. The audio processing includes full duplex implementations of ITU G.711, G.722 and G.728 audio compression, with wideband and narrowband acoustic echo cancellation to enable the use of a "hands free" speaker phone type interface.

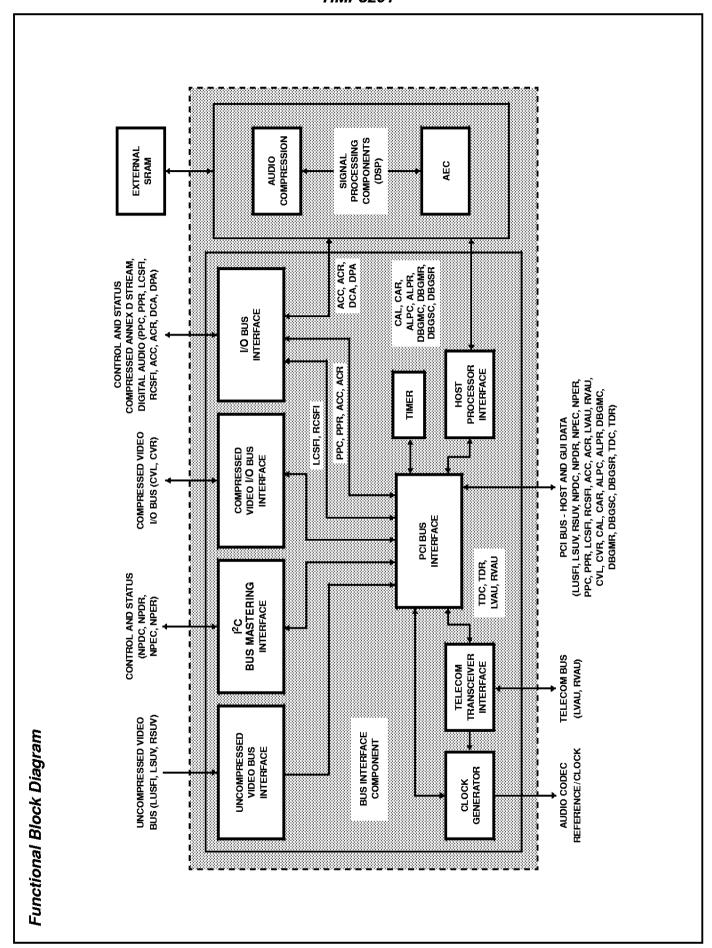

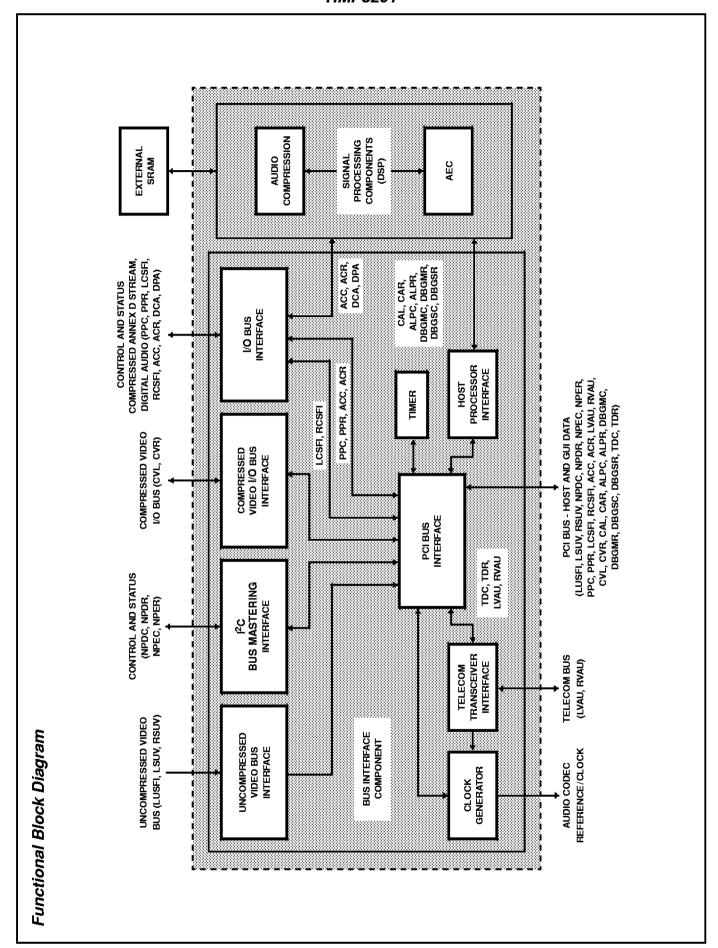

In addition to audio processing the ALP provides a PCI interface to manage data flows between the host and the Harris Video Conferencing chipset. The PCI interface supports control and data flows between the host system and the H.261 Video Codec, the audio codec, the video encoder/decoder, and the ISDN modem. As shown in the block diagram, these data flows are routed to the various ICs via an I<sup>2</sup>C bus, an 8-bit general purpose I/O bus, a telecom interface supporting the MVIP or IOM2 standards, and buses for compressed and uncompressed video.

Additional information on register programming and software support may be obtained in the accompanying programming and technical reference manual for the HMP8201 and the Harris Reference Design.

# Ordering Information

| PART<br>NUMBER | TEMP.<br>RANGE ( <sup>O</sup> C) | PACKAGE               | PKG. NO.   |

|----------------|----------------------------------|-----------------------|------------|

| HMP8201CN      | 0 to 70                          | 208 Ld PQFP<br>(Note) | Q208.28x28 |

NOTE: PQFP is also known as QFP and MQFP.

| Table of Contents                                          |   |

|------------------------------------------------------------|---|

| PAGE                                                       | Ξ |

| Functional Block Diagram                                   |   |

| Target Application - PC Based H-320 Video Teleconferencing |   |

| Pinout                                                     |   |

| Pin Description                                            |   |

| Electrical Specifications                                  |   |

| PCB Layout Considerations                                  |   |

| 1.0 Data Flows                                             |   |

| 1.1 Control Flows                                          |   |

| 1.2 Major Data Paths                                       |   |

| 2.0 Description of Functions                               |   |

| 2.1 Bus Interface Component                                |   |

| 3.0 Description of Registers                               |   |

| 3.1 PCI Register Space                                     |   |

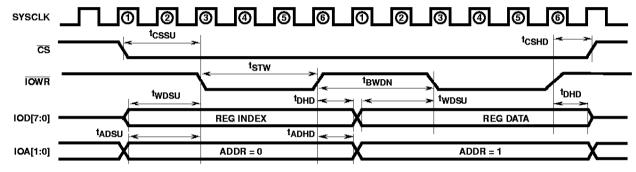

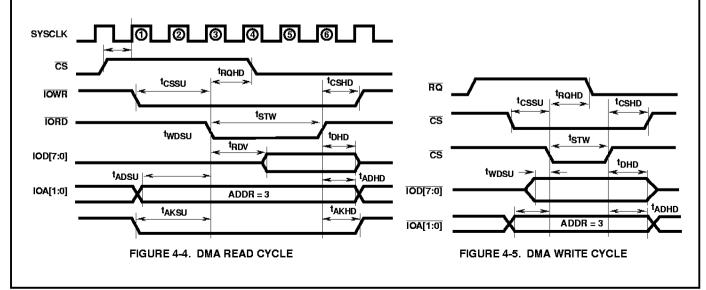

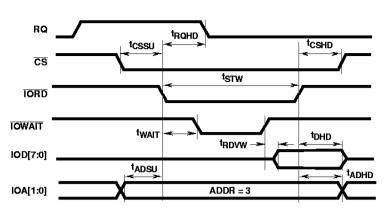

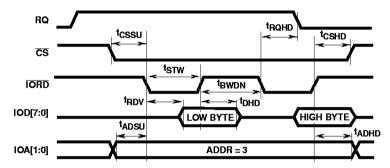

| 4.0 Timing Diagrams                                        |   |

| 4.1 Pin Timing                                             |   |

| 4.2 External Cycle Timing                                  |   |

| 4.3 Internal Cycle Timing                                  |   |

| Metric Plastic Quad Flatpack Packages (MQFP/PQFP)          |   |

### Introduction

The Harris Audio Link Processor (ALP) combines flexible audio processing capabilities with sophisticated PCI bus interface functions to support implementation of the International Telecommunications Union (ITU) H.320 videoconferencing recommendation. The ALP provides a complete solution for the audio (ITU G.7xx) layers of ITU H.320. In addition, it includes an sub-band based acoustic echo cancellation (AEC) algorithm that greatly reduces annoying speech echo during full duplex audio communication.

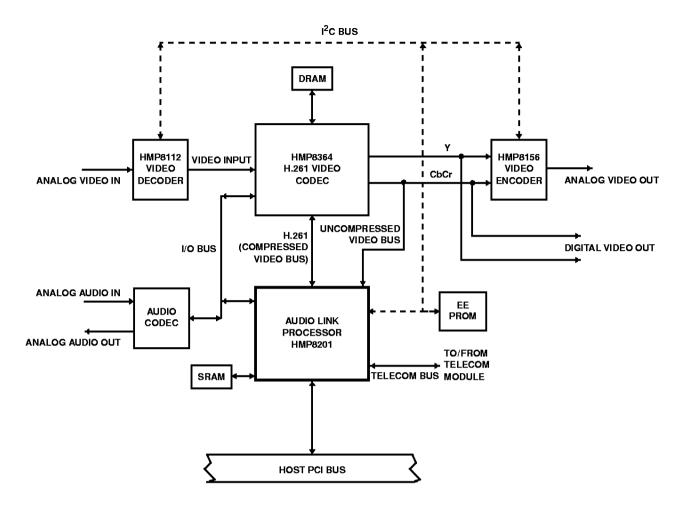

The ALP utilizes digital signal processor (DSP) technology to execute the H.320 audio layer. The audio capabilities include: full duplex implementations of ITU G.711, G.722 and G.728 and acoustic echo cancellation with noise cancellation. The transport layer is an host implementation of ITU H.221, which requires interfaces to the H.261 video compression chip and the telecom communications channel. In addition, the DSP provides host processor communications via the PCI bus and hardware I/O control and data flow functions for external audio codecs.

The ALP also provides PCI bus interface functions to support ITU H.320 implementation. The ALP provides a "gateway" to the PCI bus for the devices used in implementing the video, audio and transport layers of the ITU H.320 standard.

To this end, the ALP supports these PCI bus interfaces: the 8-bit digital video input bus (uncompressed video data), a compressed video bus (H.261), an 8-bit general purpose bus (control and status, compressed H.yyy Annex D data streams, and digital audio), Telecom communication channel time-division multiplexed bus (MVIP or IOM2), the serial I<sup>2</sup>C bus (control and status), and to the on-chip DSP core (host processor communications.

NOTE: This document describes the ALP hardware. In order to function, the hardware is designed to work with host software and downloadable DSP microcode. In some sections of this document, descriptions and statements will imply that the host software and downloadable DSP microcode are an integral part of the ALP subsystem.

FIGURE 1.

### **Audio Compression**

The full duplex implementations of ITU G.711, G.722, and G.728 audio compression run in the embedded Digital Signal Processors (DSPs) in the ALP. Linear audio samples from the audio codec are input through the I/O bus and then subsequently processed. G.711 implements A-Law or u-Law companding which provides a compression ratio of 1.6. G.711 performs a logarithmic quantization on signals with a 4kHz bandwidth falls into the waveform coding class of audio compression techniques. Waveform coders work equally well compressing music or speech. G.722, which is also a form of waveform coding, implements Sub-Band ADPCM which provides a higher compression ratio (3.5) and wider audio bandwidth (8kHz) then G.711. Finally, G.728 implements Low Delay Code Excited Linear Predictive coding (LD-CELP), which is a form of speech coding. Speech coders provide the highest amount of compression on signals that are primarily speech. G.728 provides a compression ratio of 6.5 and outputs a signal with a 4kHz bandwidth.

### Acoustic Echo Cancellation

The ALP implements a proprietary, sub-band based AEC technique that was developed by PictureTel Corp. This technique is similar to PictureTel's Integrated Dynamic Echo Canceller II (IDEC II) technique which has been shown to be superior to other AEC techniques. The AEC algorithm runs on the DSP core in the ALP. The AEC function has two modes of operation, wide and narrow band. It may be selectively disabled by the user (for simplex

communication or in excessively noisy environments). Additionally, noise suppression is included with this AEC algorithm.

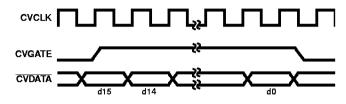

### PCI Interface

The PCI Interface provides a gateway through which video teleconferencing data and control are passed between a host computer and PCMS chip set. The ALP supports little endian transfers and conforms to the PCI 2.1 specification. The PCI Interface provides two sets of register address spaces which are visible on the PCI bus.

The first register set is used to configure the ALP for PCI operation and includes the registers required for plug-and-play compatibility. This conforms to the 256 byte Configuration Space specification as defined in the PCI 2.1 specification. The first 16 bytes of this configuration space represent a universal, read only header whose content is set by ROM on the ALP. User specific vendor information is loaded into the Subsystem registers from an external serial I<sup>2</sup>C EEPROM. Access to this configuration space is generally restricted to the host operating system.

The second register set, which supports doubleword transfers only, is used to provide control, status, and data transfer information associated with the PCMS chip set operation. At boot up, the host allocates a 4096 byte block of PCI register space for this second register set.

In some cases, the host computer performs the data transfer and the ALP acts as a PCI bus target. In other cases, the ALP acts as a PCI master to transfer the data; these are listed below:

As a bus target, the ALP responds to the following types of data transfers:

- I<sup>2</sup>C Master Read data transfer

- I<sup>2</sup>C Master Write data transfer

- · I/O Bus Read and Write transfers

- Mailbox FIFO data transfers with the embedded DSP cores

- Timer Control

As a bus master, the ALP can initiate the following types of data transfer:

- Telecom H.221 transmit data transfer

- · Telecom H.221 receive data transfer

- Uncompressed Video (UCV) receive

- · Compressed Video Local (CVL) transfer

- · Compressed Video Remote(CVR) transfer

- · Compressed Audio Local (CAL) transfer

- · Compressed Audio Remote (CAR) transfer

Further details (such as register details) can be found in the Programming and Applications Reference for the Audio Link Processor.

### Uncompressed Video Interface (UVI)

The ALP provides an Uncompressed Video Interface to receive both the local and remote uncompressed video streams from the Px64 chip. The video frames from each source are interleaved and sent to the ALP at an average rate of 30 frames/sec. This interface also supports still frame capture to implement Annex D mode. The ALP acts as a PCI master to transfer the received video streams to a target GUI/host via the PCI interface.

### Uncompressed Video Bus (UVB)

The ALP provides an Uncompressed Video Bus (UVB) capable of receiving video data from the Px64 chip at a sustained rate of 20.25MBytes/s. Refer to page xx for signal definitions of the UVB. These signals include an 8-bit data bus, UVB[7:0], a vertical sync, VSYNC, a data valid, UVRDY, and a field indicator, FIELD. SYSCLK is used for the bus clock.

A more complete discussion of the UV interface is contained in the HMP8364 data sheet.

### **UVB Transfer Protocol**

The ALP will use the rising edge of SYSCLK to clock in video data when UVRDY is high.

### Data Transfers Between UVB and PCI

The ALP functions as a PCI master to transfer two streams of uncompressed video data received on the UVB to the PCI bus. These transfers are controlled by a block of 32-bit registers in the Video Channel portion of the PCI Control/Status Register block. The ALP provides the following basic

functionality:

- a) UVB FIFO

- b) Four buffer address registers (2 even/2 odd)

- c) Two registers for controlling the gap between video lines (even/odd)

- d) Two registers for controlling the dropping of video fields (even/odd)

- e) Two lines per field counters and controls (even/odd)

- f) Two pixels per line counters and controls (even/odd)

- g) Two RGB Alpha fill registers (even/odd)

- h) Controls for even/odd fields for overflow handling, Alpha mode enable, field capture mode and buffer enable.

- Status for even/odd fields reflecting buffer and FIFO conditions and current buffer transfer state.

- j) Control for the size of PCI Bus block transfers (0 to 64 double words).

### Compressed Video Interface

The ALP provides a Compressed Video Interface through which data is transferred between the Host and the Px64 chip. This interface function converts ALP-Px64 data transfers over the Compressed Video Bus to ALP-Host transfers over the PCI bus, and converts Host-ALP transfers on the PCL bus to ALP-Px64 transfers on the compressed video bus. The ALP acts as master for transfers over both the PCI and Compressed Video Bus.

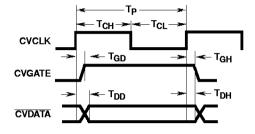

### Compressed Video Bus (CVB)

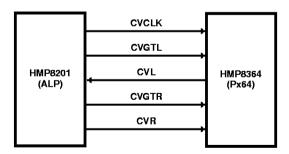

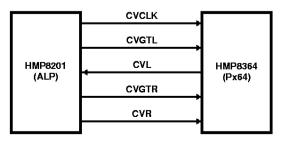

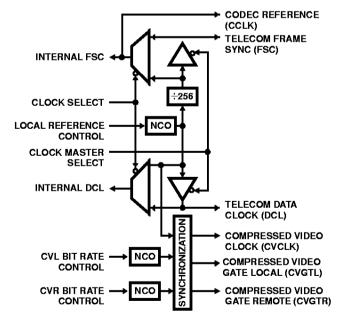

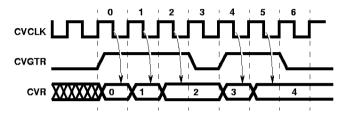

The ALP provides a 5-wire CVB capable of transferring serially at rates up to 384kbits/s. These signals include a serial data clock, CVCLK, remote and local compressed video lines, CVR and CVL, and I/O data gates, CVGTR and CVGTL. The signal interface is depicted in Figure 2.

FIGURE 2. COMPRESSED VIDEO BUS SIGNALS

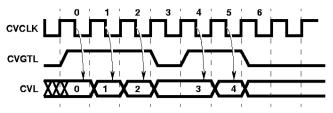

### CVL/CVR Data Transfer Over CVB

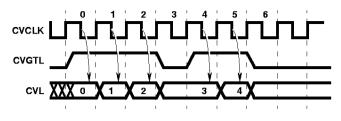

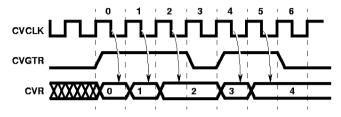

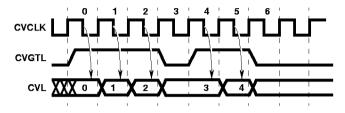

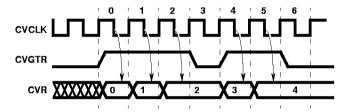

The signaling protocol required to effect a master read compressed video data transfer is shown in Figure 3. The master uses the falling edge of CVCLK to latch in data when CVGTL is high. The corresponding master write is illustrated in Figure 4. The slave uses the falling edge of CVCLK to latch in data when CVGTR is high.

FIGURE 3. CVB MASTER READ

FIGURE 4. CVB MASTER WRITE

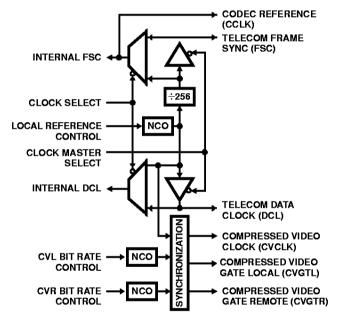

The source for the compressed video clock, CVCLK, is the Local Reference NCO. The CVCLK frequency is typically 2.048MHz. The gating signals are generated by the carry out of programmable NCOs. The gating signal frequency is set by loading the CVL and CVR Bit Rate Control Registers (see Section 3.1.2.7.3). The bit rate across the CVB is determined by the frequency with which the gating signals are asserted, and it is bounded at the upper end by the frequency of CVCLK (2.048MHz). Figure 5 depicts how the audio codec reference and Telecom signals are created and selected. Note: the gating signals are asserted synchronous with CVCLK.

The number of bits allocated to video in the H.221 multi frame sets the required bit rate over the CVB. Since the number of bits allocated to video in the H.221 frame can be variable over the course of a call, the host will update the Bit Rate Control registers to match changing bandwidth allocations for video in either the local or remote direction. The Px64 adapts compression to changes in bit rate based on the flow of data to and from its internal CVL and CVR buffers.

### CVL/CVR Data Transfer Over PCI

The ALP acts as a PCI master to read CVR data and write CVL data to ping-pong buffers using a protocol similar to that used for CAR and CAL data. The CVR transfers are controlled by a PCI based register set that mirrors the CAR registers in functionary. Similarly, the CVL transfers are controlled by a registers that mirrors the CAL registers.

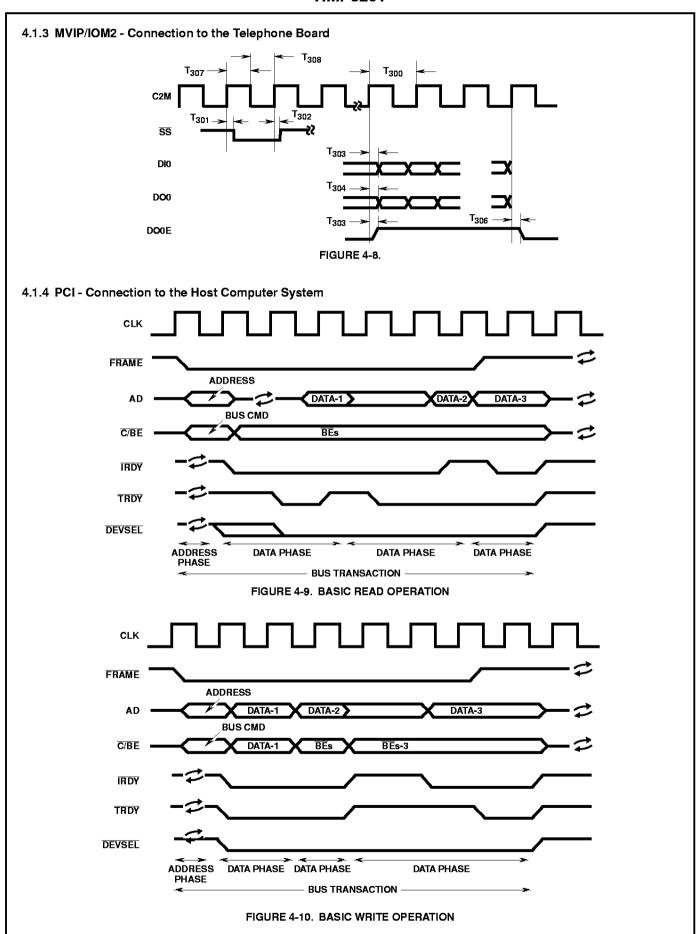

### Telecom Interface and Signals

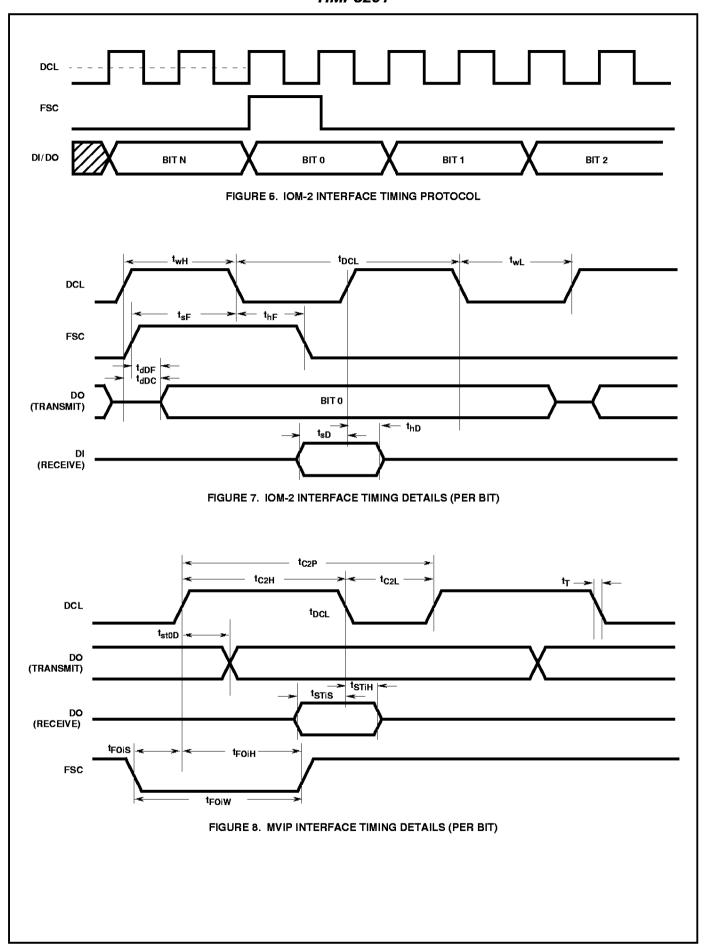

The ALP provides a five-wire Telecom interface through which H.221 data transfers occur with the system ISDN modem. This interface is compatible with ISDN modems using either a MVIP (Multi Vendor Integration Protocol) in the US or IOM-2 type interface (this consists of the combination of the GCI line card interface standard and the Special Circuit Interface T standard) in Europe and elsewhere.

The local and remote H.221 data streams are transferred directly through this interface from/to the host PCI bus. The maximum sustainable data rate through this interface is 128kbits/s.

This interface consists of the five signal lines which include a serial data clock (DCL) which runs at twice the data rate, a serial data input (DI), a serial data out put (DO), a frame sync (FSC) which runs at 8kHz, and an output data enable (ODE). The ALP sources the frame sync and data clock signals and switch the interpretation of the data in and out signals.

The ALP uses the an MVIP/IOM2 signaling convention to transfer data over the Telecom interface; it is capable of mastering the Telecom bus and functions as a PCI master to transfer H.221 data to and from the Telecom Interface. Configuration of the Telecom Interface may be done through its PCI based control register (see Section xx).

The ALP sources the frame sync and data clock signals and switch the interpretation of the data in and out signals.

FIGURE 5. TELECOM, COMPRESSED VIDEO AND AUDIO REFERENCE CLOCK AND CONTROL

# PC Bus Interface

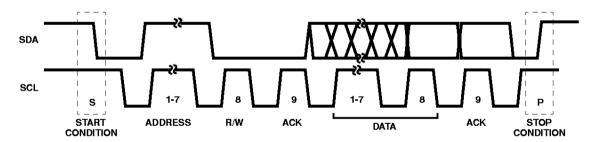

The ALP provides an I<sup>2</sup>C interface to communicate with peripheral devices such as the NTSC/PAL Encoder IC (HMP8112), the NTSC/PAL Decoder IC (HMP8115), a serial EPROM (used to upload PCI Interface configuration data), and any additional peripheral I<sup>2</sup>C slave devices. I<sup>2</sup>C is a two wire interface consisting of a serial clock line (SCL), and a serial data line (SDA) that can run up to up to 100 KBPS as specified in the inter-integrated circuit interface from Philips Semiconductor. The ALP only functions as an I<sup>2</sup>C Bus Master. As a result, the ALP can only be connected to I<sup>2</sup>C slave devices without bus contention.

### PCI Configuration Via I<sup>2</sup>C EEPROM

The ALP uploads the vendor specific information required for PCI interface configuration from an I<sup>2</sup>C compatible serial EEPROM. The required information is 32 bits in length and represents the Subsystem Vendor ID and Subsystem ID. The ALP will read this information and load it into address 10<sub>16</sub> of PCI Configuration Space (see section xx). The ALP reads the serial EEPROM and initializes the PCI Configuration Space after system reset.

### I<sup>2</sup>C EEPROM Address

The 8-bit slave address and broadcast on the I<sup>2</sup>C bus for EEPROM read and write operations is given in Table 1. Refer to EEPROM data sheets for more information.

TABLE 1.

| OPERATION | DPERATION DEVICE ID |     | R/W BIT |  |

|-----------|---------------------|-----|---------|--|

| Read      | 10 <sub>16</sub>    | xxx | 1       |  |

| Write     | 10 <sub>16</sub>    | xxx | 0       |  |

### Data Transfers Between I<sup>2</sup>C and PCI

Data transfers between the PCI and the ALP's I<sup>2</sup>C bus are controlled by two PCI based I<sup>2</sup>C control registers (refer to the programming/register reference). All I<sup>2</sup>C operations are initiated when bit 24 of address 10<sub>16</sub> is updated. The ALP will perform an I<sup>2</sup>C master read or write depending on the

value written to bit 23 of address 10<sub>16</sub>. After completion of the I/O cycle, the appropriate status bits will be set.

For a detailed timing description on the I<sup>2</sup>C bus, please refer to the Philips I<sup>2</sup>C Specification.

# I<sup>2</sup>C Control Interface

The I<sup>2</sup>C clock/data timing is shown in Figure 9. The HMP8112 contains 29 internal registers used to program and configure the Decoder. The I<sup>2</sup>C control port contains a pointer register that auto-increments through the entire register space and can be written. The autoincrement pointer will wrap after the last register has been accessed (Product ID Register) and should be set to the desired starting address each time an access is started. For a write transfer, the I<sup>2</sup>C device base address is the first part of a serial transfer. Then the internal register pointer is loaded. Then a series of registers can be written. If multiple registers are written, the pointer register will autoincrement up through the register address space. A stop cycle is used to end the transfer after the desired number of registers are programmed.

For a read transfer, the I<sup>2</sup>C device address is the first part of the serial transfer. Then the internal register pointer is loaded. At this point another start cycle is initiated to access the individual registers. Multiple registers can be read and the pointer register will autoincrement up through the pointer register address space. On the last data read, an acknowledge should not be issued. A stop cycle is used to end the transfer after the desired number of registers are read.

FIGURE 9. I<sup>2</sup>C SERIAL TIMING FLOW

# Pin Description

| NAME                                                                                            | PQFP PIN<br>NUMBER             | INPUT/<br>OUTPUT | DESCRIPTION                                                                                                                                                                             |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PCI INTERF                                                                                      | ACE (50 Pins, 4 In, 2          | 2 Out, 44 I/O)   |                                                                                                                                                                                         |  |  |

| AD[31:0] 208, 1-4, 7-9, I/O<br>14-16, 19-22, 25,<br>40, 43-46, 49-51,<br>53-54, 57-60,<br>63-64 |                                | I/O              | PCI Address/Data Bus. Address and Data are multiplexed over this bus. A bus transaconsists of an address transfer followed by one or more data transfers. (Three-Stat pins)             |  |  |

| CBE[3:0]                                                                                        | 10, 26, 39, 52                 | 1/0              | Bus Command/Byte Enable. Defines bus command during address transfer. Defines which byte lanes are valid during data transfers. (Three-State I/O pins)                                  |  |  |

| PAR                                                                                             | 38                             | I/O              | Parity. Set for even parity across AD[31:0] and CBE[3:0]. The bus master sets PAR during address and write data phases. Target sets PAR during read data phases. (Three-State I/C pins) |  |  |

| FRAME                                                                                           | 27                             | I/O              | Frame. This active low signal is asserted by the current bus master to indicate the beginning and duration of a bus transaction. (Sustained Three-State pin)                            |  |  |

| TRDY                                                                                            | 31                             | I/O              | Target Ready. This active low signal indicates the target device's ability to complete the data phase of the transaction. (Sustained Three-State pin)                                   |  |  |

| IRDY                                                                                            | 28                             | I/O              | Initiator Ready. This active low signal indicates the Initiator's ability to complete the current data phase of the transaction. (Sustained Three-State pin)                            |  |  |

| STOP                                                                                            | 33                             | I/O              | Stop. The current target asserts this signal low to stop the current transaction. (Sustained Three-State pin)                                                                           |  |  |

| ĪNTĀ                                                                                            | 201                            | 0                | Interrupt A. This active low PCI interrupt stays asserted until serviced by host.                                                                                                       |  |  |

| IDSEL                                                                                           | 13                             | I                | Initialization Device Select. Used as a chip select during configuration read and write transactions.                                                                                   |  |  |

| DEVSEL                                                                                          | 32                             | I/O              | Device Select. Asserted by a device recognizing its address as the target of an access (Sustained Three-State pin)                                                                      |  |  |

| PERR                                                                                            | 34                             | I/O              | Parity Error. Indicates data parity errors during all PCI transactions except a Special Cycle (Sustained Three-State pin)                                                               |  |  |

| SERR                                                                                            | 37                             | I/O              | System Error. Indicates address parity errors, data parity errors during Special Cycle command, or any other system error where the result will be catastrophic                         |  |  |

| REQ                                                                                             | 207                            | 0                | Request. Indicates to arbiter that this agent desires use of the bus. Point to point signal (Three-State)                                                                               |  |  |

| GNT                                                                                             | 206                            | I                | Grant. Indicates to the agent that access to the bus has been granted. (Three-State)                                                                                                    |  |  |

| PCICLK                                                                                          | 204                            | I                | Clock. This is the PCI clock input to every device. Every signal but RST, are sampled on the rising edge of CLK.                                                                        |  |  |

| RST                                                                                             | 202                            | I                | Reset.                                                                                                                                                                                  |  |  |

| I <sup>2</sup> C INTERF                                                                         | ACE (2 Pins, 1 Out,            | 1 I/O)           |                                                                                                                                                                                         |  |  |

| SCL                                                                                             | 147                            | 0                | I <sup>2</sup> C Serial Clock                                                                                                                                                           |  |  |

| SDA                                                                                             | 148                            | I/O              | I <sup>2</sup> C Serial Data                                                                                                                                                            |  |  |

| I/O BUS (IO                                                                                     | <b>B)</b> , (27 Pins, 9 IN, 10 | Out, 8 I/O)      |                                                                                                                                                                                         |  |  |

| IOD[7:0]                                                                                        | 197-193, 190-188               | I/O              | I/O Data Bus. Bidirectional data bus. (Three-State)                                                                                                                                     |  |  |

| IOA[1:0]                                                                                        | 164, 167                       | 0                | Programmed I/O addresses[1:0]                                                                                                                                                           |  |  |

| IOA[3:2]                                                                                        | 162-163                        | 0                | Spare address signals.                                                                                                                                                                  |  |  |

# Pin Description (Continued)

| NAME      | PQFP PIN<br>NUMBER | INPUT/<br>OUTPUT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-----------|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VC_CS     | 159                | 0                | Px64 Chip Select. This active low output signals the Px64 to respond to I/O Bus commands This signal also maps to IOA[4].                                                                                                                                                                                                                             |  |  |  |

| CCS       | 158 O              |                  | Audio Codec Chip Select. This active low output signals the audio codec to respond to 1/0 Bus commands. This signal also maps to IOA[5].                                                                                                                                                                                                              |  |  |  |

| CDAK      | 157                | 0                | Audio Codec Capture Acknowledge. This active low output signals that the next read cyclis a DMA read from the capture FIFO. This signal also maps to IOA[6].                                                                                                                                                                                          |  |  |  |

| PDAK      | 152                | 0                | Audio codec Playback Acknowledge. This active low output signals that the next write cyclis a DMA write to the playback FIFO. This signal also maps to IOA[7].                                                                                                                                                                                        |  |  |  |

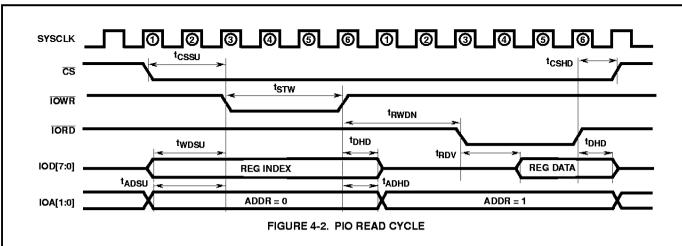

| ĪORD      | 181                | 0                | I/O Read Strobe. This active low output defines an I/O Bus read cycle.                                                                                                                                                                                                                                                                                |  |  |  |

| ĪOWR      | 185                | 0                | I/O Write Strobe. This active low output defines an I/O Bus write cycle.                                                                                                                                                                                                                                                                              |  |  |  |

| IOWAIT    | 186                | I                | I/O Wait. The target can extend the read or write by driving this input low after the assertion of either IOWR or IORD. (Three-State).                                                                                                                                                                                                                |  |  |  |

| IOINT     | 187                | I                | I/O Bus Interrupt. Asserted by other components on IOB to initiate a PCI interrupt. Not open drain input; external pull up required.                                                                                                                                                                                                                  |  |  |  |

| IORQ[3:0] | 175-176, 179-180   | I                | Spare request signals (active high).                                                                                                                                                                                                                                                                                                                  |  |  |  |

| ADRQ      | 174                | I                | Px64 Data Request. This active high input signals that the Px64 chip requires an Annex data transfer. This signal also maps to IORQ4.                                                                                                                                                                                                                 |  |  |  |

| CDRQ      | 169                | I                | Audio codec Capture Request. This active high input signals that the audio codec has a least one sample captured. This signal also maps to IORQ5.                                                                                                                                                                                                     |  |  |  |

| PDRQ      | 168                | I                | Audio codec Playback Request. This active high input signals that the audio codec ha room for at least one playback sample. This signal also maps to IORQ6.                                                                                                                                                                                           |  |  |  |

| TELECOM I | NTERFACE (5 Pins,  | 1 In, 2 Out,     | 2 I/O)                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DI        | 146                | I                | Serial Data Input. Serial data input from ISDN Modern. Synchronous to DCL.                                                                                                                                                                                                                                                                            |  |  |  |

| DO        | 142                | 0                | Serial Data Output. Serial data output to ISDN Modem. Synchronous to DCL.                                                                                                                                                                                                                                                                             |  |  |  |

| DCL       | 140                | 1/0              | Serial Data Clock. In systems using the MVIP interface this line would be tied to the C2 or put which is a 2.048MHz clock synchronous to the bit rate. In systems using the IOM-2 medem interface, this signal would be tied to the DCL output which is synchronous to twice the bit rate, and is programmable in 64kHz steps from 512kHz to 4096kHz. |  |  |  |

| FSC       | 141                | I/O              | Frame Sync. This signal is an 8kHz sync indicating the start of a frame. Normally, this generated by upstream device (tel-co). For test purposes, this sync may be locally generated and output from the ALP. This signal also serves as the audio sample rate reference the audio codec.                                                             |  |  |  |

| DOE       | 143                | 0                | Data Output Enable. This active low output is asserted during an outgoing data transmi sion.                                                                                                                                                                                                                                                          |  |  |  |

| COMPRESS  | SED VIDEO BUS (5   | Pins, 1 In, 4 (  | Dut, 0 I/O)                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| CVCLK     | 116                | 0                | Compressed Video Clock.                                                                                                                                                                                                                                                                                                                               |  |  |  |

| CVGTL     | 118                | 0                | Compressed Video Gate Local. This active high signal enables CVCLK to clock conpressed video bits out of the Px64 chip.                                                                                                                                                                                                                               |  |  |  |

| CVL       | 121                | I                | Compressed Video Local. This is the serial input for compressed video. The bit value at this input is sampled by the falling edge of CVCLK when CVGTL is asserted.                                                                                                                                                                                    |  |  |  |

| CVGTR     | 119                | 0                | Compressed Video Gate Remote. This active high signal is asserted simultaneously wid ata bits clocked out of CVR by CVCLK.                                                                                                                                                                                                                            |  |  |  |

# Pin Description (Continued)

| NAME                       | PQFP PIN<br>NUMBER                            | INPUT/<br>OUTPUT | DESCRIPTION                                                                                                                                                                                                                     |  |  |  |  |

|----------------------------|-----------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CVR 120 O                  |                                               | 0                | Compressed Video Remote. Compressed video data is serially clocked through this output at the rising edge of CVCLK.                                                                                                             |  |  |  |  |

| UNCOMPRE                   | SSED VIDEO BUS                                | (11 Pins, 11 I   | n, 0 Out, 0 I/O)                                                                                                                                                                                                                |  |  |  |  |

| UV[7:0] 124-127, 130-133 I |                                               | I                | Uncompressed Video. Uncompressed video from H.261 processor. Data on this bus is clocked into the ALP by the rising edge of SYSCLK when UVRDY is asserted.                                                                      |  |  |  |  |

| VSYNC                      | 134                                           | I                | Vertical Sync. This signal indicates the beginning of a new video field.                                                                                                                                                        |  |  |  |  |

| UVRDY                      | 137                                           | I                | Uncompressed Video Ready. This active high input indicates that data present on UV[7:0] is valid.                                                                                                                               |  |  |  |  |

| FIELD                      | 138                                           | I                | Video Field. The sense of this signal indicates whether an even or odd video field is currently being transferred (0 = even, 1 = odd). The state of this input is held constant through out the duration of the field transfer. |  |  |  |  |

| MISCELLAN                  | IEOUS (9 Pins, 6 In,                          | 3 Out, 0 I/O)    |                                                                                                                                                                                                                                 |  |  |  |  |

| SYSCLK                     | 139                                           | I                | CLOCK. Video teleconferencing system clock. Typically 27MHz.                                                                                                                                                                    |  |  |  |  |

| SYSRST                     | 151                                           | 0                | Reset. This active low output echoes a PCI reset.                                                                                                                                                                               |  |  |  |  |

| CLKOUT                     | 183                                           | 0                | DSP Processor clock. 40.5MHz output of PLL.                                                                                                                                                                                     |  |  |  |  |

| PLLBPCLK                   | 155                                           | I                | External Test Clock Input.                                                                                                                                                                                                      |  |  |  |  |

| CCLK                       | 199                                           | 0                | Codec clock. Audio reference (8kHz).                                                                                                                                                                                            |  |  |  |  |

| TMOD[1:0]                  | 149-150                                       | I                | Test Mode. Selects one of three test modes. "00" = normal operation; "02" = PLL bypass.                                                                                                                                         |  |  |  |  |

| LOAD                       | 153                                           | I                | Boot Select. 0 loads from host, 1 loads from CDI.                                                                                                                                                                               |  |  |  |  |

| LFA                        | 172                                           | I                | Loop Filter Input. This pin is tied to ground via lump components required to control PLL Loop Filter bandwidth.                                                                                                                |  |  |  |  |

| SRAM INTE                  | RFACE (35 Pins, 0                             | ln, 19 Out, 16   | 1/0)                                                                                                                                                                                                                            |  |  |  |  |

| SD[15:0]                   | 78-79, 82-86,<br>89-93, 96-99                 |                  | SRAM Data Bus. Bidirectional data bus.                                                                                                                                                                                          |  |  |  |  |

| SA[16:0]                   | 101, 76-75, 72-68,<br>65, 105-107,<br>110-114 |                  | SRAM Address Bus. Note: SA16 allows paging of 128 kwords of external RAM, which is not required by the current firmware.                                                                                                        |  |  |  |  |

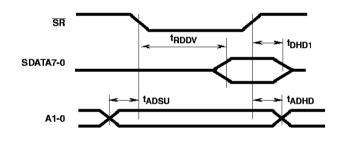

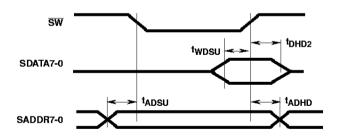

| SRD                        | 100                                           |                  | SRAM Read Strobe. This active low output defines an SRAM read cycle.                                                                                                                                                            |  |  |  |  |

| SWR                        | 77                                            |                  | SRAM Write Strobe. This active low output defines an SRAM write cycle.                                                                                                                                                          |  |  |  |  |

| SUPPLY (63                 | Pins, 31 V <sub>CC</sub> , 30 G               | ND)              |                                                                                                                                                                                                                                 |  |  |  |  |

| V <sub>CC</sub>            |                                               | I                | 3.3V Digital Supply.                                                                                                                                                                                                            |  |  |  |  |

| V <sub>CC</sub> A          |                                               | I                | 3.3V Analog Supply for PLL circuit.                                                                                                                                                                                             |  |  |  |  |

| GND                        |                                               | 0                | Digital Ground.                                                                                                                                                                                                                 |  |  |  |  |

| GNDA                       |                                               | 0                | Analog Ground for PLL circuit.                                                                                                                                                                                                  |  |  |  |  |

# Absolute Maximum RatingsThermal InformationDigital Supply Voltage (V<sub>CC</sub> to DGND).4.0VDigital Input VoltagesGND -0.5V to V<sub>CC</sub> 0.5VPQFP Package32ESD ClassificationClass 1Maximum Storage Temperature Range.65°C to 150°COperating Temperature RangeMaximum Lead Temperature (Soldering 10s).300°CHMP8201CN0°C to 70°C(Lead Tips Only)

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTE:

1. θ<sub>JA</sub> is measured with the component mounted on an evaluation PC board in free air. Dissipation rating assumes device is mounted with all leads soldered to printed circuit board

**Electrical Specifications**  $V_{CC} = 3.3V \pm 9\%$ ,  $T_A = 25^{\circ}C$ , Unless Otherwise Specified

|                              |                                     |                                                                                                                                    |                               | HMP8201 |                              |       |  |

|------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------|------------------------------|-------|--|

| PARAMETER                    | SYMBOL                              | TEST CONDITIONS                                                                                                                    | MIN                           | TYP     | MAX                          | UNITS |  |

| POWER SUPPLY CHARACTERIST    | rics                                |                                                                                                                                    |                               |         |                              |       |  |

| Power Supply Voltage Range   | DV <sub>CC</sub> , AV <sub>CC</sub> | Note 2                                                                                                                             | 3.00                          | 3.30    | 3.60                         | ٧     |  |

| Power Supply Current         | Digital I <sub>CCOP</sub>           | f <sub>SYSCLK</sub> = 27MHz,<br>f <sub>PCICLK</sub> = 33MHz,<br>DV <sub>CC</sub> = 3.60V,<br>Outputs Not Loaded                    | -                             | XXX     | xxx                          | mA    |  |

|                              | Analog I <sub>CAOP</sub>            | f <sub>SYSCLK</sub> = 27MHz,<br>AV <sub>CC</sub> = 3.60V                                                                           | -                             | XX      | XX                           | mA    |  |

| Total Power Dissipation      | Ртот                                | f <sub>SYSCLK</sub> = 27MHz,<br>f <sub>PCICLK</sub> = 33MHz,<br>DV <sub>CC</sub> = AV <sub>CC</sub> = 3.60V,<br>Outputs Not Loaded | -                             | X.XX    | X.XX                         | W     |  |

| DIGITAL I/O                  |                                     | -                                                                                                                                  |                               |         |                              |       |  |

| Input Logic High Voltage     | V <sub>IH</sub>                     | DV <sub>CC</sub> = Max                                                                                                             | 0.7xV <sub>CC</sub><br>(2.52) | -       | -                            | ٧     |  |

| Input Logic Low Voltage      | V <sub>IL</sub>                     | DV <sub>CC</sub> = Min                                                                                                             | -                             | -       | 0.3xV <sub>CC</sub><br>(0.9) | V     |  |

| Input Leakage Current (High) | lін                                 | DV <sub>CC</sub> = Max, Input = DV <sub>CC</sub><br>Note 4                                                                         | -10                           | -       | 10                           | μА    |  |

| Input Leakage Current (Low)  | I <sub>IL</sub>                     | DV <sub>CC</sub> = Max, Input = 0V<br>Note 4                                                                                       | -10                           | -       | 10                           | μА    |  |

| Input/Output Capacitance     | C <sub>IN</sub>                     | CLK Frequency = 1 MHz,<br>Note 2, All Measurements<br>Referenced to Ground T <sub>A</sub> = 25°C                                   | -                             | -       | 10                           | pF    |  |

| Rise/Fall Time               | t <sub>r</sub> , t <sub>f</sub>     | Note 2                                                                                                                             | -                             | -       | 2.0                          | ns    |  |

| Output Logic High Voltage    | V <sub>OH</sub>                     | I <sub>OH</sub> = -400μA, DV <sub>CC</sub> = Max                                                                                   | V <sub>CC</sub><br>- 0.4      | ı       | -                            | V     |  |

| Output Logic Low Voltage     | V <sub>OL</sub>                     | I <sub>OL</sub> = 800μA, DV <sub>CC</sub> = Min                                                                                    |                               | -       | 0.4V                         | ٧     |  |

# **Electrical Specifications** $V_{CC}$ = 3.3V $\pm 9\%$ , $T_A$ = 25°C, Unless Otherwise Specified (Continued)

|                                                |                                   |                                                                                                   | HMP8201             |      |                      |       |

|------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------|---------------------|------|----------------------|-------|

| PARAMETER                                      | SYMBOL                            | TEST CONDITIONS                                                                                   | MIN                 | TYP  | MAX                  | UNITS |

| PCI DIGITAL I/O                                |                                   | •                                                                                                 |                     |      |                      |       |

| PCI Bus Clock Frequency                        | CLK                               | Note 2                                                                                            | 0                   | 33   | 33                   | MHz   |

| Clock Cycle Time                               | CLK                               | 7                                                                                                 | 30                  | -    | -                    | ns    |

| Clock Waveform Symmetry                        |                                   | 7                                                                                                 | 40                  | -    | 60                   | %     |

| Clock Pulse Width High                         | t <sub>PWH</sub>                  | 7                                                                                                 | 12                  | -    | -                    | ns    |

| Clock Pulse Width Low                          | t <sub>PWL</sub>                  | 1                                                                                                 | 12                  | -    | -                    | ns    |

| Input Logic High Voltage                       | V <sub>IH</sub>                   | DV <sub>CC</sub> = Max                                                                            | 0.5*V <sub>CC</sub> | -    | V <sub>CC</sub> +0.5 | ٧     |

| Input Logic Low Voltage                        | V <sub>IL</sub>                   | DV <sub>CC</sub> = Min                                                                            | -0.5                | -    | 0.3xV <sub>CC</sub>  | ٧     |

| Input Leakage Current (High)                   | l <sub>IH</sub>                   | DV <sub>CC</sub> = Max, Input = DV <sub>CC</sub><br>Note 2                                        | -10                 | -    | 10                   | μΑ    |

| Input Leakage Current (Low)                    | IIL                               | DV <sub>CC</sub> = Max, Input = 0V<br>Note 2                                                      | -10                 | -    | 10                   | μΑ    |

| Input/Output Capacitance                       | C <sub>IN</sub>                   | CLK Frequency = 1MHz,<br>All Measurements Referenced to<br>Ground T <sub>A</sub> = 25°C           | -                   | 8-10 | -                    | pF    |

| Rise/Fall Time                                 | t <sub>r</sub> , t <sub>f</sub>   | Note 2                                                                                            | -                   | -    | 2.0                  | ns    |

| Output Logic High Voltage                      | V <sub>OH</sub>                   | I <sub>OH</sub> = -500μA, DV <sub>CC</sub> = Max                                                  | 0.9xV <sub>CC</sub> | -    | -                    | ٧     |

| Output Logic Low Voltage                       | V <sub>OL</sub>                   | I <sub>OL</sub> = 1.5mA, DV <sub>CC</sub> = Min                                                   | 0                   | -    | 0.1xV <sub>CC</sub>  | ٧     |

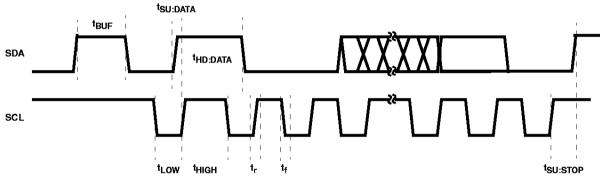

| I <sup>2</sup> C DIGITAL I/O (SDA, SCL, Fast M | ode)                              |                                                                                                   |                     |      |                      |       |

| Input Logic High Voltage                       | V <sub>IH</sub>                   | DV <sub>CC</sub> = Max                                                                            | 0.7xV <sub>CC</sub> | -    | -                    | ٧     |

| Input Logic Low Voltage                        | V <sub>IL</sub>                   | DV <sub>CC</sub> = Min                                                                            | -                   | -    | 0.3xV <sub>CC</sub>  | ٧     |

| Input Logic Current                            | I <sub>IH</sub> , I <sub>IL</sub> | DV <sub>CC</sub> = Max<br>Input = 0V or 3.3V                                                      | -10                 | -    | 10                   | μΑ    |

| Input/Output Capacitance                       | C <sub>IN</sub>                   | CLK Frequency = 400kHz,<br>Note 2, All Measurements<br>Referenced to GND<br>T <sub>A</sub> = 25°C | -                   |      | 8                    | pF    |

| Output Logic High Voltage                      | V <sub>OH</sub>                   | I <sub>OH</sub> = -1mA, DV <sub>CC</sub> = Max                                                    | 0.9xV <sub>CC</sub> | -    | -                    | ٧     |

| Output Logic Low Voltage                       | V <sub>OL</sub>                   | I <sub>OL</sub> = 3mA, DV <sub>CC</sub> = Min                                                     | 0                   | -    | 0.1xV <sub>CC</sub>  | ٧     |

| SCL Clock Frequency                            | fscl                              | Note 2                                                                                            | 0                   | -    | 100                  | kHz   |

| SCL Minimum Low Pulse Width                    | t <sub>LOW</sub>                  |                                                                                                   | 4.7                 | -    | -                    | μs    |

| SCL Minimum High Pulse Width                   | thigh                             |                                                                                                   | 4.0                 | -    | -                    | μs    |

| Data Hold Time                                 | thd:data                          |                                                                                                   | 0                   | -    | -                    | ns    |

| Data Setup Time                                | t <sub>SU:DATA</sub>              |                                                                                                   | 250                 | -    | -                    | ns    |

| Rise Time                                      | t <sub>r</sub>                    | Note 2                                                                                            | -                   | -    | 1000                 | ns    |

| Fall Time                                      | t <sub>f</sub>                    | 7                                                                                                 | -                   | -    | 300                  | ns    |

### Electrical Specifications $V_{CC} = 3.3V \pm 9\%$ , $T_A = 25^{\circ}C$ , Unless Otherwise Specified (Continued)

|                        |                   |                 | HMP8201 |     |     |       |  |  |

|------------------------|-------------------|-----------------|---------|-----|-----|-------|--|--|

| PARAMETER              | SYMBOL            | TEST CONDITIONS | MIN     | TYP | MAX | UNITS |  |  |

| TIMING CHARACTERISTICS |                   |                 |         |     |     |       |  |  |

| Data Setup Time        | t <sub>SU</sub>   | Notes 2, 3      | 10      | -   | -   | ns    |  |  |

| Data Hold Time         | t <sub>HD</sub>   |                 | 0       | -   | -   | ns    |  |  |

| Clock to Out           | t <sub>DVLD</sub> |                 | -       | -   | 8.0 | ns    |  |  |

### NOTES:

- 2. Guaranteed by design or characterization.

- 3. Test performed with C<sub>L</sub> = 40pF, I<sub>OL</sub> = 3mA, I<sub>OH</sub> = -1mA. Input reference level is 1.5V for all inputs. V<sub>IH</sub> = 3.0V, V<sub>IL</sub> = 0V.

- 4. Input leakage current includes hi-Z output leakage for all bidirectional/Three-State outputs.

# **Timing Waveforms**

FIGURE 10. TIMING DIAGRAM

### PCB Layout Considerations

A PCB board with a minimum of 4 layers is recommended, with layers 1 and 4 (top and bottom) for signals and layers 2 and 3 for power and ground. The PCB layout should implement the lowest possible noise on the power and ground planes by providing excellent decoupling. PCB trace lengths between groups of  $V_{CC}$  and GND pins should be as short as possible.

The optimum layout places the HMP8201 as close as possible to the PCI connector.

### **Component Placement**

External components should be positioned as close as possible to the appropriate pin, ideally such that traces can be connected point to point. Chip capacitors are recommended where possible, with radial lead ceramic capacitors the second-best choice.

Power supply decoupling should be done using a  $0.1\mu F$  ceramic capacitor in parallel with a  $0.01\mu F$  chip capacitor for each group of  $V_{CC}$  pins to ground. These capacitors should be located as close to the  $V_{CC}$  and GND pins as possible, using short, wide traces.

### **Ground Plane**

A common ground plane for all devices, including the HMP8201, is recommended. All GND pins on the HMP8201 must be connected to the ground plane.

### **Power Planes**

All  $V_{CC}$  pins on the HMP8201 must be connected to the power plane.

### **Analog Signals**

Traces containing digital signals should not be routed over, under, or adjacent to the analog output traces to minimize crosstalk. If this is not possible, coupling can be minimized by routing the digital signals at a 90 degree angle to the analog signals. The analog output traces should also not overlay the HMP8201 and  $V_{CC}$  power planes to maximize high-frequency power supply rejection.

# 1.0 Data Flows

| DATA FLOW                                   | ACRONYM | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|---------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Local Scaled<br>Uncompressed Video          | LSUV    | LSUV is generated by the Px64 IC to provide video for local display. The LSUV is received as 8-bit SIF (CIF, QCIF?) video at 20.25Mbytes/s for transmission over the PCI bus to the graphics accelerator. Local video is always at field rates or field interleaved with RSUV.                             |

| Remote Scaled<br>Uncompressed Video         | RSUV    | RSUV is generated by the Px64 IC to provide video for remote display. The RSUV is received as 8-bit SIF (CIF, QCIF?) video at 20.25Mbytes/s for transmission over the PCI bus to the graphics accelerator. Remote video is always at frame rates or field interleaved with LSUV.                           |

| Local Uncompressed Still<br>Frame Image     | LUSFI   | LUSFI is generated by the Px64 to support an "Annex D" image. This is a special transfer to the host component memory and can consist of a single SIF (CIF, QCIF?) image or a sequence of 4 SIF (CIF, QCIF?) images.                                                                                       |

| Compressed Video Local                      | CVL     | CVL is a serial bit stream generated by the Px64 IC to transmit H.261 compressed video to the host component.                                                                                                                                                                                              |

| Local Compressed Still Frame Image          | LCSFI   | The LCSFI is generated by the Host Component software from the LUSFI. It consists of one or 4 compressed CIF frames of "Annex D" still video which are transmitted to the H.261 IC via the PCI bus and the ALP IC I/O Bus. The H.261 IC then inserts this compressed video in its outgoing CVL to the ALP. |

| Remote Compressed Still<br>Frame Image      | RCSFI   | The Px64 extracts 1 or 4 CIF frames of compressed Annex D still frame images from the H.261 data stream to ship to the host for decompressing. The data is shipped <i>via</i> the I/O Bus to the ALP and then <i>via</i> the PCI Bus to the host.                                                          |

| Compressed<br>Video Remote                  | CVR     | CVR is a serial bit stream from the ALP IC to the H.261 IC which is fully compliant with the requirements of H.261 for the compressed video bit stream. This bit stream is extracted from the received H.221 stream within the ALP IC and then transmitted via a serial bus to the H.261 IC.               |

| Digital Capture Audio                       | DCA     | DCA is sampled locally to feed to audio processing for transmission to the remote end.                                                                                                                                                                                                                     |

| Digital Playback Audio                      | DPA     | DPA is decompressed audio from the remote end to be played locally.                                                                                                                                                                                                                                        |

| Compressed Audio Local                      | CAL     | CAL is the digitally compressed version of the local audio stream. It is routed to the host via the PCI bus for inclusion in the H.221 data stream.                                                                                                                                                        |

| Compressed Audio<br>Remote                  | CAR     | CAR is the compressed audio stream from the remote end. It is extracted from the H.221 stream by the host and sent to audio processing section of the ALP via the PCI Bus.                                                                                                                                 |

| Local Multiplexed Video<br>Audio User Data  | LVAU    | Local teleconferencing (H.221) data from the host to the Telecom interface.                                                                                                                                                                                                                                |

| Remote Multiplexed<br>Video Audio User Data | RVAU    | Remote teleconferencing (H.221) data from the Telecom interface to the host.                                                                                                                                                                                                                               |

### 1.1 Control Flows

| DATA FLOW                                  | ACRONYM | DESCRIPTION                                                           |

|--------------------------------------------|---------|-----------------------------------------------------------------------|

| Ntsc/pal Decoder Command                   | NPDC    | Command issued to the NTSC/PAL Decoder.                               |

| Ntsc/pal Decoder Response                  | NPDR    | Command response received from the NTSC/PAL Decoder.                  |

| Ntsc/pal Encoder Command                   | NPEC    | Command issued to the NTSC/PAL Encoder.                               |

| Ntsc/pal Encoder Response                  | NPER    | Command response received from the NTSC/PAL Encoder.                  |

| Px64 Processor Command                     | PPC     | Command issued to the Px64 IC.                                        |

| Px64 Processor Response                    | PPR     | Command response received from the Px64 IC.                           |

| Audio Codec Command                        | ACC     | Command issued to the Audio CODEC.                                    |

| Audio Codec Response                       | ACR     | Command response received from the Audio CODEC.                       |

| Telecommunications Device Command          | TDC     | Command issued to the Telecommunications Device.                      |

| Telecommunications Device Response         | TDR     | Command response received from the Telecommunications Device.         |

| Bus Interface And Audio Processor Command  | ALPC    | Command issued to the Bus Interface and Audio Processor.              |

| Bus Interface And Audio Processor Response | ALPR    | Command response received from the Bus Interface and Audio Processor. |

| ALP Master Debug Command                   | DBGMC   | Command issued to the ALP master DSP debug software.                  |

| ALP Master Debug Response                  | DBGMR   | Command response received from the ALP master DSP debug software.     |

| ALP Slave Debug Command                    | DBGSC   | Command issued to the ALP slave DSP debug software.                   |

| ALP Slave Debug Response                   | DBGSR   | Command response received from the ALP slave DSP debug software.      |

### 1.2 Major Data Paths

Table 1-1 describes data flows relative to the ALP. FIFO sizes are based on the assumption that a PCI bus request will be granted within 10 microseconds ( $\mu$ s).

TABLE 1-1. DATA FLOW DESCRIPTION

| FLOW                                                   | PINS                                                  | RATE                                                           | HW                       | FIFO  |

|--------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------|--------------------------|-------|

| LSUV: Local Uncompressed Video                         | In: Digital Video<br>Out: PCI                         | 20 <sup>+</sup> MB/s <sub>PEAK</sub><br>27 <sup>+</sup> on PCI | PCI Master               | 64 dw |

| RSUV: Remote Uncompressed Video                        | In: Digital Video<br>Out: PCI                         | 20 <sup>+</sup> MB/s <sub>PEAK</sub><br>27 <sup>+</sup> on PCI | PCI Master               | 64 dw |

| CVL: Compressed Video Local                            | In: IOB<br>Out: PCI                                   | 16kB/s (G.728)                                                 | PCI Master               | 4 dw  |

| CVR: Compressed Video Remote                           | In: PCI<br>Out: IOB                                   | 16kB/s (G.728)                                                 | PCI Master               | 4 dw  |

| CAL: Compressed Audio Local                            | In: PCI<br>Out: SPI                                   | 8kB/s                                                          | PCI Master               | 5 dw  |

| CAR: Compressed Audio Remote                           | In: SPI<br>Out: PCI                                   | 8kB/s                                                          | PCI Master               | 5 dw  |

| LCSFI/RCSFI: Annex D Compressed Image                  | In: PCI/IOB<br>Out: IOB/PCI                           | 16kB/s                                                         | PCI Master               | 8 dw  |

| LVAU: Local Communications Output (2B Channel)         | In: PCI<br>Out: Telecom                               | 16kB/s                                                         | PCI Master               | 8 dw  |

| RVAU: Remote Communications Stream (2B Channel)        | In: Telecom<br>Out: PCI                               | 16kB/s                                                         | PCI Master               | 8 dw  |

| I <sup>2</sup> C Command/Status (NPDC/NPDR, NPEC/NPER) | In: PCI/I <sup>2</sup> C<br>Out: I <sup>2</sup> C/PCI | Very Low                                                       | PCI Target<br>I2C Master | n/a   |

| IOB Command/Status by Host (PPC/PPR, ACC/ACR)          | In: PCI/IOB<br>Out: IOB/PCI                           | Low                                                            | PCI Target<br>IOB Master | n/a   |

| IOB Download (PPC)                                     | In: PCI<br>Out: IOB                                   |                                                                | PCI Target<br>IOB Master |       |

| IOB Command/Status by DSP (ACC/ACR)                    | In: IOB/SPI<br>Out: SPI/IOB                           |                                                                | IOB Master               | n/a   |

| ALPC: Host->DSP Command Mailbox                        | In: PCI<br>Out: SPI                                   | Low                                                            | PCI Target               | 32 w  |

| ALPR: DSP->Host Status Mailbox                         | In: SPI<br>Out: PCI                                   | Low                                                            | PCI Target               | 32 w  |

| DBGMC: Host->MDSP Debug Command Mailbox                | In: PCI<br>Out: MDSP                                  | Low                                                            | PCI Target               | 32 w  |

| DBGMR: MDSP->Host Debug Status Mailbox                 | In: MDSP<br>Out: PCI                                  | Low                                                            | PCI Target               | 32 w  |

| DBGSC: Host->SDSP dEbug Command Mailbox                | In: PCI<br>Out: SDSP                                  | Low                                                            | PCI Target               | 32 w  |

| DBGSR: SDSP->Host Debug Status Mailbox                 | In: SDSP<br>Out: PCI                                  | Low                                                            | PCI Target               | 32 w  |

| DCA: Local Digital Audio                               | In: IOB<br>Out: SPI                                   | 32kB/s                                                         | Channel                  | sw    |

| DPA: Remote Digital Audio                              | In: SPI<br>Out: IOB                                   | 32kB/s                                                         | Channel                  | sw    |

| DSP Algorithms                                         | In/Out SRAM                                           | 20MW/s <sub>PEAK</sub>                                         | Direct Access            | sw    |