#### Description

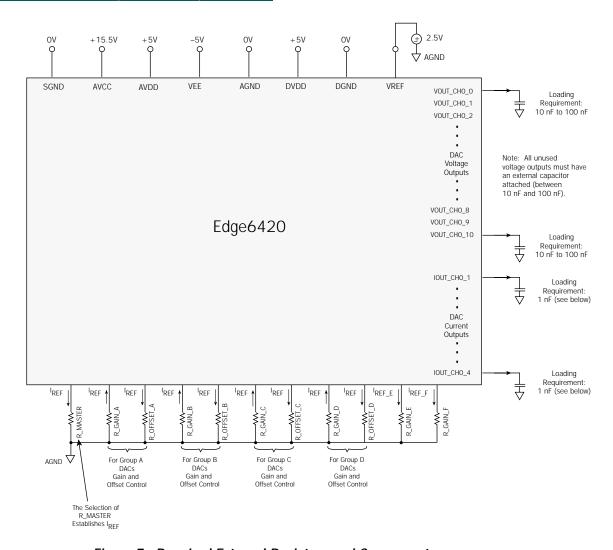

The Edge6420 is a monolithic device which has 64 integrated DACs that are designed specifically for all per channel wide-voltage and current levels needed for pin electronics inside automatic test equipment. The chip can also be used for other applications requiring multiple integrated voltage or current DAC outputs.

#### Voltage DACs

- Wide voltage (17V range)

- Adjustable full scale range

- · Adjustable minimum output

- 13 bits resolution

#### Current DACs

- ~3.6 mA full scale range

- · Adjustable full scale range

- 6/13 bits resolution

The DACs are programmed using a serial interface.

The inclusion of 64 total DACs into 1 package offers an extremely high density, flexible solution normally implemented using multiple components.

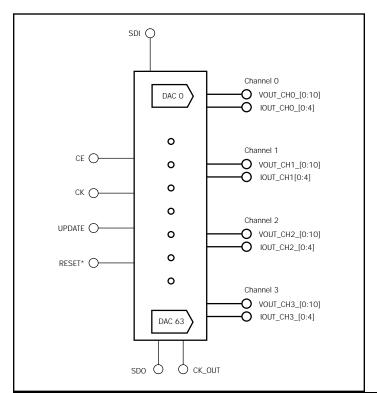

## Functional Block Diagram

#### **Features**

64 Total DACs/Package Including:

- Wide Voltage Output Range (17V Range); Useful for Supervoltage

- 44 Voltage DACs / Package

- 20 Current DACs / Package

- Adjustable Full Scale Range

- Adjustable Output Voltage Offset

- Small 13x13mm BGA Package

- All DACs are Guaranteed Monotonic

## **Applications**

- Test Equipment

- Applications requiring multiple programmable voltage and currents

## PIN Description

| Ball Name            | Ball Location                                                                                  | Description                                                                                                           |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VOUT_CH[0:3]_[0:4]   | G13, G15, F14, F13, F15, G3, F1, F2,<br>F3, E1, J3, J1, K2, K3, K1, J13, K15,<br>K14, K13, L15 | Group A DAC output volages for channels 0 to 3.                                                                       |  |  |  |  |

| VOUT_CH[0:3]_[5:6]   | E14, E15, E2, E3, L2, L1, L14, L13                                                             | Group B DAC output voltages for channels 0 to 3.                                                                      |  |  |  |  |

| VOUT_CH[0:3]_[7:8]   | E13, D14, D1, D2, L3, M2, M15, M14                                                             | Group C DAC output voltagges for channels 0 to 3.                                                                     |  |  |  |  |

| VOUT_CH[0:3]_[9:10]  | D15, D13, D3, C1, M1, M3, M13, N15                                                             | Group D DAC output voltages for channels 0 to 3.                                                                      |  |  |  |  |

| IOUT_CH[0:3]_[0:1]   | C15, C14, B1, C2, N1, N2, P15, N14                                                             | Group E DAC output voltages for channels 0 to 3.                                                                      |  |  |  |  |

| IOUT_CH[0:3]_[2:4]   | H14, H15, G14, H3, G1, G2, H2, H1,<br>J2, H13, J15, J14                                        | Group F DAC output voltages for channels 0 to 3.                                                                      |  |  |  |  |

| R_MASTER             | P5                                                                                             | Master external resistor used to define the reference current for the gain and offset setting block for voltage DACs. |  |  |  |  |

| R_GAIN_(A,B,C,D,E,F) | P11, R10, N10, P10, R9, N9                                                                     | Pins for external resistor to set current gain for both voltage and current output DACs.                              |  |  |  |  |

| R_OFFSET_(A,B,C,D)   | R6, P6, N6, R5                                                                                 | Pins for external resistor to set the offset voltage for Group A, B, C, and D voltage output DAC's.                   |  |  |  |  |

| SDI                  | B10                                                                                            | Serial data input.                                                                                                    |  |  |  |  |

| СК                   | A11                                                                                            | Clock for the input data shift register.                                                                              |  |  |  |  |

| UPDATE               | C6                                                                                             | Strobe to transfer the shift register data to the DACs.                                                               |  |  |  |  |

| CE                   | A10                                                                                            | Chip enable.                                                                                                          |  |  |  |  |

| RESET*               | C5                                                                                             | Active low chip reset. Sets the DACs to a known default state.                                                        |  |  |  |  |

| SD0                  | B5                                                                                             | Serial Data Out.                                                                                                      |  |  |  |  |

| CK_OUT               | A6                                                                                             | Regenerated clock output for daisy chain purposes.                                                                    |  |  |  |  |

| SCAN_OUT             | B11                                                                                            | Analog output test pin.                                                                                               |  |  |  |  |

| TEST_MODE            | В6                                                                                             | Test mode pin for internal scan.                                                                                      |  |  |  |  |

| VREF                 | С9                                                                                             | Reference input (for a 2.5V band gap).                                                                                |  |  |  |  |

| AVCC                 | C3, C12, N4, R12                                                                               | Positive analog voltage supply.                                                                                       |  |  |  |  |

| AVDD                 | C7, N7                                                                                         | Analog 5V supply.                                                                                                     |  |  |  |  |

| VEE                  | A9, R8, B9, P9                                                                                 | Negative analog voltage supply.                                                                                       |  |  |  |  |

| AGND                 | B8, N8                                                                                         | Analog ground (minimize noise).                                                                                       |  |  |  |  |

| SGND                 | A8, R7                                                                                         | Supply ground.                                                                                                        |  |  |  |  |

| DVDD                 | B7, P7                                                                                         | Digital voltage supply.                                                                                               |  |  |  |  |

| DGND                 | C8, P8                                                                                         | Digital supply ground.                                                                                                |  |  |  |  |

## PIN Description (continued)

| Ball Name | Ball Location                                                                                                                                                                                          | Description    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| N/C       | A1, A2, A3, A4, A5, A7, A12, A13,<br>A14, A15, B2, B3, B4, B12, B13,<br>B14, B15, C4, C10, C11, C13, N3,<br>N5, N11, N12, N13, P1, P2, P3,<br>P4, P12, P13, P14, R1, R2, R3,<br>R4, R11, R13, R14, R15 | Not connected. |

## PIN Description (continued)

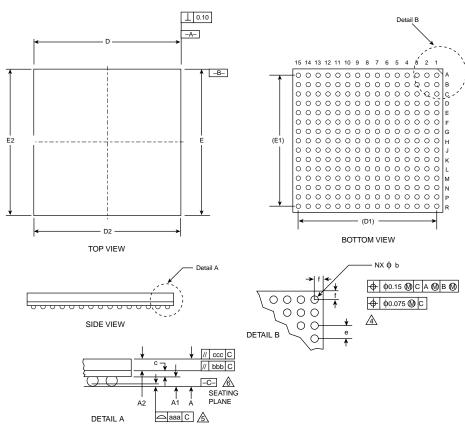

13mm x 13mm CSPBGA Package

A1 Ball Pad Indicator E6420

## Top View

| Α           | A1<br>1<br>N/C                                                                      | A2<br>(144)<br><sub>N/C</sub>                                                       | A3<br>(142)<br><sub>N/C</sub>                                                  | A4<br>(139)<br><sub>N/C</sub> | A5<br>(136)<br><sub>N/C</sub> | A6<br>(134)<br>CK_OUT  | A7<br>(131)<br><sub>N/C</sub> | A8<br>128<br>SGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A9<br>(125)<br>VEE                      | A10<br>(122)<br>CE                | A11<br>(119)<br>CK  | A12<br>(116)<br><sub>N/C</sub>         | A13<br>113)<br>N/C                                                                   | A14<br>(111)<br><sub>N/C</sub>                                                                           | A15<br>109<br><sub>N/C</sub>                                                                              |

|-------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------|-------------------------------|------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|---------------------|----------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| В           | B1 3 IOUT_CH1_0                                                                     | B2 2                                                                                | B3 (141)                                                                       | B4 (138)                      | B5 (135) SDO                  | B6 (132) TEST_MODE     | B7 (129)                      | B8 (127)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | B9 (124)                                | B10 (121)                         | B11  (18)  SCAN_OUT | B12                                    | B13 (112)                                                                            | B14                                                                                                      | B15<br>(108)<br>N/C                                                                                       |

| С           | C1 5 VOUT_CH1_10                                                                    | C2 4 IOUT_CH1_1                                                                     | C3 (143)                                                                       | C4 (140)                      | C5                            | C6                     | C7 (130)                      | C8 (126)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C9 (123)                                | C10 (120)                         | C11 (17)            | C12<br>(114)<br>AVCC                   | C13                                                                                  | C14<br>(105)<br>IOUT_CHO_1                                                                               | C15<br>(106)<br>IOUT_CHO_0                                                                                |

| D           | D1  8  VOUT_CH1_7                                                                   | D2  7  VOUT_CH1_8                                                                   | D3  6  VOUT_CH1_9                                                              | D4                            | D5                            | D6                     | D7                            | D8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D9                                      | D10                               | D11                 | D12                                    | D13<br>(104)<br>VOUT_CHO_10                                                          | D14 (102)<br>VOUT_CHO_8                                                                                  | D15 (103) VOUT_CHO_9                                                                                      |

| E           | E1 11 VOUT_CH1_4                                                                    | E2  VOUT_CH1_5                                                                      | E3 9 VOUT_CH1_6                                                                | E4                            | E5                            | E6                     | E7                            | E8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | E9                                      | E10                               | E11                 | E12                                    | E13<br>(101)<br>VOUT_CH0_7                                                           | E14<br>99<br>VOUT_CH0_5                                                                                  | E15<br>100<br>VOUT_CHO_6                                                                                  |

| F           | F1 14 VOUT_CH1_1                                                                    | F2 13 VOUT_CH1_2                                                                    | F3 12 VOUT_CH1_3                                                               | F4                            | F5                            | F6                     | F7                            | F8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | F9                                      | F10                               | F11                 | F12                                    | F13<br>97<br>VOUT_CH0_3                                                              | F14<br>96<br>VOUT_CH0_2                                                                                  | F15<br>98<br>VOUT_CH0_4                                                                                   |

| G           | G1 17 IOUT_CH1_3                                                                    | G2<br>16<br>IOUT_CH1_4                                                              | G3<br>(15)<br>VOUT_CH1_0                                                       | G4                            | G5                            |                        |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ng the inn                              |                                   | G11                 | G12                                    | G13<br>94<br>VOUT_CHO_O                                                              | G14<br>93<br>IOUT_CH0_4                                                                                  | G15<br>95)<br>VOUT_CHO_1                                                                                  |

| Н           | H1 20 IOUT_CH2_3                                                                    | H2<br>19<br>IOUT_CH2_2                                                              | H3<br>18<br>IOUT_CH1_2                                                         | H4                            | H5                            | diss<br>bal            | sipation.<br>Is should        | This midded the connection of | dle grid of<br>ected to th<br>ing. Orde | ne                                | H11                 | H12                                    | H13<br>90<br>IOUT_CH3_2                                                              | H14<br>91<br>IOUT_CH0_2                                                                                  | H15<br>92<br>IOUT_CH0_3                                                                                   |

| J           | J1 23                                                                               | J2<br>21                                                                            | J3                                                                             | J4                            | J5                            |                        | 420BBG i<br>lesired.          | f populat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ed middle                               |                                   | J11                 | J12                                    | J13                                                                                  | J14<br>88<br>IOUT_CH3_4                                                                                  | J15<br>89<br>IOUT_CH3_3                                                                                   |

|             | I VOLIT CH2 1                                                                       | I IOUT CH2 4                                                                        |                                                                                |                               |                               |                        |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                   |                     |                                        |                                                                                      |                                                                                                          | IOUI_CH3_3                                                                                                |

| K           | VOUT_CH2_1                                                                          | K2  (24)                                                                            | VOUT_CH2_0  K3  25                                                             | K4                            | K5                            | K6                     | K7                            | K8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | K9                                      | K10                               | K11                 | K12                                    | K13 84                                                                               | K14<br>85                                                                                                | K15                                                                                                       |

| K<br>L      | K1                                                                                  | K2<br>(24)<br>VOUT_CH2_2<br>L2<br>(27)                                              | K3<br>25<br>VOUT_CH2_3<br>L3                                                   | L4                            | K5                            | K6 L6                  | K7                            | K8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | K9                                      | K10<br>L10                        | K11                 | K12                                    | K13<br>84)<br>VOUT_CH3_3<br>L13<br>81)                                               | K14<br>85<br>VOUT_CH3_2<br>L14<br>82                                                                     | VOUT_CH3_1<br>L15                                                                                         |

|             | K1 (26) VOUT_CH2_4 L1 (28) VOUT_CH2_6 M1 (31)                                       | K2<br>(24)<br>VOUT_CH2_2<br>L2<br>(27)<br>VOUT_CH2_5<br>M2<br>(30)                  | K3<br>25<br>VOUT_CH2_3<br>L3<br>29<br>VOUT_CH2_7<br>M3<br>32                   |                               |                               |                        |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |                                   |                     |                                        | K13  84  VOUT_CH3_3  L13  81  VOUT_CH3_6  M13  78                                    | K14<br>85<br>VOUT_CH3_2<br>L14<br>82<br>VOUT_CH3_5<br>M14<br>79                                          | 86<br>VOUT_CH3_1<br>L15<br>83<br>VOUT_CH3_4<br>M15                                                        |

| L           | K1 26 VOUT_CH2_4 L1 28 VOUT_CH2_6 M1                                                | K2<br>VOUT_CH2_2<br>L2<br>L2<br>VOUT_CH2_5<br>M2                                    | K3<br>25<br>VOUT_CH2_3<br>L3<br>29<br>VOUT_CH2_7<br>M3_                        | L4                            | L5                            | L6                     | L7                            | L8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L9                                      | L10                               | L11                 | L12                                    | K13<br>84<br>VOUT_CH3_3<br>L13<br>81<br>VOUT_CH3_6<br>M13                            | K14<br>85<br>VOUT_CH3_2<br>L14<br>82<br>VOUT_CH3_5<br>M14                                                | 001_CH3_1<br>L15<br>83<br>VOUT_CH3_4<br>M15                                                               |

| L<br>M      | K1 (26) VOUT_CH2_4 L1 (28) VOUT_CH2_6 M1 (31) VOUT_CH2_9 N1 (34)                    | K2 (24) VOUT_CH2_2 L2 (27) VOUT_CH2_5 M2 (30) VOUT_CH2_8 N2 (33) IOUT_CH2_1 P2 (38) | K3                                                                             | M4 N4 42                      | M5                            | N6 48 R_OFFSET_C P6 49 | L7                            | N8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | N9 58 R_GAIN_F P9 57                    | M10 M10 M10 M10 R_GAIN_C P10 60   | M11                 | M12  M12  M12  M12  M12  M12  M16  M16 | K13<br>84<br>VOUT_CH3_3<br>L13<br>81<br>VOUT_CH3_6<br>M13<br>78<br>VOUT_CH3_9<br>N13 | K14 (85) VOUT_CH3_2 L14 (82) VOUT_CH3_5 M14 (79) VOUT_CH3_8 N14 (76) IOUT_CH3_1 P14 (74)                 | 86<br>VOUT_CH3_1<br>L15<br>83<br>VOUT_CH3_4<br>M15<br>80<br>VOUT_CH3_7<br>N15<br>77<br>VOUT_CH3_10<br>P15 |

| L<br>M<br>N | K1 (26) VOUT_CH2_4 L1 (28) VOUT_CH2_6 M1 (31) VOUT_CH2_9 N1 (34) IOUT_CH2_0 P1 (36) | K2 (24) VOUT_CH2_2 L2 (27) VOUT_CH2_5 M2 (30) VOUT_CH2_8 N2 (33) IOUT_CH2_1 P2      | K3 (25) VOUT_CH2_3 L3 (29) VOUT_CH2_17 M3 (32) VOUT_CH2_10 N3 (35) N/C P3 (40) | N4 42 AVCC P4 43              | M5                            | N6 N6 48 R_OFFSET_C P6 | N7 (51) AVDD P7 (52)          | N8 S4 AGND P8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | N9 58 R_GAIN_F                          | M10  M10  N10  61)  R_GAIN_C  P10 | M11 65 NC P11       | M12  N12  68  NIC  P12                 | K13  84  VOUT_CH3_3  L13  81  VOUT_CH3_6  M13  78  VOUT_CH3_9  N13  71  N/C  P13  69 | K14<br>85<br>VOUT_CH3_2<br>L14<br>82<br>VOUT_CH3_5<br>M14<br>79<br>VOUT_CH3_8<br>N14<br>76<br>IOUT_CH3_1 | 86<br>VOUT_CH3_1<br>L15<br>83<br>VOUT_CH3_4<br>M15<br>80<br>VOUT_CH3_7<br>N15<br>77<br>VOUT_CH3_10<br>P15 |

## PIN Description (continued)

### 13mm x 13mm CSPBGA Package

### **Bottom View**

| 15                        | 14                          | 13                            | 12                          | 11                          | 10                    | 9                      | 8                     | 7                           | 6                        | 5                          | 4                             | 3                           | 2                             | 1                       |   |

|---------------------------|-----------------------------|-------------------------------|-----------------------------|-----------------------------|-----------------------|------------------------|-----------------------|-----------------------------|--------------------------|----------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------|---|

| A15<br>109<br>N/C         | A14<br>(111)<br>N/C         | A13<br>113)<br>N/C            | A12<br>(116)<br>N/C         | A11<br>(119)<br>CK          | A10<br>(122)<br>CE    | A9<br>(125)<br>VEE     | A8<br>128<br>SGND     | A7<br>(131)<br>N/C          | A6<br>(134)<br>CK_OUT    | A5<br>(136)<br>N/C         | A4<br>(139)<br>N/C            | A3<br>(142)<br>N/C          | A2<br>(144)<br><sub>N/C</sub> | A1<br>1<br>N/C          | A |

| B15<br>108<br>N/C         | B14<br>(110)<br>N/C         | B13                           | B12<br>(115)<br>N/C         | B11<br>(118)<br>SCAN_OUT    | B10<br>(121)<br>SDI   | 124<br>VEE             | B8 (127)<br>AGND      | 129<br>DVDD                 | B6<br>(132)<br>TEST_MODE | B5<br>135<br>SD0           | B4<br>138<br>N/C              | B3<br>(141)<br>N/C          | B2<br>2<br>N/C                | B1<br>3<br>IOUT_CH1_0   | В |

| C15<br>106<br>IOUT_CH0_0  | C14<br>105<br>IOUT_CHO_1    | C13                           | C12<br>(114)<br>AVCC        | C11<br>(117)<br>N/C         | C10<br>(120)<br>N/C   | C9<br>(123)<br>VREF    | C8<br>(126)<br>DGND   | C7                          | C6<br>(133)<br>UPDATE    | C5<br>(137)<br>RESET*      | C4<br>(140)<br><sub>N/C</sub> | C3<br>(143)<br>AVCC         | C2<br>4<br>IOUT_CH1_1         | C1 5 VOUT_CH1_10        | С |

| D15<br>103<br>VOUT_CH0_9  | D14<br>102<br>VOUT_CHO_8    |                               | D12                         | D11                         | D10                   | D9                     | D8                    | D7                          | D6                       | D5                         | D4                            | D3  6  VOUT_CH1_9           | D2  7  VOUT_CH1_8             | +                       | D |

| E15<br>100<br>VOUT_CH0_6  |                             | E13<br>(101)<br>VOUT_CHO_7    | E12                         | E11                         | E10                   | E9                     | E8                    | E7                          | E6                       | E5                         | E4                            | E3  9  VOUT_CH1_6           | E2<br>10<br>VOUT_CH1_5        | E1 (11) VOUT_CH1_4      | E |

| F15<br>98<br>VOUT_CH0_4   | F14<br>96<br>VOUT_CH0_2     | F13<br>97<br>VOUT_CH0_3       | F12                         | F11                         | F10                   | F9                     | F8                    | F7                          | F6                       | F5                         | F4                            | F3<br>12<br>VOUT_CH1_3      | F2<br>13<br>VOUT_CH1_2        | F1 14 VOUT_CH1_1        | F |

| G15<br>95<br>VOUT_CH0_1   | G14<br>93<br>IOUT_CHO_4     | G13<br>94<br>VOUT_CHO_0       | G12                         | G11                         | G10                   |                        |                       | ulating th                  |                          | G5                         | G4                            | G3<br>15<br>VOUT_CH1_0      | G2<br>16<br>IOUT_CH1_4        | G1<br>17<br>IOUT_CH1_3  | G |

| H15<br>92<br>IOUT_CH0_3   | H14<br>91<br>IOUT_CH0_2     | H13<br>90<br>IOUT_CH3_2       | H12                         | H11                         | H10                   | dissipati<br>balls sho | on. This<br>ould be c | middle gronnected floating. | rid of<br>to the         |                            | H4                            | H3<br>18<br>IOUT_CH1_2      | H2<br>19<br>IOUT_CH2_2        | H1 20 IOUT_CH2_3        | Н |

| J15<br>89<br>IOUT_CH3_3   | J14<br>88<br>IOUT_CH3_4     | J13<br>87<br>VOUT_CH3_0       | J12                         | J11                         | J10                   | is desire              |                       | oulated m                   | iddle                    |                            | J4                            | J3<br>22<br>VOUT_CH2_0      | J2<br>21<br>IOUT_CH2_4        | J1 (23) VOUT_CH2_1      | J |

| K15<br>86<br>VOUT_CH3_1   | K14<br>85<br>VOUT_CH3_2     | K13<br>84<br>VOUT_CH3_3       | K12                         | K11                         | K10                   | K9                     | K8                    | K7                          | K6                       | K5                         | K4                            | K3<br>25<br>VOUT_CH2_3      | K2<br>24<br>VOUT_CH2_2        | K1 26 VOUT_CH2_4        | K |

| L15<br>83<br>VOUT_CH3_4   | L14<br>82<br>VOUT_CH3_5     | L13  81)  VOUT_CH3_6          | L12                         | L11                         | L10                   | L9                     | L8                    | L7                          | L6                       | L5                         | L4                            | L3<br>29<br>VOUT_CH2_7      | L2<br>27<br>VOUT_CH2_5        | L1 28 VOUT_CH2_6        | L |

| M15<br>80<br>VOUT_CH3_7   | M14<br>79<br>VOUT_CH3_8     | M13<br>78<br>VOUT_CH3_9       | M12                         | M11                         | M10                   | M9                     | M8                    | M7                          | M6                       | M5                         | M4                            | M3<br>32<br>VOUT_CH2_10     | M2<br>30<br>VOUT_CH2_8        | M1<br>31)<br>VOUT_CH2_9 | М |

| N15<br>77<br>VOUT_CH3_10  | N14<br>76<br>IOUT_CH3_1     | N13<br>(71)<br><sub>N/C</sub> | N12<br>68<br>N/C            | N11<br>65<br><sub>N/C</sub> | N10<br>61<br>R_GAIN_C | N9<br>58<br>R_GAIN_F   | N8<br>54<br>AGND      | N7<br>(51)<br>AVDD          | N6<br>48<br>R_OFFSET_C   | N5<br>45<br><sub>N/C</sub> | N4<br>42<br>AVCC              | N3<br>35<br><sub>N/C</sub>  | N2<br>33<br>IOUT_CH2_1        | N1<br>34<br>IOUT_CH2_0  | N |

| P15<br>(75)<br>IOUT_CH3_0 | P14<br>74<br><sub>N/C</sub> | P13<br>69<br><sub>N/C</sub>   | P12<br>66<br><sub>N/C</sub> | P11<br>63<br>R_GAIN_A       | P10<br>60<br>R_GAIN_D | P9 (57)<br>VEE         | P8 55 DGND            | P7<br>52<br>DVDD            | P6<br>49<br>R_OFFSET_B   | P5<br>46<br>R_MASTER       | P4 43 N/C                     | P3<br>40<br><sub>N/C</sub>  | P2<br>38<br>N/C               | P1 36)                  | P |

| R15                       | R14                         | R13                           | R12                         | R11 64 N/C                  | R10<br>62<br>R_GAIN_B | R9<br>59<br>R_GAIN_E   | R8<br>56<br>VEE       | R7<br>53<br>SGND            | R6  50  R_OFFSET_A       | R5<br>47<br>R_OFFSET_D     | R4 44 N/C                     | R3<br>41)<br><sub>N/C</sub> | R2<br>39<br><sub>N/C</sub>    | R1 37)                  | R |

### Circuit Description

#### **Chip Overview**

The Edge6420 provides 64 output levels (44 voltage and 20 current). These outputs can easily be configured to generate the specific analog voltage and current requirements for 4 channels of ATE pin electronics including:

- 3 level driver

- Window comparator

- Active load

- Per pin PMU

without requiring any scaling or shifting via external components.

The Edge6420 has the flexibility to be used in other configurations for other applications.

Programming of the chip is done using a 4 bit digital interface comprised of:

- Serial Data In

- Clock

- Update

- Chip Enable.

#### **Grouping of DACs**

DACs are separated into 4 channels of 6 distinct functional groups. Groups are defined by:

- Type (voltage or current output)

- Resolution (# of bits)

- Output range

- Output compliance.

Table 1 defines the DACs on a per channel basis:

| Attribute                                           | Group<br>A             | Group<br>B             | Group<br>C           | Group<br>D             | Group<br>E                      | Group<br>F                      |

|-----------------------------------------------------|------------------------|------------------------|----------------------|------------------------|---------------------------------|---------------------------------|

| Total # of<br>DACs in Group                         | 5 per channel          | 2 per channel          | 2 per channel        | 2 per channel          | 2 per channel                   | 3 per channel                   |

| Туре                                                | V                      | V                      | V                    | V                      | I                               | I                               |

| Resolution (# of bits)                              | 13                     | 13                     | 13                   | 13                     | 13                              | 6                               |

| Output Range:  Max DAC Range (Note 1)  Offset Range | 11.5V<br>-3.5V to 2.5V | 11.5V<br>-3.5V to 2.5V | 17V<br>-3.5V to 2.5V | 11.5V<br>-3.5V to 2.5V | 3.6 mA<br>-128 LSB<br>(Note 2)  | 3.6 mA<br>0                     |

| Adjustable Output Offset                            | yes                    | yes                    | yes                  | yes                    | no                              | no                              |

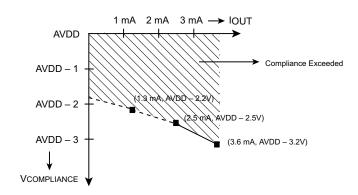

| Compliance                                          | ±100 μA                | ±100 μA                | ±100 μA              | ±100 μA                | -0.2 to AVDD - 2.2V<br>(Note 3) | -0.2 to AVDD - 2.2V<br>(Note 3) |

- Note 1: The max DAC range is achieved through specific AVCC, AVEE, and Gain resistor settings. See the equations in the "DAC Voltage Output Overview", "DAC Current Output Overview", and specifications for details.

- Note 2: -128 LSB is equivalent to -128 \* LSB, where LSB = Range /  $2^{13}$ . For max range case of 3.6 mA, this offset would thus be: -56.26  $\mu$ A of offset current at Code 0.

- Note 3: Compliance specified in the table is at IOUT = 1.3mA. Maximum compliance is lower at higher currents. Please refer to specifications for compliance at other output currents.

#### Table 1. DAC Grouping

### Circuit Description (continued)

#### **DAC Voltage Output Overview**

The output voltage of Group A, B, C, and D DACs is governed by the following equation:

$$V_{OUT\_[A:D]} = \left(K_{G[A:D]} * V_{REF} * \frac{R\_GAIN\_[A:D]}{R\_MASTER} * \frac{DATA}{8192}\right) + V_{OFFSET\_[A:D]}$$

#### Equation 1.

where:

DATA corresponds to the base-10 value of the binary data loaded into the shift register shown in Figure 2.

$K_{G[A:D]}$  is a multiplying factor that is fixed, as follows:

$$K_{GA} = 4$$

$K_{GB} = 4$   $K_{GD} = 4$

$$K_{GB} = 4$$

$K_{GD} = 4$

$$V_{REF} = 2.5V$$

#### Offset

The offset for each of the voltage DACs is governed by the following equation:

$$V_{OFFSET\_[A:D]} = K_{OFFSET} * V_{REF} * \left(0.5 - \left(\frac{R_{OFFSET\_[A:D]}}{R_{MASTER}}\right)\right)$$

#### Equation 2.

where:

$$K_{OFFSFT} = 2$$

$$V_{REF} = 2.5V$$

#### **External Resistors**

The recommended resistor values for the above equations are as follows:

R MASTER =

$$100$$

K $\Omega$  (0.1% precision)

$$R GAIN [A:D] = (0.4 \text{ to } 1.15) * R MASTER$$

$$R_{OFFSET_[A:D]} = (0.0 \text{ to } 1.2) * R_{MASTER}$$

#### Minimum / Maximum Output Voltages

See Table 2 for the minimum and maximum possible voltages of a voltage output.

| DAC Setting<br>MSB LSB | V <sub>OUT_[A:D]</sub> (V) |

|------------------------|----------------------------|

| 0000Н                  | V <sub>OFFSET_[A:D]</sub>  |

| 1FFFH                  | V <sub>MAX_[A:D]</sub>     |

#### Table 2. Minimum/Maximum Output Voltages

where:

$V_{OFFSET[A:D]}$  is defined in equation 2

and

$$V_{MAX\_[A:D]} = \left(K_{G[A:D]} * V_{REF} * \frac{R\_GAIN\_[A:D]}{R\_MASTER} * \frac{8191}{8192}\right) + V_{OFFSET\_[A:D]}$$

#### Equation 3.

The most negative voltage possible for the Edge6420 is -3.5V when VEE = -4.5V.

#### Resolution

The resolution of the DACs in Groups A, B, C, and D is:

where V<sub>RANGE\_[A:D]</sub> is defined in Equation 4.

#### Range

The range of the DACs in Groups A, B, C and D is:

$$V_{RANGE\_[A:D]} = K_{G[A:D]} * V_{REF} * \frac{R\_GAIN\_[A:D]}{R\_MASTER} * \frac{8191}{8192}$$

Equation 4.

### Circuit Description (continued)

#### Group A DACs

There are five Group A DACs/channel. Group A DACs have a centralized offset, gain and range that is independent of any other group.

Group A DACs are characterized by 13 bit resolution and their typical outputs are governed by the following equation:

$$V_{OUT\_A} = \left(10 * \frac{R\_GAIN\_A}{R\_MASTER} * \frac{DATA}{8192}\right) + V_{OFFSET\_A}$$

where:

$$V_{OFFSET\_A} = \left(5 * \left(.5 - \frac{R_OFFSET\_A}{R_MASTER}\right)\right)$$

*Note:*  $V_{REF} = 2.5V$

#### Group B DACs

There are two Group B DACs/channel. Group B DACs have a centralized offset, gain and range that is independent of any other group.

Group B DACs are characterized by 13 bit resolution and their typical outputs are governed by the following equation:

$V_{OUT\_B} = \left(10 * \frac{R\_GAIN\_B}{R\_MASTER} * \frac{DATA}{8192}\right) + V_{OFFSET\_B}$

where:

$$V_{OFFSET\_B} = \left(5 * \left(.5 - \frac{R_OFFSET\_B}{R_MASTER}\right)\right)$$

*Note:*  $V_{REF} = 2.5V$

### Group C DACs

There are two Group C DACs/channel. Group C DACs have a centralized offset, gain and range that is independent of any other group'.

Group C DACs are characterized by 13 bit resolution and their typical outputs are governed by the following equation:

$$V_{OUT\_C} = \left(20 * \frac{R\_GAIN\_C}{R\_MASTER} * \frac{DATA}{8192}\right) + V_{OFFSET\_C}$$

where:

$$V_{OFFSET\_C} = \left(5 * \left(.5 - \frac{R_OFFSET\_C}{R_MASTER}\right)\right)$$

*Note:*  $V_{REF} = 2.5V$

#### **Group D DACs**

There are two Group D DACs/channel. Group D DACs have a centralized offset, gain and range that is independent of any other group.

Group D DACs are characterized by 13 bit resolution and their typical outputs are governed by the following equation:

$$V_{OUT\_D} = \begin{pmatrix} 10 * & R\_GAIN\_D \\ \hline R\_MASTER & 8192 \end{pmatrix} + V_{OFFSET\_D}$$

where:

$$V_{OFFSET\_D} = \left(5 * \left(.5 - \frac{R_OFFSET\_D}{R_MASTER}\right)\right)$$

Note:  $V_{REF} = 2.5V$

#### **DAC Current Output Overview**

The output current of Group E and F DACs is governed by the following equation:

$$I_{OUT\_[E:F]} = \left( \begin{array}{c} K_{G[E:F]} * I_{REF\_[E:F]} * \\ \hline MAX\_{COUNT\_[E:F]} \end{array} \right) + I_{OFFSET\_[E:F]}$$

#### Equation 5.

where:

DATA corresponds to the base-10 value of the binary data loaded into the shift resister in Figure 2.

$$I_{REF\_[E:F]} = \frac{V_{REF}}{R\_GAIN\_[E:F]}$$

K<sub>G[E:F]</sub> is a multiplying factor that is fixed, as follows:

$$K_{GF} = 80$$

$K_{GF} = 80$

$$V_{RFF} = 2.5V$$

$$MAX\_COUNT\_E = 8192$$

$MAX\_COUNT\_F = 64$

### Circuit Description (continued)

#### Offset

The typical offset for each current DAC is governed by the following equations:

$$I_{OFFSET\_E} = -\frac{K_{GE} * V_{REF}}{R\_{GAIN\_E}} * \frac{128}{MAX\_{COUNT\_E}}$$

#### Equation 6.

$$IOFFSET F = 0$$

#### **Group E DACs**

There are 2 Group E DACs/channel. Group E DACs are characterized by:

- Current outputs (current flows out of the chip)

- 13 bit resolution

- Fixed offset (–128 \* LSB typical)

- Adjustable full scale range (but < 3.6 mA).</li>

The output current equation for Group E DACs is:

$$I_{OUT\_E} = \left(\frac{DATA}{8192} * \frac{200}{R\_GAIN\_E}\right) - \frac{3.125}{R\_GAIN\_E}$$

where:

$$55 \text{ k}\Omega \leq \text{R\_GAIN\_E} \leq 156 \text{ k}\Omega$$

Note:  $V_{REF} = 2.5V$

#### Group F DACs

There are 3 Group F DACs/channel. Group F DACs are characterized by:

- Current outputs (current flows out of the chip)

- 6 bit resolution

- Fixed offset (O typical)

- Adjustable full scale range (but < 3.6 mA).</li>

The output current equation for Group F DACs is:

$$I_{OUT\_F} = \frac{DATA}{64} * \frac{200}{R\_GAIN\_F}$$

where:

$$55 \text{ k}\Omega \leq \text{R\_GAIN\_F} \leq 156 \text{ k}\Omega$$

*Note:*  $V_{REF} = 2.5V$

## Circuit Description (continued)

### Address Map

| Address               | Channel          | Group                  | Туре               | Typical Uses                                          |

|-----------------------|------------------|------------------------|--------------------|-------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4 | 0<br>0<br>0<br>0 | A<br>A<br>A<br>A       | V<br>V<br>V<br>V   | Driver & Comparator Levels                            |

| 5<br>6                | 0<br>0           | B<br>B                 | V<br>V             | PPMU Comparator Thresholds                            |

| 7<br>8                | 0                | C<br>C                 | V<br>V             | PPMU Force Voltage, Flash<br>Programming Supervoltage |

| 9<br>10               | 0                | D<br>D                 | V<br>V             | Load Commutating Voltage                              |

| 11<br>12              | 0<br>0           | E<br>E                 |                    | Load Source and Sink<br>Programming currents          |

| 13<br>14<br>15        | 0<br>0<br>0      | F<br>F<br>F            |                    | Chip Bias, Rising/Falling<br>Slew Rate Adjust         |

| 16-31                 | 1                | Same format as ab      | ove for Channel 1. |                                                       |

| 32-47                 | 2                | Same format as ab      | ove for Channel 2. |                                                       |

| 48-63                 | 3                | Same format as ab      | ove for Channel 3. |                                                       |

| 64                    | N/A              | All V/I                |                    | Parallel Load for all DACs                            |

| 65-255                | Not used         | (reserved for future u | pgradability).     |                                                       |

## Circuit Description (continued)

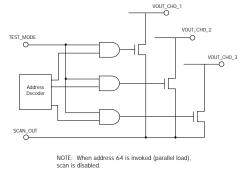

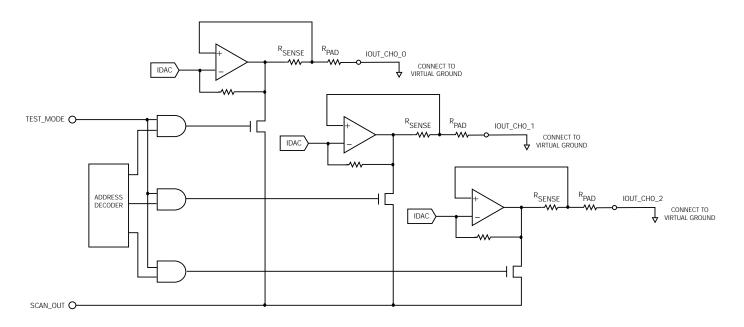

Figure 1. DAC Functionality Block Diagram

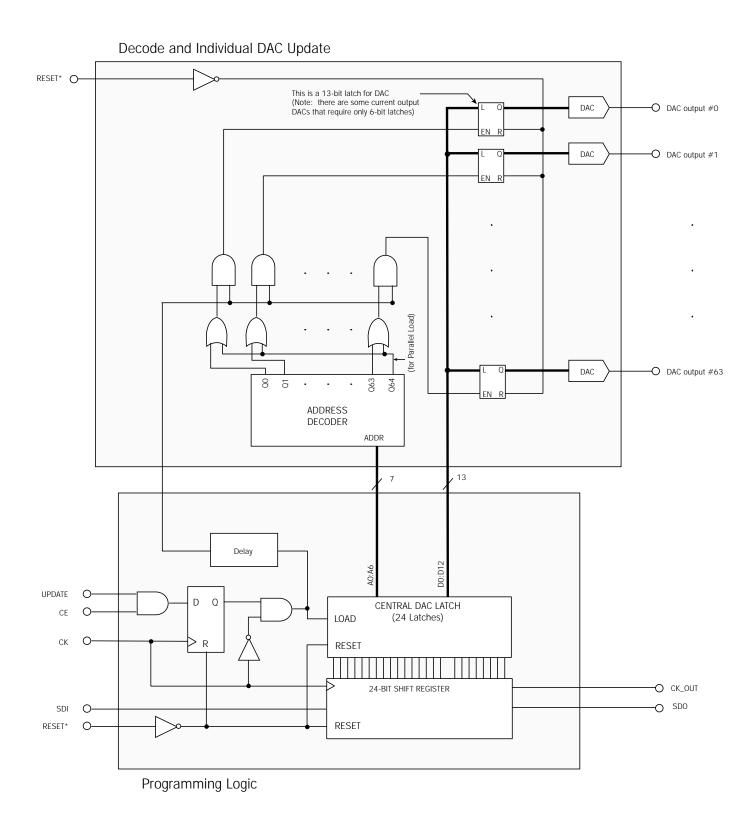

### Circuit Description (continued)

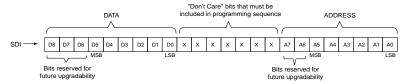

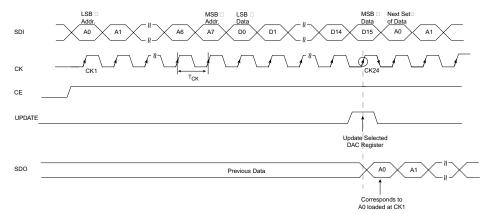

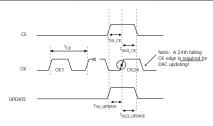

#### **Programming Sequence**

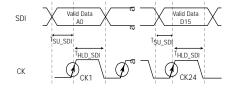

The DACs are programmed serially (see Figures 1, 2a, 2b, and 3). On each rising edge of CK, SDI is loaded into a shift register. It requires 24 Clocks to fully load the shift register (8 address bits + 16 data bits).

#### For Groups A, B, C, D, and E DACs:

Address and data are loaded LSB first, MSB last. In a 24 clock sequence, AO, as shown in Figure 2a, is loaded into the shift register on the first CK rising edge, and D15 is loaded last on the 24th rising CK edge. Note that a 24th falling CK edge is required to transfer the data from the Central DAC Latch to the selected DAC latch (See Figure 1). See detailed Timing Diagrams in the "AC Characteristics" specifications section.

#### For Group F DACs:

The loading sequence is the same as Groups A-E, but

Group F uses only 6 bits, and these bits must be programmed as shown in Figure 2b. 24 clock cycles are required for programming, with AO loaded on the first rising CK edge, and D8 (as shown in Figure 2b) loaded on the 24th rising CK edge.

As is the case with other groups, a 24th falling edge of CK24 is required for proper programming of Group F DACs.

#### **Chip Enable**

CE is a synchronous input which determines whether the Central DAC latch shown in Figure 1 is loaded with data from the shift register. CE is also necessary to update a DAC. If CE is high, rising edges of CK load data from the shift register to an internal latch. If CE is low, central DAC latch updating is disabled.

CE Central and Individual DAC Latch "Load" Status

low Central and individual DAC latch loading is

disabled

high Central and individual DAC latches are loaded

Figure 2a. Format of Address and Data in Shift Register for Group A, B, C, D, and E DACs (13-bits)

Figure 2b. Format of Address and Data in Shift Register for Group F DACs (6-bits)

Figure 3. Serial Data Programming Sequence

### Circuit Description (continued)

#### **Digital Outputs**

SDO is a CMOS output, swinging rail to rail between DVDD and DGND.

#### **Chip Reset and Power Up**

RESET\* for the Edge6420 is active low.

When the Edge6420 first powers up, the latches will turn on to the same state as though RESET\* had been asserted.

When RESET\* is brought low, the latches, and therefore the DAC levels, will go to a known state that corresponds to a specific DATA code. See the "Application Information" section for an example of how this functionality works. The known states are:

| GROUP | RESET* State (Code) |

|-------|---------------------|

| А     | 1000H               |

| В     | 1000H               |

| С     | 1000H               |

| D     | 1000H               |

| Е     | 0000Н               |

| F     | 1000H               |

Care should be taken to ensure RESET\* is invoked properly. It is critical to ensure that if a RESET\* is asserted after UPDATE has transitioned from a high to low state, that RESET\* stay low, at least 2  $\mu s$ . To understand this precaution, notice in Figure 1 that UPDATE is delayed in order to enable individual DAC latches. If RESET\* is not brought low for sufficient time, an individual DAC update  $\underline{will}$  occur.

By simply forcing the RESET\* pulse low for a minimum of  $2~\mu s$ , when a CK frequency of 50 MHz or less is used, the 6420 will clear properly to the known states shown above.

#### **Power Supply Sequence**

Power supplies should be asserted in the following order:

- 1. VEE

- 2. AVDD

- 3. DVDD

- 4. AVCC