### PLC18V8Z Series

### **FEATURES**

- 20-pin Universal Programmable Array Logic

- Virtually Zero-Standby-power

- Functional replacement for Series 20 PAL devices

- I<sub>OL</sub> = 24mA

- High-performance CMOS EPROM cell technology

- Erasable

- Reconfigurable

- 100% testable

- 40ns Max propagation delay.

- Up to 18 inputs and 8 input/output macro cells

- Programmable output polarity

- Power-up reset on all registers

- Register Preload capability

- Synchronous Preset/Asynchronous Reset

- Security fuse to prevent duplication of proprietary designs

- Design support provided using AMAZE software development package and other CAD tools for PLDs

- Available in 300mil-wide DIP with quartz window, ceramic DIP (OTP)

### **APPLICATIONS**

- Battery powered instruments

- Laptop and pocket computers

- Industrial control

- Medical Instruments

- Portable communications equipment

### **ORDERING INFORMATION**

| DESCRIPTION                                                               | ORDER CODE            | PACKAGE<br>DESIGNATOR* |

|---------------------------------------------------------------------------|-----------------------|------------------------|

| 20-Pin Ceramic Dual<br>In-Line Package<br>300mil-wide                     | PLC18V8Z/<br>BRA (OT) | GDIP1-T20              |

| 20-Pin Ceramic Dual<br>In-Line Package<br>300mil-wide w/ quartz<br>window | PLC18V8Z/<br>BRA      | GDIP1-T20              |

<sup>\*</sup> MIL-STD 1835 or Appendix A of 1995 Military Data Handbook

### DESCRIPTION

The PLC18V8Z is a universal PAL® device featuring high performance and virtually zero-standby power for power sensitive applications. It is a reliable, user-configurable substitute for discrete TTL/CMOS logic. While compatible with TTL and HCT it can also replace HC logic over the V<sub>CC</sub> range of 4.5 to 5.5V.

The PLC18V8Z is a two-level logic element comprised of 10 inputs, 74 AND gates (product terms) and 8 output Macro cells.

Each output features an "Output Macro Cell" which can be individually configured as a dedicated input, a combinatorial output, or a registered output with internal feedback. As a result, the it is capable of emulating all common 20-pin PAL devices to reduce documentation, inventory, and manufacturing costs.

A power-up reset function and a Register Preload function have been incorporated in the architecture to facilitate state machine design and testing.

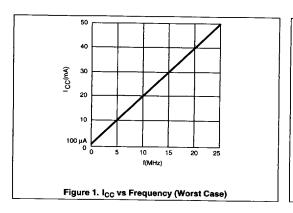

With a standby current of less than 250µA and active power consumption of 2mA/MHz, the device is ideally suited for power sensitive applications in battery operated/backed portable instruments and computers.

The PLC18V8Z is also processed to industrial requirements for operation over an extended temperature range of -55°C to +125°C and supply voltage of 4.5V to 5.5V.

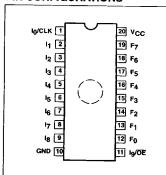

### PIN CONFIGURATIONS

### PIN LABEL DESCRIPTIONS

| 1   | Dedicated input            |

|-----|----------------------------|

| В   | Bidirectional input/output |

| 0   | Dedicated output           |

| D   | Registered output          |

|     | (D-type flip-flop)         |

| F   | Macrocell Input/Output     |

| CLK | Clock Input                |

| OE  | Output Enable              |

| Vcc | Supply Voltage             |

| GND | Ground                     |

7110826 0085817 122 🖿

November 15, 1993

1029

853-1584 11362

<sup>@</sup>PAL is a registered trademark of Monolithic Memories Inc. a wholly owned subsidiary of Advanced Micro Devices, Inc

## PLC18V8Z Series

November 15, 1993

1030

**- 7110826 0085818 069**

### PLC18V8Z Series

### PAL DEVICE TO PLC18V8Z OUTPUT PIN CONFIGURATION CROSS REFERENCE

| PIN<br>NO. | PLC<br>18V8Z        | 16L8<br>16H8<br>16P8<br>16P8 | 16R4<br>16RP4 | 16R6<br>16RP6 | 16R8<br>16RP8 | 16L2<br>16H2<br>16P2 | 14L4<br>14H4<br>14P4 | 12L6<br>12H6<br>12P6 | 10L8<br>10H8<br>10P8 |

|------------|---------------------|------------------------------|---------------|---------------|---------------|----------------------|----------------------|----------------------|----------------------|

| 1          | I <sub>0</sub> /CLK |                              | CLK           | CLK           | CLK           | I                    | 1                    | ī                    |                      |

| 19         | F7                  | В                            | В             | В             | D             | 1                    | ı                    | ī                    | 0                    |

| 18         | F6                  | В                            | В             | D             | ٥             | - I                  | ı                    | 0                    | 0                    |

| 17         | F5                  | В                            | D             | D             | D             | _                    | 0                    | 0                    | 0                    |

| 16         | F4                  | В                            | D             | D             | D             | 0                    | 0                    | 0                    | 0                    |

| 15         | F3                  | В                            | D             | D             | D             | 0                    | 0                    | 0                    | 0                    |

| 14         | F2                  | В                            | D             | D             | D             | 1                    | 0                    | 0                    | 0                    |

| 13         | F1                  | В                            | В             | D             | D             | ī                    | _                    | 0                    | 0                    |

| 12         | F0                  | В                            | В             | В             | D             | ī                    | 1                    | 1                    | 0                    |

| 11         | lg/OE               | 1                            | OE            | ŌΕ            | ŌE            | -                    | ī                    |                      |                      |

The Philips Semiconductors state-of-the-art Floating-Gate CMOS EPROM process yields bipolar equivalent performance at less than one-quarter the power consumption. The erasable nature of the EPROM process enables Philips Semiconductors to functionally test the devices prior to shipment to the customer.

Additionally, this allows Philips Semiconductors to extensively stress test, as well as ensure the threshold voltage of each individual EPROM cell. 100% programming yield is subsequently guaranteed.

### **FUNCTIONAL DIAGRAM**

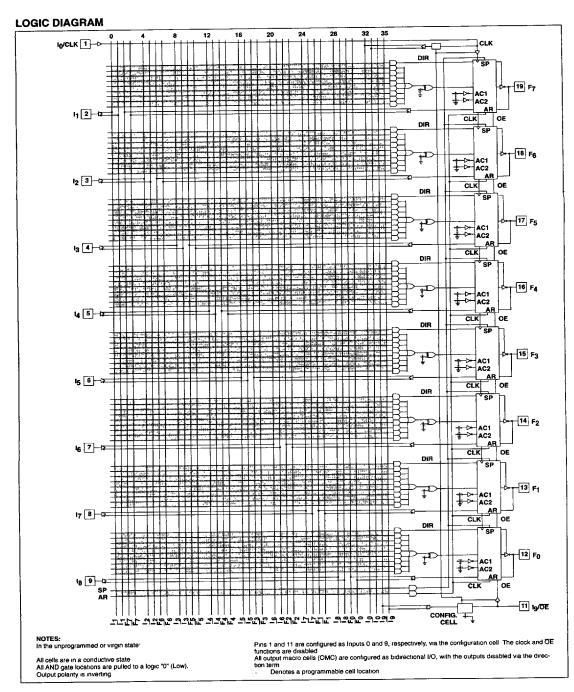

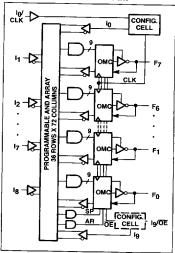

The PLC18V8Z series devices have 8 individually programmable Output Macro Cells The 74 AND inputs (or product terms) from the programmable AND array are connected to the 8 OMCs in groups of 9. Eight of the AND terms are dedicated to logic functions; the ninth is for asynchronous direction control, which enables/disables the respective bidirectional I/O pin. Two product terms are dedicated for the Synchronous Preset and Asynchronous Reset functions.

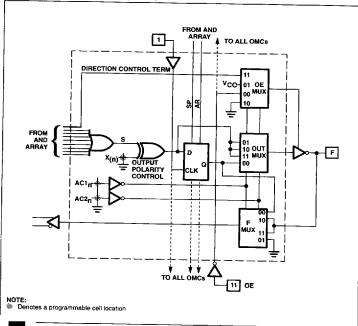

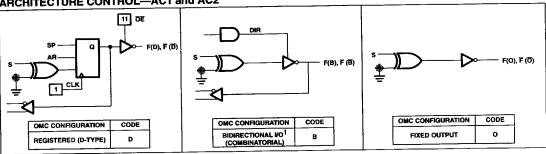

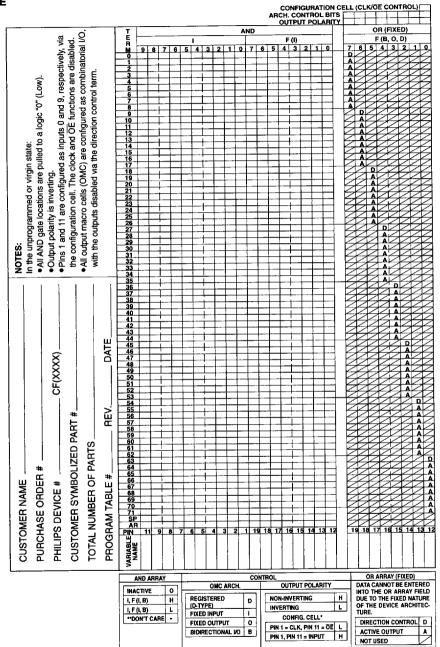

Each OMC can be independently programmed via 16 architecture control bits. AC1<sub>n</sub> and AC2<sub>n</sub> (one pair per macro cell). Similarly, each OMC has a programmable output polarity control bit (Xn). By configuring the pair of architecture control bits according to the configuration cell table, 4 different configurations may be implemented. Note that the configuration cell is automatically programmed based on the OMC configuration.

### **DESIGN SECURITY**

The PLC18V8Z series devices have a programmable security fuse that controls the access to the data programmed in the device. By using this programmable feature, proprietary designs implemented in the device cannot be copied or retrieved

## THE OUTPUT MACRO CELL (OMC) OUTPUT MACRO CELL (OMC)

7110826 0085819 TT5

November 15, 1993

## PLC18V8Z Series

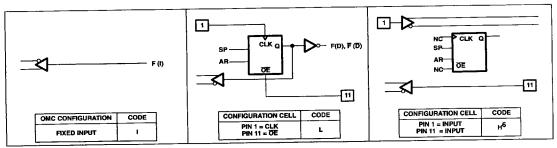

### **CONFIGURATION CELL**

A single configuration cell controls the functions of Pins 1 and 11. Refer to Functional Diagram. When the configuration cell is programmed, Pin 1 is a dedicated clock and Pin 11 is dedicated for output enable. When the configuration cell is unprogrammed, Pins 1 and 11 are both dedicated inputs. Note that the output enable for all registered OMCs is common-from Pin 11 only. Output enable control of the bidirectional I/O OMCs is provided from the AND array via the direction product term.

If any one OMC is configured as registered, the configuration cell will be automatically configured (via the design software) to ensure that the clock and output enable functions are enabled on Pins 1 and 11,

respectively. If none of the OMCs are registered, the configuration cell will be programmed such that Pins 1 and 11 are dedicated inputs. The programming codes are as follows:

| Pin 1 = CLK, Pin 11 = OE | L |

|--------------------------|---|

| Pin 1 and Pin 11 = Input | н |

| FUNCTION                            | CONTR            | OL CELL CONFIGURA | COMMENTS     |                                                                                            |

|-------------------------------------|------------------|-------------------|--------------|--------------------------------------------------------------------------------------------|

|                                     | AC1 <sub>1</sub> | AC2 <sub>N</sub>  | CONFIG. CELL |                                                                                            |

| Registered mode                     | Programmed       | Programmed        | Programmed   | Dedicated clock from Pin 1. OE Control for all registerd OMCs from Pin 11 only.            |

| Bidirectional I/O mode <sup>1</sup> | Unprogrammed     | Unprogrammed      | Unprogrammed | Pins 1 and 11 are dedicated inputs. 3-State control from AND array only.                   |

| Fixed input mode                    | Unprogrammed     | Programmed        | Unprogrammed | Pins 1 and 11 are dedicated inputs.                                                        |

| Fixed output mode                   | Programmed       | Unprogrammed      | Unprogrammed | Pins 1 and 11 are dedicated inputs. The feedback path (via F <sub>MUX</sub> ) is disabled. |

### NOTE:

## ARCHITECTURE CONTROL—AC1 and AC2

### NOTE:

A factory shipped unprogrammed device is configured such that:

- This is the initial unprogrammed state. All cells are in a conductive state.

- All AND gates are pulled to a logic "0" (Low).

- Output polarity is inverting.

- Pins 1 and 11 are configured as inputs 0 and 9. The clock and OE functions are disabled.

- 5. All Output Macro Cells (OMCs) are configured as bidirectional I/O, with the outputs disabled via the direction term.

- This configuration cannot be used if any OMCs are configured as registered (Code = D). The configuration cell will be automatically configured to ensure that the clock and output enable functions are enabled on Pins 1 and 11, respectively, if any one OMC is programmed as registered.

## 7110826 0085820 717 📟

November 15, 1993

This is the virgin state as shipped from the factory.

## PLC18V8Z Series

### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| SYMBOL           | PARAMETER                   | RATINGS                       | UNIT            |

|------------------|-----------------------------|-------------------------------|-----------------|

| Vcc              | Supply voltage              | -0.5 to +7                    | V <sub>DC</sub> |

| V <sub>CC</sub>  | Operating supply voltage    | 4.5 to 5.5                    | V <sub>DC</sub> |

| V <sub>IN</sub>  | Input voltage               | -0.5 to V <sub>CC</sub> + 0.5 | V <sub>DC</sub> |

| V <sub>OUT</sub> | Output voltage              | -0.5 to V <sub>CC</sub> + 0.5 | V <sub>DC</sub> |

| I <sub>IN</sub>  | Input currents              | -10 to +10                    | mA              |

| Гоит             | Output currents             | +24                           | mA              |

| T <sub>amb</sub> | Operating temperature range | -55 to +125                   | - °C            |

| T <sub>STG</sub> | Storage temperature range   | -65 to +150                   | <del>-</del> c  |

## DC ELECTRICAL CHARACTERISTICS

-55°C ≤ T<sub>amb</sub> ≤ +125°C, 4.5V ≤ V<sub>CC</sub> ≤ 5.5V

| SYMBOL                       | PARAMETER                                            | TEST CONDITION                                                             |          | UNIT     |                       |           |

|------------------------------|------------------------------------------------------|----------------------------------------------------------------------------|----------|----------|-----------------------|-----------|

|                              |                                                      |                                                                            | MIN      | TYP2     | MAX                   | 1         |

| input voita                  | ige                                                  |                                                                            |          |          |                       | ·——       |

| V <sub>IL</sub>              | Low                                                  | V <sub>CC</sub> = MIN                                                      | -0.3     |          | 0.8                   | l v       |

| ViH                          | High                                                 | V <sub>CC</sub> = MAX                                                      | 2.0      |          | V <sub>CC</sub> + 0.3 | V         |

| Output vol                   | tage <sup>3</sup>                                    |                                                                            | <u> </u> |          | 1 .00 . 0.0           | <u> </u>  |

| V <sub>OL</sub>              | Low                                                  | V <sub>CC</sub> = MAX, I <sub>OL</sub> = 24mA                              |          |          | 0.500                 | l v       |

| V <sub>OH</sub>              | High                                                 | V <sub>CC</sub> = MAX, I <sub>OH</sub> = -3.2mA                            | 2.4      |          | 1                     | l ·       |

| Input curre                  | ent                                                  |                                                                            | •        | <u> </u> |                       | <u> </u>  |

| I <sub>IL</sub>              | Low <sup>6</sup>                                     | V <sub>IN</sub> = GND                                                      | Ti Ti    |          | -10                   | μА        |

| I <sub>IH</sub>              | High                                                 | $V_{IN} = V_{CC}$                                                          |          |          | 10                    | μА        |

| Output cur                   | rent                                                 |                                                                            |          |          |                       | μΛ        |

| I <sub>O(OFF)</sub>          | Hi-Z state                                           | V <sub>OUT</sub> = V <sub>CC</sub><br>V <sub>OUT</sub> = GND               |          |          | 10<br>-10             | μA<br>μA  |

| los                          | Short-circuit <sup>4</sup>                           | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = GND                              |          |          | -130                  | mΑ        |

| Icc                          | V <sub>CC</sub> supply current (Standby)             | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0 or V <sub>CC</sub> <sup>7</sup> |          |          | 250                   | μА        |

| I <sub>CC</sub> /f           | V <sub>CC</sub> supply current (Active) <sup>5</sup> | V <sub>CC</sub> ≃ MAX                                                      |          |          | 2.0                   | mA/MHz    |

| Capacitano                   | e                                                    |                                                                            | <u> </u> | L        | 2.0                   | THE VIVIE |

| C <sub>1</sub> 12            | Input                                                | V <sub>CC</sub> = 5V<br>V <sub>IN</sub> = 2.0V                             |          | 12       | 17                    | pF        |

| C <sub>B</sub> <sup>12</sup> | 1/0                                                  | V <sub>B</sub> = 2.0V                                                      |          | 15       | 20                    | pF        |

7110826 0085821 653 📟

November 15, 1993

## PLC18V8Z Series

## AC ELECTRICAL CHARACTERISTICS

| SYMBOL              | ≤+125°C, 4.5V ≤ V <sub>CC</sub> ≤ 5.                                        | FROM                 | то                   | TEST CONDITION8                                            |                     | LIMITS   |     | UNIT         |

|---------------------|-----------------------------------------------------------------------------|----------------------|----------------------|------------------------------------------------------------|---------------------|----------|-----|--------------|

| 01111000            |                                                                             | 1                    |                      | R <sub>1</sub> (W)                                         | C <sub>L</sub> (pF) | MIN      | MAX | <u></u>      |

| ulse width          | 1                                                                           |                      |                      |                                                            |                     |          | ,   |              |

| t <sub>CKP</sub>    | Clock period<br>(Minimum t <sub>IS</sub> + t <sub>CKO</sub> ) <sup>13</sup> | CLK+                 | CLK+                 | 200                                                        | 50                  | 40       |     | ns           |

| t <sub>СКН</sub>    | Clock width High                                                            | CLK+                 | CLK -                | 200                                                        | 50                  | 15       |     | ns           |

| tokl                | Clock width Low                                                             | CLK -                | CLK+                 | 200                                                        | 50                  | 15       | ļ   | ns           |

| ARW <sup>11</sup>   | Async reset pulse width                                                     | l ±, F±              | 1∓, F∓               |                                                            |                     | 40       | ns  | <u>L</u>     |

| lold time           |                                                                             |                      |                      |                                                            |                     |          |     |              |

| tıH                 | Input or feedback<br>data hold time                                         | CLK+                 | Input ±              | 200                                                        | 50                  | 0        |     | ns           |

| Setup time          |                                                                             |                      |                      |                                                            |                     |          |     | τ            |

| t <sub>IS</sub>     | Input or feedback data setup time                                           | I ±, F±              | CLK+                 | 200                                                        | 50                  | 22       | l   | ns           |

| ropagatio           | on delay                                                                    |                      |                      |                                                            |                     |          |     |              |

| t <sub>PD</sub>     | Delay from input to active output                                           | l±, F±               | F±                   | 200                                                        | 50                  |          | 30  | ns           |

| t <sub>CKO</sub>    | Clock High to output valid access Time                                      | CLK+                 | F±                   | 200                                                        | 50                  |          | 18  | ns           |

| t <sub>OE1</sub> 10 | Product term enable to<br>outputs off                                       | I ±, F±              | F±                   | Active-High R = 1.5k<br>Active-Low R = 550                 | 50                  |          | 30  | ns           |

| t <sub>OD1</sub> 9  | Product term disable to outputs off                                         | l ±, F±              | F±                   | From $V_{OH}R = \infty$<br>From $V_{OL}R = 200$            | 5                   |          | 30  | пѕ           |

| t <sub>OD2</sub> 9  | Pin 11 output disable<br>High to outputs off                                | OE -                 | F±                   | From V <sub>OH</sub> R = ∞<br>From V <sub>OL</sub> R = 200 | 5                   |          | 25  | ns           |

| t <sub>OE2</sub> 10 | Pin 11 output enable to active output                                       | OE+                  | F±                   | Active-High R = 1.5k<br>Active-Low R = 550                 | 50                  |          | 25  | ns           |

| tano <sup>11</sup>  | Async reset delay                                                           | I±, F±               | F+                   |                                                            |                     |          | 40  | ns           |

| t <sub>ARR</sub> 11 | Async reset recovery time                                                   | l ±, F±              | CLK+                 |                                                            |                     | 30       |     | ns           |

| t <sub>SPR</sub> 11 | Sync preset recovery time                                                   | l±, F±               | CLK+                 |                                                            |                     | 30       |     | ns           |

| tppg11              | Power-up reset                                                              | V <sub>CC</sub> +    | F+                   |                                                            |                     | <u> </u> | 40  | ns           |

| Frequency           | y of operation                                                              |                      |                      |                                                            |                     |          |     | <del> </del> |

| f <sub>MAX</sub>    | Maximum frequency                                                           | I/(t <sub>iS</sub> + | t <sub>СКО</sub> )13 | 200                                                        | 50                  |          | 25  | MH           |

- 1. Stresses above those listed may cause malfunction or permanent damage to the device. This is a stress rating only. Functional operation at these or any other condition above those indicated in the operational and programming specification of the device is not implied.

- All typical values are at V<sub>CC</sub> = 5V, T<sub>amb</sub> = +25°C. 3. All voltage values are with respect to network ground terminal.

- 4. Duration of short-circuit should not exceed one second. Test one at a time.

- Measured with all outputs switching.

- 6. I<sub>IL</sub> for Pin 1 ( $I_0$ /CLK) is  $\pm$  10 $\mu$ A with  $V_{IN}$  = 0.4V.

- VIN includes CLK and OE if applicable 7.

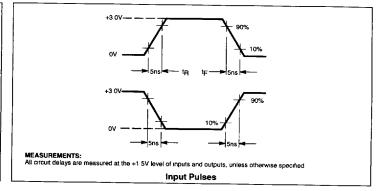

- 8. Refer also to AC Test Conditions. (Test Load Circuit)

- For 3-State output; output enable times are tested with  $C_L = 50pF$  to the 1.5V level, and  $S_1$  is open for high-impedance to High tests and closed for high-impedance to Low tests. Output disable times are tested with  $C_L = 5pF$ . High-to-High impedance to Low tests. Output disable times are tested with  $C_L = 5pF$ . High-to-High impedance to an output voltage of  $V_T = (V_{OH} - 0.5V)$  with  $S_1$  open, and Low-to-High Impedance tests are made to the  $V_T$  ( $V_{OL} + 0.5V$ ) with  $S_1$  closed.

- 10. Resistor values of 1.5k and 550ohm provide 3-State levels of 1.0V and 2.0V, respectively. Output timing measurements are to 1.5V level.

- Not tested, guaranteed by design/characterization.

- 12. Only tested for initial qualification, or after any design changes which may effect this parameter.

- 13. This parameter is guaranteed by testing the individual parameters specified in this equation.

November 15, 1993

## PLC18V8Z Series

### **AC TEST CONDITIONS**

FROM OUTPUT

(BX, FX)

UNDER TEST

TEST POINT

R<sub>2</sub> = 390Ω

\*C<sub>L</sub> INCLUDES JIG AND PROBE TOTAL

CAPACITANCE

Test Load Circuit

### **VOLTAGE WAVEFORMS**

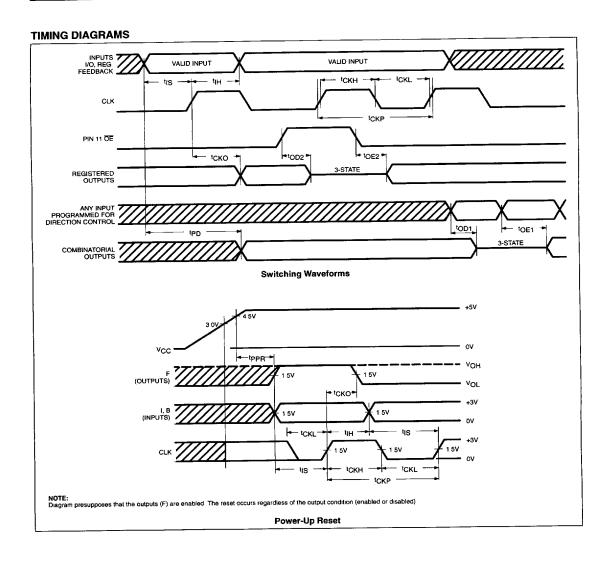

### **POWER-UP RESET**

In order to facilitate state machine design and testing, a power-up reset function has been incorporated in the PLC18V8Z. All internal registers will reset to active-Low (logical "0") after a specified period of time (tppa).

Therefore, any OMC that has been configured as a registered output will always produce an active-High on the associated output pin because of the inverted output buffer. The internal feedback (Q) of a

registered OMC will also be set Low. The programmed polanty of OMC will not affect the active-High output condition during a system power-up condition.

## PLC18V8Z Series

7110826 0085824 362 🚥

November 15, 1993

### PLC18V8Z Series

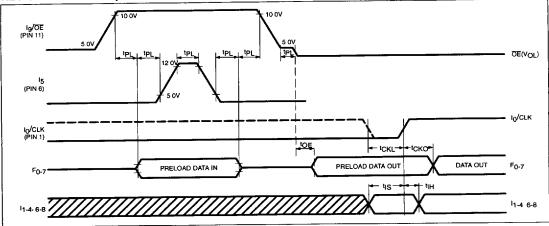

# REGISTER PRELOAD FUNCTION (DIAGNOSTIC MODE ONLY)

In order to facilitate the testing of state machine/controller designs, a diagnostic mode register preload feature has been incorporated into the PLC18V8Z series device. This feature enables the user to load

the registers with predetermined states while a super voltage is applied to Pins 11 and 6 ( $l_9/OE$  and  $l_5$ ). (See diagram for timing and sequence.)

To read the data out, Pins 11 and 6 must be returned to normal TTL levels. The outputs,  $F_{0-7}$ , must be enabled in order to read data

out. The Q outputs of the registers will reflect data in as input via F0-F7 during preload. Subsequently, the register Q output via the feedback path will reflect the data in as input via F0-F7.

Refer to the voltage waveform for timing and voltage references.  $t_{PL} = 10 \mu sec.$

## PLC18V8Z Series

### REGISTER PRELOAD (DIAGNOSTIC MODE)

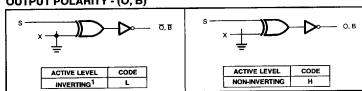

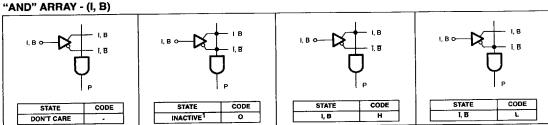

### LOGIC PROGRAMMING

The PLC18V8Z can be programmed by means of Logic Programming equipment.

With Logic programming, the AND/OR/Ex-OR gate input connections necessary to implement the desired logic function are coded directly from logic equations using the Program Table. Similarly, various OMC configurations are implemented by programming the Architecture Control bits AC1 and AC2. Note that the configuration cell is automatically programmed based on the OMC configuration.

In this table, the logic state of variables I, P and B associated with each Sum Term S is assigned a symbol which results in the proper fusing pattern of corresponding link pairs, defined as follows:

## **OUTPUT POLARITY - (O, B)**

1. A factory shipped unprogrammed device is configured such that all cells are in a conductive state.

## 7110826 0085826 135 💳

November 15, 1993

## PLC18V8Z Series

# ERASURE CHARACTERISTICS (For Quartz Window Packages Only)

The erasure characteristics of the PLC18V8Z Series devices are such that erasure begins to occur upon exposure to light with wavelengths shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lighting could erase a typical PLC18V8Z in approximately three years, while it would take approximately one week to cause erasure when exposed to direct sunlight. If the

PLC18V8Z is to be exposed to these types of lighting conditions for extended periods of time, opaque labels should be placed over the window to prevent unintentional erasure.

The recommended erasure procedure for the PLC18V8Z is exposure to shortwave ultraviolet light which has a wavelength of 2537 Angstroms (Å). The integrated dose (i.e., UV intensity × exposure time) for erasure should be a minimum of 15Wsec/cm². The erasure time with this dosage is approximately 30 to 35 minutes

using an ultraviolet lamp with a 12,00µW/cm² power rating. The device should be placed within one inch of the lamp tubes during erasure. The maximum integrated dose a CMOS EPLD can be exposed to without damage is 7258Wsec/cm²). Exposure of these CMOS EPLDs to high intensity UV light for longer periods may cause permanent damage.

The maximum number of guaranteed erase/write cycles is 50. Data retention exceeds 20 years.

### **PROGRAMMING**

The PLC18V8Z35/I is programmable on conventional programmers for 20-pin PAL devices. Refer to the following charts for qualified manufacturers of programmers and software tools:

| PROGRAMMER MANUFACTURER                                                                                                | PROGRAMMER MODEL                                                                                                               | FAMILY/PINOUT CODES |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------|

| DATA I/O CORPORATION<br>10525 WILLOWS ROAD, N.E.<br>P.O. BOX 97046<br>REDMOND, WASHINGTON 98073-9746<br>(800) 247-5700 | System 29B, LogicPak™ 303A-011A; V09 (DIL) 303A-011B; V04 (PLCC)  UNISITE 40/48 V2.5 (DIL) Chipsite (PLCC) - TBA  MODEL 60 TBA | 86/4F               |

| STAG MICROSYSTEMS, INC.<br>1600 WYATT DRIVE, SUITE 3<br>SANTA CLARA, CALIFORNIA 95054<br>(408) 988-1118                | ZL30/30A PROGRAMMER REV. 30A34 (DIL) 30A001 Adaptor (PLCC)  PPZ PROGRAMMER TBA                                                 | 12/205              |

| SOFTWARE MANUFACTURER                                                                                                           | DEVELOPMENT SYSTEM                   |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| PHILIPS SEMICONDUCTORS COMPANY<br>811 EAST ARQUES AVENUE<br>P.O. BOX 3409<br>SUNNYVALE, CALIFORNIA 94088-3409<br>(408) 991-2000 | AMAZE SOFTWARE<br>REV. 1.8 and LATER |

| DATA I/O<br>10525 WILLOWS ROAD, N.E.<br>P.O. BOX 97046<br>REDMOND, WASHINGTON 98073-9746<br>(800) 247-5700                      | ABEL™ SOFTWARE                       |

| LOGICAL DEVICES, INC.<br>1201 NORTHWEST 65TH PLACE<br>FORT LAUDERDALE, FLORIDA 33309<br>(800) 331-7766                          | CUPL™ SOFTWARE                       |

November 15, 1993

1039

7110826 0085827 071

## PLC18V8Z Series

### **PROGRAM TABLE**

<sup>\*</sup> THE CONFIGURATION CELL IS AUTOMATICALLY PROGRAMMED BASED ON THE OMC ARCHITECTURE. \*\* FOR SP, AR: "-" IS NOT ALLOWED.