| LTR<br>A         |                           |              |      |                          |              |                                                  |              |              |            | RE\          | /ISK       | ONS          |                                                                          |              |     |      |      |           |      |      |     |                      |     |     |          |

|------------------|---------------------------|--------------|------|--------------------------|--------------|--------------------------------------------------|--------------|--------------|------------|--------------|------------|--------------|--------------------------------------------------------------------------|--------------|-----|------|------|-----------|------|------|-----|----------------------|-----|-----|----------|

| Α                |                           | -            |      |                          |              | 0                                                | ESC          | RIPT         | ЮN         |              |            |              |                                                                          |              |     |      |      | DATE      | (YR- | MO-D | A)  | AP                   | PRO | VED |          |

|                  | Change<br>Delete<br>Conve | e qr         | oup  | utline<br>C pro<br>litar | gramm        | nabi                                             | lity         | tes          | st a       | Q.<br>nd a   | Ad<br>dd   | d ca<br>marg | se<br>in                                                                 | out1<br>test | ine | Υ.   |      | 86 SEP 23 |      |      |     | M.d. Fye<br>M.d. Fye |     |     |          |

| В                | Add v                     | endo<br>numb | r CA | GE 34                    | 335.<br>oria | Add                                              | d de<br>ange | vice<br>s th | ty<br>nrou | pe (<br>ghou | )2.<br>it. | Cha          | nge                                                                      | dra          | win | g    |      | 88 1      | YAY  | 26   |     | M.                   | 1.  | G   | <u>'</u> |

|                  |                           |              |      |                          |              |                                                  |              |              |            |              |            |              |                                                                          |              |     |      |      |           |      |      |     |                      |     |     |          |

|                  | RRE                       | N            | C    | AGE                      | EC           | OE                                               | E            | 67           | 26         | 8            |            |              |                                                                          |              | ,   |      |      |           |      |      |     |                      |     |     | Γ        |

| REV<br>SHEET     |                           | 4            | 4    |                          | ₩            | _                                                | _            |              | _          |              |            | $\vdash$     |                                                                          |              |     |      |      |           | _    |      |     |                      |     | H   | F        |

| REV              |                           | $\dashv$     |      | -                        | <del>-</del> | ├                                                | -            |              | -          |              | Н          | $\vdash$     |                                                                          |              |     |      | _    |           |      | _    |     |                      | -   | ┢   | r        |

| SHEET            |                           |              | 十    | ╅                        | 1            | <del>                                     </del> | ┢            |              |            | -            |            |              |                                                                          |              |     |      |      |           |      |      |     |                      |     |     | H        |

| REV ST           | TATLIS                    | 丁            | REV  |                          | В            | В                                                | В            | В            | В          | В            | В          | В            | В                                                                        | В            | В   | В    | В    | В         | В    | В    | В   | В                    | В   | В   | ı        |

|                  |                           |              | SHE  | ET .                     | 1            | 2                                                | 3            | 4            | 5          | 6            | 7          | 8            | 9                                                                        | 10           | 11  | 12   | 13   | 14        | 15   | 16   | 17  | 18                   | 19  | 20  | L        |

| OF SH            | J/A                       |              |      |                          |              | PARE                                             |              | 2            | Pi         | <u></u>      |            |              | DEFENSE ELECTRONICS SUPPLY CENTER                                        |              |     |      |      | -         |      |      |     |                      |     |     |          |

| OF SHI<br>PMIC N |                           |              |      |                          |              | 200                                              |              |              |            | _            |            |              | MICROCIRCUITS, N-CHANNEL, MOS 8-BIT MICROCOMPUTER WITH 32 K-BIT UVEPROM, |              |     |      | 444  | CER       | ITER |      |     |                      |     |     |          |

| PMIC N           | NDA<br>MILIT              | ΓAF          | ľY   | D                        | СН           | Ra                                               | D BY         |              | lm         | mi           | <u>~</u>   |              | M.M.                                                                     | ICRO         | CIR | CUIT | S. 1 | N-CH      | IANN | EL,  | MOS | 8-B                  | IT  |     |          |

\* U.S. GOVERNMENT PRINTING OFFICE: 1987 — 748-129/60912

5962-E917

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

# 1. SCOPE

1.1~Scope. This drawing describes device requirements for class B microcircuits in accordance with  $1.\overline{2.1}$  of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

1.2 Part number. The complete part number shall be as shown in the following example:

1.2.1 Device types. The device types shall identify the circuit function as follows:

| Device type | Generic number | Circuit function                          | Frequency    |

|-------------|----------------|-------------------------------------------|--------------|

| 01          | 8751H-8        | 8-bit microcomputer with 32 K-bit UVEPROM | 8.0 MHz max  |

| 02          | 8751H          | 8-bit microcomputer with 32 K-bit UVEPROM | 12.0 MHz max |

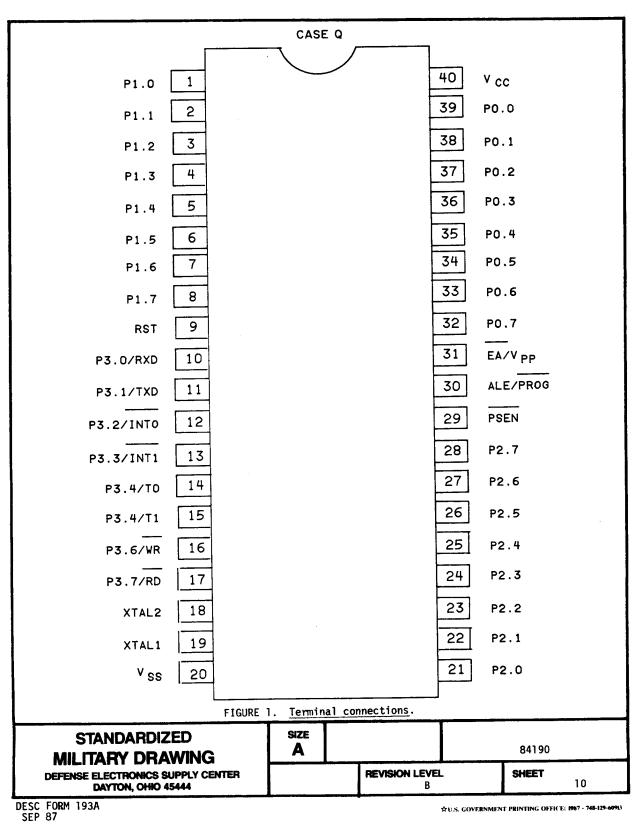

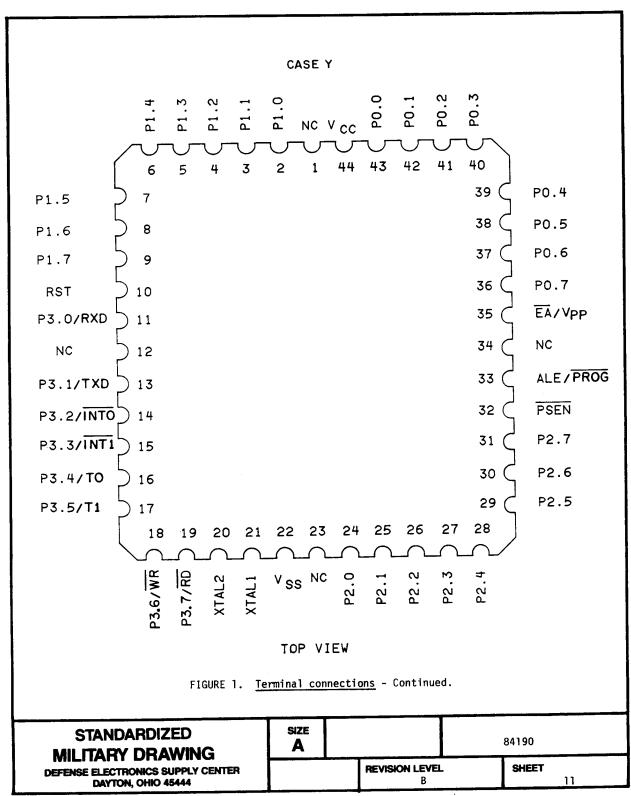

1.2.2 <u>Case outlines</u>. The case outlines shall be as designated in appendix C of MIL-M-38510, and as follows:

# Outline letter Case outline 1/ Q D-5 (40-lead, 2.096" x .620" x .225"), dual-in-line package Y C-5 (44-terminal, .662" x .662" x .120"), square chip

1.3 Absolute maximum ratings.

carrier package

1.4 Recommended operating conditions.

| Supply voltage (V <sub>CC</sub> )        | 4.5 V dc to 5.5 V dc |

|------------------------------------------|----------------------|

| Program voltage (Vpp)                    | 21.0 V dc ±0.5 V dc  |

| Case operating temperature range $(T_C)$ | -55°C to +125°C      |

$\overline{1/}$  Lid shall be transparent to permit ultraviolet light erasure.  $\overline{2/}$  All voltages referenced to  $V_{SS}$ .

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 84190   |

|------------------------------------------------------|-----------|----------------|---------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 2 |

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987—549-098

#### 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MIL ITARY

MIL-M-38510 - Microcircuits, General Specification for.

STANDARD

MILITARY

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

- 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

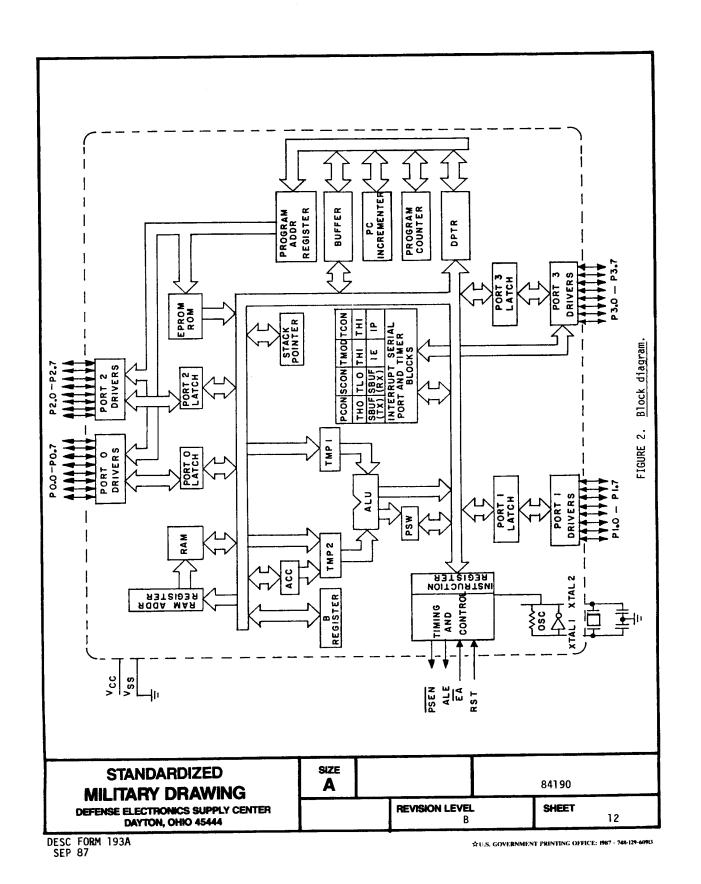

- 3.2.2 Block diagram. The block diagram shall be as specified on figure 2.

- 3.2.3 Programmed EPROM device. The requirements for supplying programmed EPROM devices are not part of this drawing.

- 3.2.4 Case outlines. The case outlines shall be in accordance with 1.2.2.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.5 herein.

- 3.5 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.5. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

| STANDARDIZED MILITARY DRAWING                           | SIZE<br>A |                       |   | 84190 |   |

|---------------------------------------------------------|-----------|-----------------------|---|-------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |           | <b>REVISION LEVEL</b> | • | SHEET | 3 |

DESC FORM 193A

|                                                                    |                           | 0                                                                                                            | In            | Cmarra # | 1 2 2 4 -                 | Unit            |

|--------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------|---------------|----------|---------------------------|-----------------|

| Test                                                               | Symbol<br> <br>           | Conditions $-55^{\circ}C \leq T_C \leq +125^{\circ}$ $V_{CC} = 5.0 \text{ V} \pm 10\%$ unless otherwise spec | C  type       | Group A  | Limits<br> <br>  Min   Ma | Ť               |

| Input low voltage                                                  | VIL                       | <br>                                                                                                         | A11           | 1, 2, 3  | 0.                        | 7   V           |

| Input high voltage<br>(except XTAL2, RST)                          | I<br>IV <sub>IH</sub>     | l                                                                                                            | A11           | 1, 2, 3  | 2.2                       | ٧               |

| Input high voltage to XTAL2, RST                                   | V <sub>IH1</sub>          | IXTAL1 = V <sub>SS</sub>                                                                                     | A11           | 1, 2, 3  | 2.5                       | V               |

| Output low voltage ports 1, 2, 3                                   | V <sub>OL</sub>           | I <sub>OL</sub> = 1.2 mA                                                                                     | A11           | 1, 2, 3  | 0.                        | 45 V            |

| Output low voltage port O<br>ALE, PSEN                             | v <sub>OL1</sub>          | I <sub>OL</sub> = 2.8 mA<br>I <sub>OL</sub> = 2.4 mA                                                         | All           | 1, 2, 3  | 0.                        | 60 V<br>45      |

| Output high voltage ports 1, 2, 3                                  | V <sub>OH</sub>           | <br> I <sub>OH</sub> = -60 μA                                                                                | All           | 1, 2, 3  | 2.4                       | ٧               |

| Output high voltage<br>port O (in external<br>bus mode), ALE, PSEN | <br> v <sub>OH1</sub><br> | <br>  I <sub>OH</sub> = -300 μA<br>                                                                          | A11           | 1, 2, 3  | 2.4                       | ٧               |

| Logical O input current<br>P1, P2, P3                              | IIL                       | V <sub>IN</sub> = 0.45 V                                                                                     | All           | 1, 2, 3  | -50                       | 0 μΑ            |

| Logical O input current<br>to EA/Vpp                               | I <sub>IL1</sub>          | <br> V <sub>IN</sub> = 0.45 V<br>                                                                            | A11           | 1, 2, 3  | -1                        | 5   mA          |

| Logical O input current<br>to XTAL2                                | IIIL2                     | <br> XTAL1                                                                                                   | V A11         | 1, 2, 3  | -4                        | .5  mA          |

| Input leakage current<br>to port 0                                 | ILI                       | <br> 0.45 < V <sub>IN</sub> < V <sub>CC</sub>                                                                | A11           | 1, 2, 3  | ±12                       | 5 μΑ            |

| Logical input current<br>to EA/Vpp                                 | II <sub>IH</sub>          | <br> V <sub>IN</sub> = 2.4 V<br>                                                                             | A11           | 1, 2, 3  | 50                        | 0 μΑ            |

| Input current to RST/V <sub>PD</sub> to activate reset             | I <sub>IH1</sub>          | V <sub>IN</sub> < (V <sub>CC</sub> - 1.5 V)                                                                  | A11           | 1, 2, 3  | 50                        | 0 μΑ            |

| Power supply current                                               | IICC                      | <br> All outputs disconnected<br> EA = V <sub>CC</sub>                                                       | , A11         | 1, 2, 3  | <br>  27<br>              | 5   mA<br> <br> |

| Capacitance of I/O buffers                                         | C1/0                      | <br> fc = 1 MHz, T <sub>C</sub> = +25°C<br> See 4.3.1c                                                       | A11           | 4        | 1                         | 0   pF          |

| See footnotes at end of tab                                        | le.                       |                                                                                                              |               |          |                           |                 |

| STANDARDIZE                                                        |                           | SIZE<br>A                                                                                                    |               |          |                           |                 |

| MILITARY DRAV                                                      |                           | <u> </u>                                                                                                     | EVISION LEVEL |          | HEET                      |                 |

★ U. S. GOVERNMENT PRINTING OFFICE: 1988—549-90

| TAE                                          | BLE I.            | Electrical p                                  | erformance                            | chara        | cter           | istics -     | Conti          | nued.            |                                    |                                      |                |

|----------------------------------------------|-------------------|-----------------------------------------------|---------------------------------------|--------------|----------------|--------------|----------------|------------------|------------------------------------|--------------------------------------|----------------|

|                                              | <br> Symbol       | Cond                                          | litions                               | 1            | )e-            | <br> Group A | Lin            | nits             | Limit                              | ts <u>2</u> /                        | Unit           |

| lest                                         | 1                 | -55°C < T<br>  V <sub>CC</sub> = 5            | [ <sub>C</sub> < +125°C<br>5.0 V ±10% | i lv<br>It   | vice           |              | Min            | Max              | Min                                | Max                                  | · j            |

| Oscillator period                            | tCLCL             | unless_other<br> <br> C <sub>L</sub> (Port 0, |                                       |              | 01<br>02       | 9,10,11      | 125<br>83      | 286<br>286       | tCLCL                              | tCLCL                                | ns             |

| High time <u>1</u> / <u>3</u> /              | t <sub>CHCX</sub> | 100 pF<br> C <sub>L</sub> (all othe           |                                       | 17           | NT-            |              | 20             |                  | 20                                 | İ                                    | <u> </u>       |

| Low time $1/3/$                              | tclcx             | -<br> f <sub>MAX</sub> = 8 MHz                |                                       | - 1          |                | ! !          | 20             |                  | 20                                 |                                      | 1              |

| Rise time <u>1/3/</u> Fall time 1/3/         | tCLCH             | <br> f <sub>MAX</sub> = 12 MH                 | lz device 0                           | 2            |                |              |                | 20               | <u> </u>                           | 20                                   | -              |

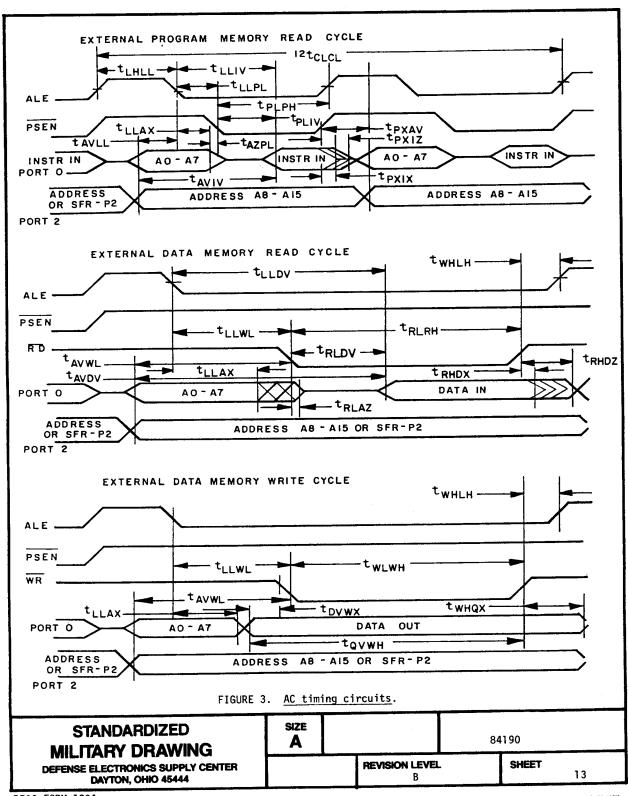

| Fall time $1/3/$ ALE pulse width             | t <sub>CHCL</sub> | See figures                                   | 3 and 4 4                             | /  <br>      | 01             | i<br>i       | 195            | i<br>I           | <br> 2t <sub>CLCL</sub><br>  -55   | i                                    | -<br>          |

| Address valid to ALE                         | ItAVLL            | į<br>Į                                        |                                       | <u>[</u>     | 02<br>01       | <br>         | 112<br>70      |                  | -55<br> tclcl<br>  -55             | <u> </u>                             | -              |

| Address hold after ALE                       | t <sub>LLAX</sub> |                                               |                                       |              | 02<br>01<br>02 |              | 28<br>75<br>33 |                  | -55<br> t <sub>CLCL</sub><br>  -50 | !<br>!                               | -              |

| ALE to valid instr in                        | tLLIV             |                                               |                                       | į-           | 01             |              |                | 335<br>168       | 1                                  | 4tcLCL                               | į              |

| ALE to PSEN                                  | t <sub>LLPL</sub> | 1                                             |                                       | <u> </u>     | 01<br>02       |              | 85<br>43       |                  | t <sub>CLCL</sub><br>-40           | 1                                    | _              |

| PSEN pulse width                             | t <sub>PLPH</sub> |                                               |                                       | -            | 01<br>02<br>01 |              | 300<br>175     | 210              | 3tclcL<br>  -75                    | Store                                | -              |

| PSEN to valid instr in                       | tpLIV             | i<br>I                                        |                                       |              | 02<br>A11      | i i          | 0              | 85               | i<br>  0                           | 3tclcL<br>  -165                     | į<br>Į         |

| Input instr hold after PSEN                  | <br>              | <br>                                          |                                       | <u> </u>     | -01            | [            |                |                  |                                    | <br>                                 | -              |

| Input instr float after $\frac{1}{PSEN}$     | tpXIZ             | <br>                                          |                                       | <br> -<br>   | 01<br>02       | <br>         |                | 90<br>  48<br>   | <u> </u>                           | tclcl<br>  -35<br>                   |                |

| PSEN to address valid Address to valid instr | t <sub>PXAV</sub> | []<br>                                        |                                       | <br> -<br> - | 01<br>02<br>01 | ]<br>]<br>   | 100<br>58      | 460              | t <sub>CLCL</sub><br>-25           | <br> <br> 5tclcL<br>  -165           | -              |

| in 1/                                        | tAZPL             | .                                             |                                       | [7           | 02<br>A11      |              | 0              | 252              | 1 0                                | -165                                 | -              |

| Address float to PSEN  RD pulse width        | tRLRH             | <br>                                          |                                       | <u> </u> -   | 01<br>02       |              | 650<br>400     |                  | 6t <sub>CLCL</sub>                 |                                      | <u>-</u>       |

| WR pulse width                               | tWLWH             | ]<br>[                                        |                                       | [            | 01<br>02       | <u> </u>     | 650<br>400     |                  | 6t <sub>CLCL</sub><br>  -100       | 1                                    | - <br>-        |

| Address hold after ALE                       | <u> </u>          | <br>                                          |                                       | ļ            | 01<br>02<br>01 | <br>         | 75<br>33       | 440              | tcLCL<br>  -50                     | Ster er                              | -¦             |

| RD to valid data in                          | t <sub>RHDX</sub> | -                                             |                                       | j-<br>17     | 02<br>Al 1     |              | 0              | 232              | i<br>I 0                           | 5t <sub>CLCL</sub><br>  -185<br>     | - <br>-        |

| Data hold after RD                           | ItRHDZ            |                                               |                                       | <u> </u>     | 01             | !<br>!       |                | <br>  165        | ļ                                  | <br> 2t <sub>CLCL</sub>              | -              |

| Data float after RD<br>ALE to valid data in  | tLLDV             | -                                             |                                       | -            | 02<br>01<br>02 | <br> <br>    |                | 82<br>830<br>496 | <del> </del>                       | -85<br> 8t <sub>CLCL</sub><br>  -170 | -              |

| Address to valid data                        | t <sub>AVDV</sub> |                                               |                                       | j            | 01<br>02       | i<br>I       |                | 940              |                                    | 9tclcL<br>  -185                     | - <u>i</u><br> |

| See footnotes at end of                      |                   | <del></del>                                   | T                                     |              |                |              | 1              |                  |                                    |                                      |                |

| STANDARI<br>MILITARY DI                      |                   | NG                                            | SIZE<br>A                             |              |                |              |                |                  | 84190                              |                                      |                |

| DEFENSE ELECTRONIC<br>DAYTON, OH             | S SUPPL           |                                               |                                       |              | REV            | ISION LEVE   | L              |                  | SHEET                              | 5                                    |                |

# U. S. GOVERNMENT PRINTING OFFICE: 1988--549-90-

| Test                               | Symbol            | Conditions                                                    | De-           | Group A | Lin        | nits       | Limit                            | s <u>2</u> /               | Unit     |

|------------------------------------|-------------------|---------------------------------------------------------------|---------------|---------|------------|------------|----------------------------------|----------------------------|----------|

|                                    |                   | -55°C < T <sub>C</sub> < +125°C                               | lvice<br>type | sub-    | Min        | Max        | Min                              | Max                        |          |

| ALE to WR or RD                    | t <sub>LLWL</sub> | <br> <br>                                                     | 01            | 9,10,11 | 310<br>185 | 440<br>315 | <br> 3t <sub>CLCL</sub><br>  -65 | 3tcLcL<br>  +65            | ns       |

| ddress to WR or RD                 | tAVWL             | <br> C <sub>L</sub> (Port O, ALE, <del>PSEN</del> ) =         | 01 02         | !       | 355<br>188 |            | 4tclcL<br>-145                   |                            |          |

| Data valid to WR                   | t <sub>QVWX</sub> | 100 pF<br> C <sub>L</sub> (all others) = 80 pF<br>            | 01<br>02<br>I |         | 0          |            | t <sub>CLCL</sub><br>  -85<br>   |                            | !<br>!   |

| ata setup to WR high               | tQWH              | See figures 3 and 4 4/<br> f <sub>MAX</sub> = 8 MHz device OT | 01            | <br>    | 800<br>508 |            | 7tcLcL<br>-75                    |                            |          |

|                                    | tuuny             | ''''<br> f <sub>MAX</sub> = 12 MHz device 02                  | 01            |         | 60<br>18   |            | t <sub>CLCL</sub>                |                            | <u> </u> |

| $\frac{1}{D}$ low to address float | tRLAZ             | ······                                                        | A11           |         | 0          |            | 0<br>                            |                            | ]        |

| D or WR high to ALE                | twHLH             | <br>                                                          | 01            |         | 60<br>18   | 190<br>148 | t <sub>CLCL</sub>                | <sup>t</sup> çլçլ<br>  +65 |          |

- 1/ Tested only initially and after any design changes.

- 2/ Variable oscillator equations provided for design purposes.

- 3/ Required external clock drive characteristics (XTAL2).

- 4/ AC testing: inputs are driven at 2.4 V for a logic "1" and 0.45 V for a logic "0". Timing measurements are made at 2.0 V for a logic "1" and 0.8 V for a logic "0".

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.8 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.9 <u>Processing EPROMS</u>. All testing requirements and quality assurance provisions herein shall be satisfied by the manufacturer prior to delivery.

- 3.9.1 Erasure of EPROMS. When specified, devices shall be erased in accordance with the procedures and characteristics specified in 4.4.

- 3.9.2 Programmability of EPROMS. When specified, devices shall be programmed to the specified pattern using the procedures and characteristics specified in 4.5 and table III.

- 3.9.3 <u>Verification of erasure of programmability of EPROMS</u>. When specified, devices shall be verified as either programmed to the specified pattern or erased. As a minimum, verification shall consist of performing a functional test (subgroup 7) to verify that all bits are in the proper state. Any bit that does not verify to be in the proper state shall constitute a device failure, and shall be removed from the lot.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                         | 84190   |  |

|------------------------------------------------------|-----------|-------------------------|---------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | <b>REVISION LEVEL</b> B | SHEET 6 |  |

# U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

#### 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- Test condition A or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- c. A data retention stress test shall be included as part of the screening procedure and shall consist of the following steps.

- (1) Program greater than 95 percent of the bit locations, including the slowest programming cell (see 3.9.2). The remaining cells shall provide a worst case speed pattern.

- (2) Bake, unbiased, for 72 hours at +140°C to screen for data retention lifetime.

- (3) Perform a margin test using Vm = +5.9 V at  $+25^{\circ}C$  using loose timing (i.e.,  $T_{ACC} = 1 \mu s$ ).

- (4) Perform dynamic burn-in (see 4.2a).

- (5) Margin at Vm = 5.9 V.

- (6) Perform electrical tests (see 4.2).

- (7) Erase (see 3.9.1), except devices submitted for groups A, B, C, and D testing.

- (8) Verify erasure (see 3.9.3).

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-SID-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 shall be measured only for the initial test and after process or design changes which may affect capacitance.

- d. All devices selected for testing shall have the EPROM programmed with a checkerboard pattern or equivalent. After completion of all testing, the devices shall be erased and verified (except devices submitted for group C and D testing).

- e. Subgroups 7 and 8 shall consist of verifying the EPROM pattern specified and the instruction set. The instruction set forms a part of the vendors test tape and shall be maintained and available from the approved source of supply.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                     | 84190            |  |  |

|------------------------------------------------------|-----------|---------------------|------------------|--|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>B | <b>SHEET</b> 7 7 |  |  |

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1967-549-096

| TABLE | II. | Electrical | test | requirements. |

|-------|-----|------------|------|---------------|

|-------|-----|------------|------|---------------|

| MIL-STD-883 test requirements                                              | Subgroups     (per method     5005, table I)     1/2/3/4/ |

|----------------------------------------------------------------------------|-----------------------------------------------------------|

| Interim electrical parameters<br>  (method 5004)                           |                                                           |

| Final electrical test parameters<br>  (method 5004)                        | 1*, 2, 3, 7, 9  <br>                                      |

| [Group A test requirements   (method 5005)                                 | 1, 2, 3, 7, 8, 1<br>9, 10, 11                             |

| Groups C and D end-point electrical parameters (method 5005)               | 2, 8A, 10<br>or<br>  1, 2, 3                              |

| Additional electrical subgroups<br>  for group C periodic<br>  inspections |                                                           |

(\*) Indicates PDA applies to subgroup 1.

Any or all subgroup may be combined when using a high speed tester.

3/ Subgroups 7 and 8 shall consist of verifying the

EPROM pattern specified and the instruction set. 4/ For all electrical tests, the device shall be programmed to the pattern specified (see 4.3.1d).

## 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition A or D.

- (2)  $T_A = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- (4) All devices selected for testing shall be programmed with a checkerboard pattern or equivalent. After completion of all testing, the devices shall be erased and verified.

- 4.4 Erasing procedure. The device is erased by exposure to high intensity short wave ultraviolet light at a wavelength of 253.7 mm. The recommended integrated dose (i.e., UV intensity X exposure time) is  $15 \text{ W-s/cm}^2$ . An example of an ultraviolet source which can erase the device in 30 minutes is the Model S52 short wave ultraviolet lamp. The lamp should be used without short wave filters and the EPROM should be placed about 1 inch away from the lamp tubes. After erasures, all bits are in the high state.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                         | 84190     |

|------------------------------------------------------------------------------------|-----------|-------------------------|-----------|

|                                                                                    |           | <b>REVISION LEVEL</b> B | SHEET 8 × |

DESC FORM 193A **SEP 87**

☆ U.S. GOVERNMENT PRINTING OFFICE: 1967—549-096

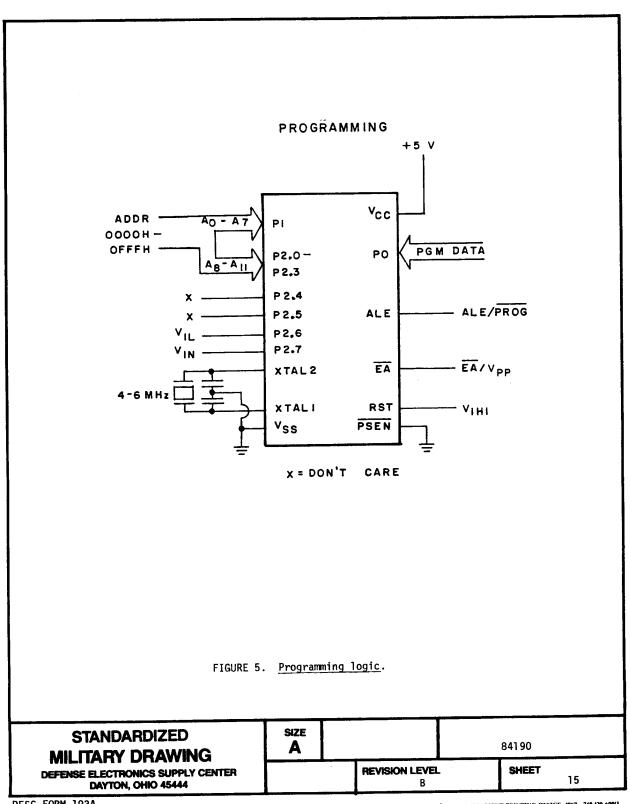

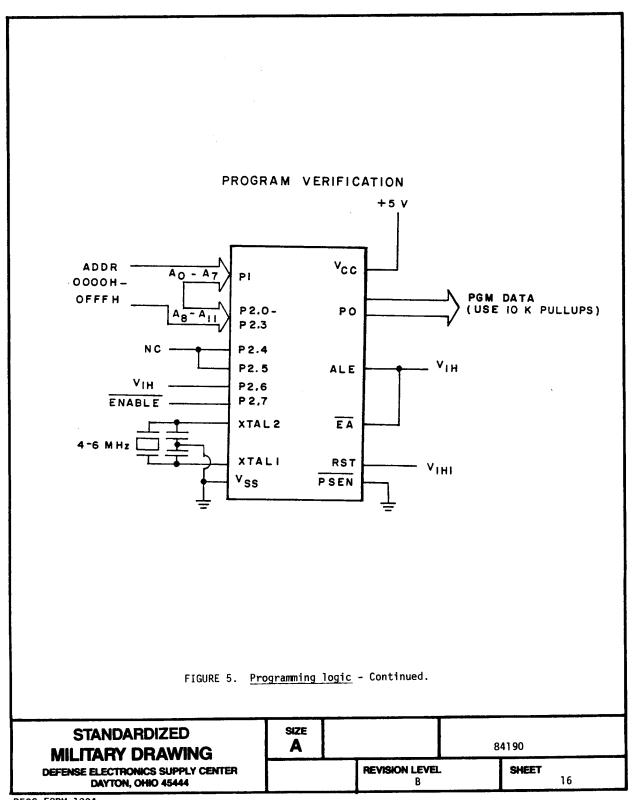

- 4.5 Programming procedures for method A. The programming characteristics in table III and the following procedures shall be used for programming the device.

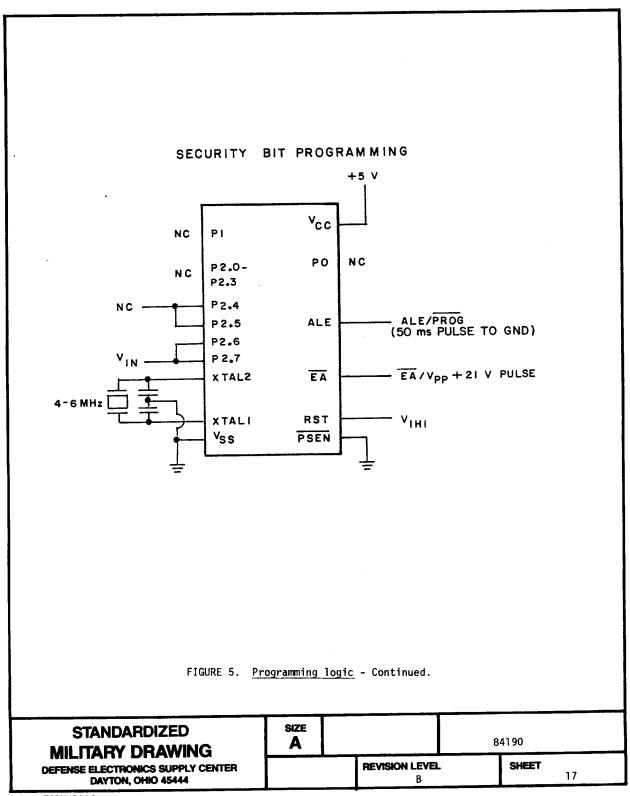

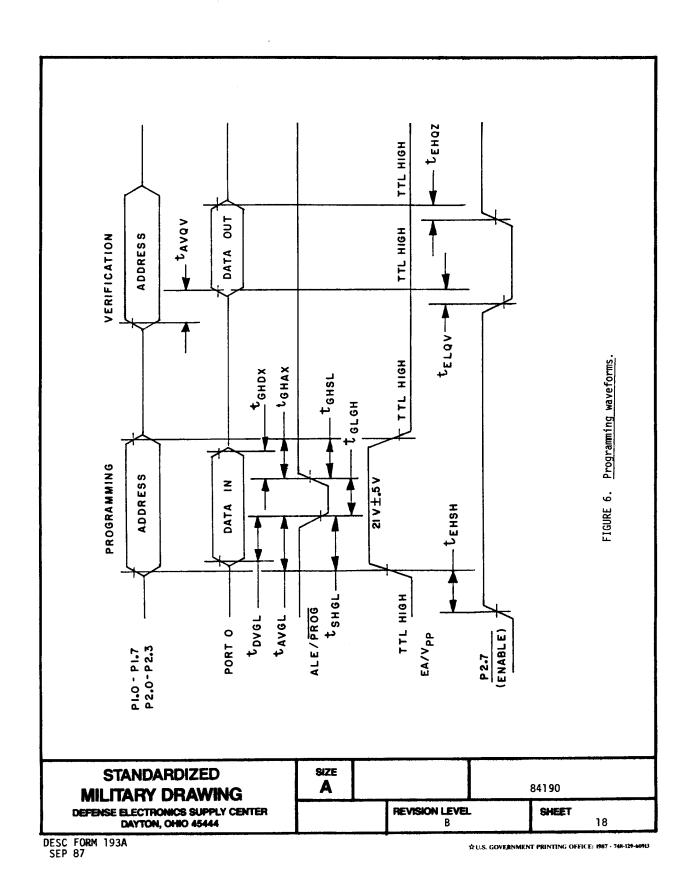

- a. Connect the device in the electrical configuration (see figure 5) for programming the waveforms of figure 6 and programming characteristics of table III shall apply.

- b. Initially and after each erasure, all bits are in the high "H" state. Information is introduced by selectively programming "L" into the desired bit locations. A programmed "L" can be changed to an "H" by ultraviolet light erasure (see 4.4).

TABLE III. Programming characteristics.

| Parameter                                     | Symbol              | Conditions                   | Min                 | Max                 | Units |

|-----------------------------------------------|---------------------|------------------------------|---------------------|---------------------|-------|

| Programming supply voltage                    | Vpp                 | V <sub>CC</sub> = 5.0 V ±10% | 20.5                | 21.5                | V     |

| Programming current                           | Ірр                 | T <sub>C</sub> = +25°C       |                     | 30                  | mA    |

| Oscillator frequency                          | 1/t <sub>CLCL</sub> | †                            | 1 4                 | 6                   | MHz   |

| Address setup to PROG                         | tavgL               | †                            | 48t <sub>CLCL</sub> |                     | ns    |

| Address hold after PROG                       | tGHAX               | †<br>                        | 48t <sub>CLCL</sub> |                     | ns    |

| Data setup to PROG                            | †DVGL               | Ť                            | 48t <sub>CLCL</sub> |                     | ns    |

| Data hold after PROG                          | tGHDX               | †                            | 48t <sub>CLCL</sub> |                     | ns    |

| ENABLE high to Vpp                            | tensh               | Ţ                            | 48t <sub>CLCL</sub> |                     | ns    |

| Vpp setup to PROG                             | t <sub>SHGL</sub>   | 1                            | 10                  |                     | μS    |

| V <sub>PP</sub> hold after PROG               | t <sub>GHSL</sub>   | <u> </u>                     | 10                  |                     | μS    |

| PROG width                                    | tGLGH               | †                            | 45                  | 55                  | ms    |

| Address to data valid                         | t <sub>AVQV</sub>   | †                            |                     | 48t <sub>CLCL</sub> | ns    |

| FURNIT to date walled                         | t <sub>ELQV</sub>   | †                            | †                   | 48t <sub>CLCL</sub> | ns    |

| ENABLE to data valid  Data float after ENABLE | t <sub>EHQZ</sub>   | †                            | 0                   | 48t <sub>CLCL</sub> | ns    |

# 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

## 6. NOTES

6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

| STANDARDIZED  MILITARY DRAWING  DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |               | 84190   |

|--------------------------------------------------------------------------------------|-----------|---------------|---------|

|                                                                                      |           | REVISION LEVE | SHEET 9 |

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904

Powered by ICminer.com Electronic-Library Service CopyRight 2003

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

- 6.4 Symbols, definitions, and functional descriptions. The symbols, definitions, and functional description for this device shall be as follows:

- Port 0 is an 8-bit open drain bidirectional I/O port. It is also the multiplexed low-order address and data bus during accesses to external memory. It also receives the instruction bytes during EPROM programming, and outputs instruction bytes during program verification. (External pullups are required during program verification.) Port 0 can sink (and in bus operations can source) eight LS TTL inputs.

- Port 1 is an 8-bit bidirectional I/O port with internal pullups. It receives the low-order address byte during EPROM programming and program verification. Port 1 can sink/source four LS TTL inputs.

- Port 2 is an 8-bit bidirectional I/O port with internal pullups. It emits the high-order address byte during accesses to external memory. It also receives the high-order address bits during EPROM programming and program verification. Port 2 can sink/source four LS TTL inputs.

- Port 3 Port 3 is an 8-bit bidirectional I/O port with internal pullups. It also serves the functions of various special features as listed below:

| Port pin | Alternate function                     |

|----------|----------------------------------------|

| P3.0     | RXD (serial input port)                |

| P3.1     | TXD (serial output port)               |

| P3.2     | INTO (external interrupt)              |

| P3.3     | INTI (external interrupt)              |

| P3.4     | TO (timer/counter 0 external input)    |

| P3.5     | T1 (timer/counter 1 external input)    |

| P3.6     | WR (external data memory write strobe) |

| P3.7     | RD (external data memory read strobe)  |

Port 3 can sink/source four LS TTL inputs

RST A high on this pin for two machine cycles while the oscillator is running resets the device. A small external pulldown resistor (8.2 k $\Omega$ ) from RST to VSS permits power-on reset when a capacitor (10  $\mu$ F) is also connected from this pin to VCC.

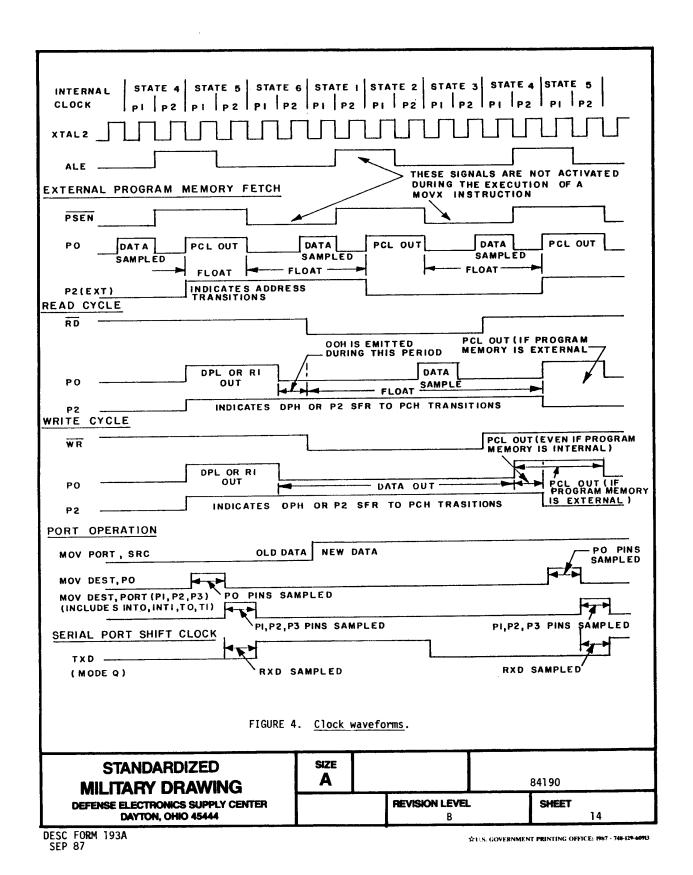

ALE/PROG Address latch enable output for latching the low byte of the address during accesses to external memory. ALE is activated at a constant rate of 1/6 the oscillator frequency except during an external data memory access at which time one ALE pulse is skipped. ALE can sink/source 8 LS TTL inputs. This pin is also the program pulse input (PROG) during EPROM programming.

Program store enable output is the read strobe to external program memory. PSEN is activated twice each machine cycle during fetches from external program memory. (However, even when executing out of external program memory two activations of PSEN are skipped during each access to external data memory). PSEN is not activated during fetches from internal program memory. PSEN can sink/source 8 LS TTL inputs.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                       | 84190           |

|------------------------------------------------------------------------------------|-----------|-----------------------|-----------------|

|                                                                                    |           | <b>REVISION LEVEL</b> | <b>SHEET</b> 19 |

DESC FORM 193A SEP 87

**PSEN**

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987--549-098

EA/Vpp

When  $\overline{\text{EA}}$  is held high, the device executes out of internal program memory (unless the program counter exceeds OFFFH). When  $\overline{\text{EA}}$  is held low, the device executes only out of external program memory. This pin also receives the 21 V programming supply voltage (Vpp) during EPROM programming. This pin should not be floated during normal operation.

XTAL1

Input to the inverting amplifier that forms the oscillator, XTAL1 should be grounded when an external oscillator is used.

XTAL2

Output of the inverting amplifier that forms the oscillator, and input to the internal clock generator. Receives the external oscillator signal when an external oscillator is used.

6.5 Approved sources of supply. Approved sources of supply are listed herein. Additional sources will be added as they become available. The vendors listed herein have agreed to this drawing and a certificate of compliance (see 3.5) has been submitted to DESC-ECS.

| Military drawing<br>part number | Vendor<br>  CAGE<br>  number | Vendor<br>similar part<br>number <u>1</u> / | Program<br>  method |

|---------------------------------|------------------------------|---------------------------------------------|---------------------|

| 8419001QX<br>8419001QX          | 34649<br>34335               | MD8751H-8/B<br>8751H-8/BQA                  | A                   |

| 8419001YX                       | 34649                        | MR8751H-8/B                                 | A                   |

| 8419002QX                       | 34335                        | 8751H/BQA                                   | A                   |

1/ Caution: Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

| Vendor CAGE<br>number | vendor name<br>and address  |

|-----------------------|-----------------------------|

| 34649                 | Intel Corporation           |

|                       | 5000 W. Williams Field Road |

|                       | Chandler, AZ 85224          |

| 34335                 | Advanced Micro Devices      |

|                       | 901 Thompson Place          |

|                       | P. O. Box 3453              |

|                       | Sunnyvale, CA 94088         |

STANDARDIZED

MILITARY DRAWING

DEPENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

84190

REVISION LEVEL

B

SHEET 20

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1967-549-096

012680 \_ \_ \_