## GT- 32090 **System Controller** For i960JX Processors

Preliminary, Rev. 2.0 March 1996

**FEATURES**

NOTE: Always contact Galileo Technology for possible updates before starting a design.

- Integrated system controller for embedded applica-

- Supports the i960JX family of CPUs

- 16-33MHz bus frequency

- Flexible DRAM controller

- Page mode and EDO DRAMs

- 128MByte address space

- 256K-4M device depth

- 1-4 banks supported directly

- Up to 8 banks supported indirectly

- 32-bit data width

- Non-interleaved

- Different size for each bank

- Zero wait state to first data at 16 and 20MHz

- One wait state to first data and no wait state to burst data at 25MHz

- Two wait states to first data and no wait state to burst data at 33MHz

- Flexible AD bus device controller

- 128MByte address space

- 4 chip selects

- Per bank programmable timing

- Supports several types of standard memories (ROM / Flash / SRAM) and I/O controllers

- External wait support

- 8-, 16-, and 32-bit device (and boot) support

- High performance DMA

- Three independent channels

- Chaining via linked lists of records

- Transfers through a 16-byte internal FIFO or fly-by

- Moves data between SIO, memory, and devices

Packing and unpacking of 8-bit and 16-bit data to/ from the SIO bus into 32-bit data on the CPU bus

- Packing and unpacking from/to the SIO bus concurrent with AD bus activity

- Fixed and round robin programmable priorities

- Simple I/O bus (SIO bus)

- Simple Read/Write bus for glueless interface to low cost peripherals

- 8/16-bit wide bus

- Four chip selects

- Programmable timing

- External wait support

- **PCMCIA**

- Supports two PCMCIA devices directly

- **JTAG**

- 5V

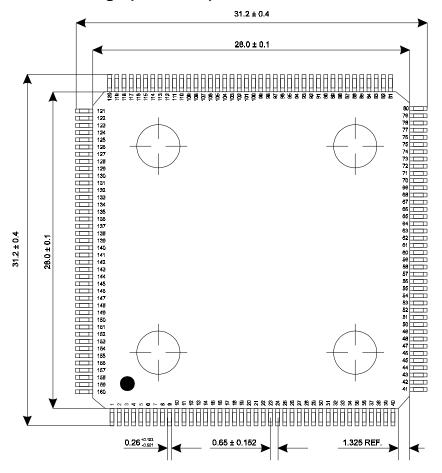

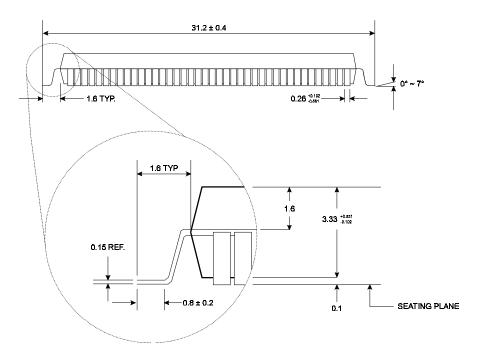

- 160 PQFP

#### **OVERVIEW**

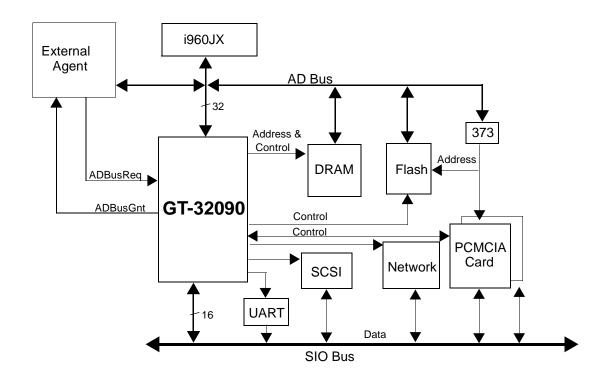

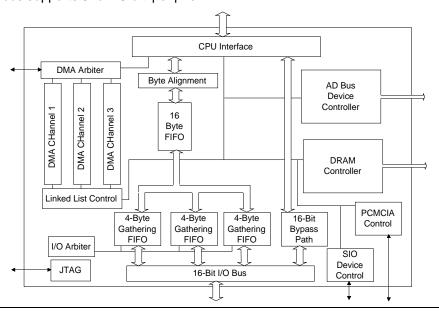

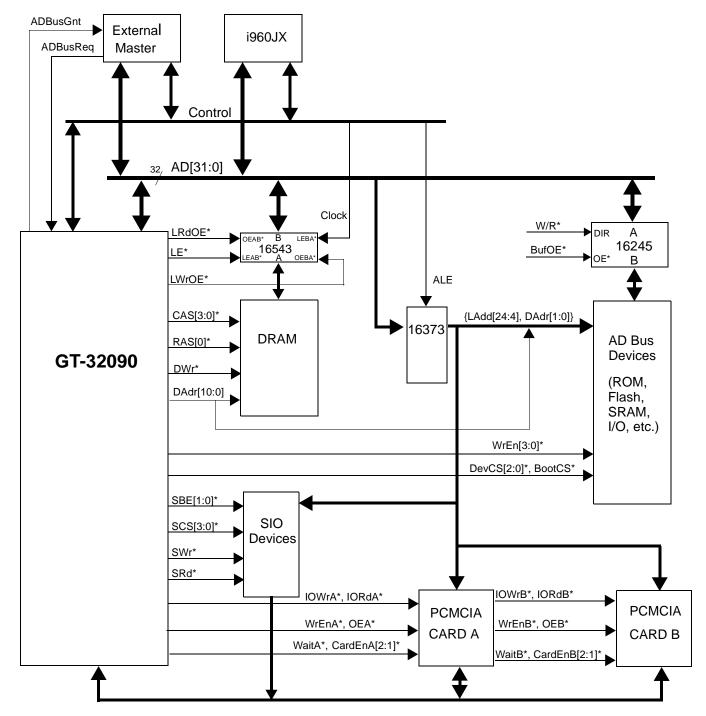

The GT-32090 is a low cost, highly integrated single-chip System Controller for the i960Jx Family. It provides high system performance, while reducing cost, complexity, device count, and board space. The GT-32090 controls two separate and independent buses, the CPU's 16 to 33MHz 32-bit wide address/data bus, and a 16-bit I/O bus. The two buses can work concurrently at different frequencies.

The DRAM Controller supports up to 128MBytes of standard or EDO DRAM. It supports up to four 32-bit wide banks directly, or up to eight banks indirectly, with zero wait states to first data or burst data at 16 and 20MHz. At 25 and 33MHz, there is one wait state and two wait states respectively, to first data, and at both frequencies there are no wait states to burst data. Various refresh and addressing modes are supported.

The Device Controller supports up to 4 devices directly, and includes various programmable timing and wait state mechanisms that can be setup individually for each device. Typical devices supported include DRAM, ROM, Flash, and SRAM, as well as high-performance master peripherals.

The powerful three-channel DMA Controller has data alignment capabilities and sophisticated chaining support via link lists. The DMA can move data between devices on the CPU bus, or between devices on the CPU bus and devices on the I/O bus. DMA transfers can go through an on-board 16-byte FIFO, or directly if in fly-by mode. Packing and unpacking of 8-bit and 16-bit data from/to the I/O bus occurs concurrently with activity on the CPU bus, increasing overall system bandwidth.

The I/O bus is a simple 16-bit read/write bus that interfaces to a large variety of low cost support components like UARTs, SCSI controllers, Ethernet controllers, and other devices. The I/O bus supports 8- or 16-bit peripher-

als, as well as slave DMA and PCMCIA devices. Three 4-byte FIFOs provide efficient support for the gathering of 8-bit or 16-bit data to/from different peripherals, in the endianess chosen by the designer.

The GT-32090 includes a direct interface to two 8-bit or 16-bit PCMCIA slots.

#### REFERENCE DESIGN

Galileo makes available the Galileo-5 Evaluation and Development System, an ISA card which greatly facilitates the development of embedded control systems based on the i960JA/JD/JF Intel processors.

The centerpiece of the system is the GT-32090 System Controller, which integrates most of the core logic necessary in embedded applications.

The Galileo-5 board serves two main objectives:

- a) It allows customers to easily evaluate the performance of a GT-32090 based system, using their own software, as opposed to generic benchmarks.

- b) It greatly facilitates and expedites the development of the final product, since hardware designers can use its design as a reference and software designers can use it to start porting software ahead of their own hardware platform.

The shipping configuration of the Galileo-5 includes a 33MHz i960JA CPU, 4MBytes of DRAM, sockets for 2MBytes of Flash, a 512KByte EPROM, a DUART, Intel MON960 software, and 2 PCMCIA sockets. Jumpers allow customers to evaluate a large variety of system configurations, and expansion connectors allow customer-designed options to be easily interfaced to.

The Galileo-5 can either be used in stand-alone fashion, or it can be plugged directly into an ISA slot of standard personal computers.

## 1 PIN INFORMATION

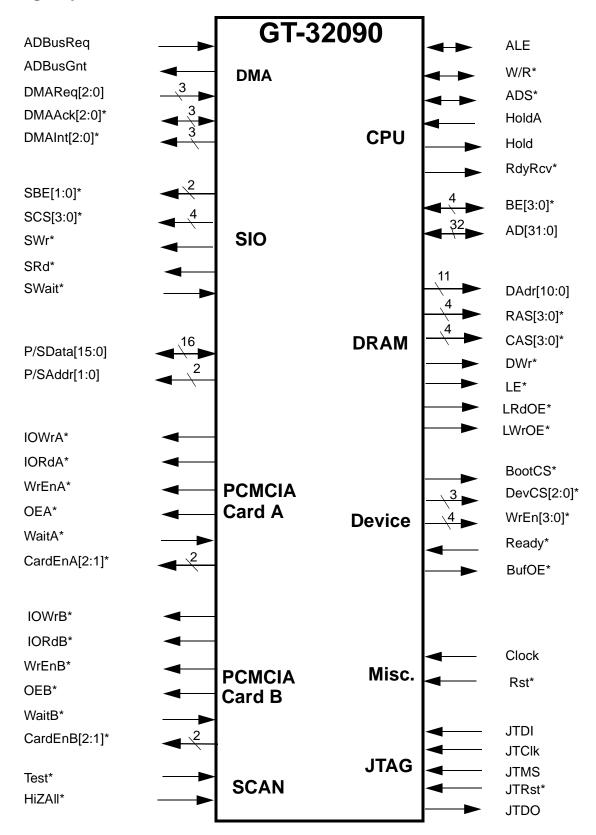

# 1.1 Logic Symbol

# 1.2 Pin Assignment Table

| Pin Name       | Туре | Description                                                                                                                                                                                                                                                          |  |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPU Interface  |      |                                                                                                                                                                                                                                                                      |  |

| AD[31:0]       | I/O  | Address/Data Bus: Multiplexed address and data bus for communication between the processor, devices, DRAM, any external agent, and the GT-32090.                                                                                                                     |  |

| ALE            | I/O  | Address Latch Enable: A strobe for latching the address into the GT-32090 and into external latches for devices, PCMCIA cards, ar SIO bus peripherals. It is an input during a CPU or external agent access, and an output during a DMA access.                      |  |

| ADS*           | I/O  | Address Strobe: Indicates a valid address and the start of a new bus access. It is an input during a CPU or external agent access, and an output during a DMA access.                                                                                                |  |

| BE[3:0]*       | I/O  | <b>Byte Enable:</b> Selects which of the four bytes on the AD bus participate in the current bus access. It is an input during a CPU or external agent access, and an output during a DMA access.                                                                    |  |

| Hold           | 0    | Hold: A request from the GT-32090 to acquire the AD bus.                                                                                                                                                                                                             |  |

| HoldA          | I    | <b>Hold Acknowledge:</b> An indication by the CPU that it has relinquished the AD bus to the GT-32090.                                                                                                                                                               |  |

| RdyRcv*        | 0    | Ready/Recover: Indicates when the data on the AD bus can be sampled or removed. During a device turn-off time, it indicates to the CPU not to drive the address on the AD bus.                                                                                       |  |

| W/R*           | I/O  | <b>Write/Read:</b> Specifies if the access is a write or a read access. It is an input during a CPU or external agent access, and an output during a DMA access. Used also to control the direction of the bi-directional transceiver for the devices on the AD bus. |  |

| DRAM           |      |                                                                                                                                                                                                                                                                      |  |

| DAdr[10:0]     | 0    | DRAM Address/Device Burst Address: Eleven multiplexed address bits to the DRAM. DAdr[1:0] provides the word burst address (same meaning as the CPU's A3, A2 pins) for all 32-bit accesses, be they to DRAM or to devices.                                            |  |

| RAS[3:0]*      | 0    | Row Address Select: Supports four banks of DRAM.                                                                                                                                                                                                                     |  |

| CAS[3:0]*      | 0    | Column Address Select: Supports byte writes to DRAM.                                                                                                                                                                                                                 |  |

| DWr*           | 0    | DRAM Write: Signals a write access to the DRAM.                                                                                                                                                                                                                      |  |

| LE*            | 0    | <b>Latch Enable:</b> When active, latches the DRAM data into external latches.                                                                                                                                                                                       |  |

| LRdOE*         | 0    | Latch Read Output Enable: When active, outputs the data from the DRAM's external latches onto the AD bus.                                                                                                                                                            |  |

| LWrOE*         | 0    | <b>Latch Write Output Enable:</b> When active, outputs the data from the DRAM's external latches onto the DRAM's data pins.                                                                                                                                          |  |

| AD Bus Devices |      |                                                                                                                                                                                                                                                                      |  |

| WrEn[3:0]*     | 0    | Write Enable: Byte write enable to devices on the AD bus.                                                                                                                                                                                                            |  |

| DevCS[2:0]*    | 0    | <b>Device Chip Select</b> : Programmable chip select signals to devices on the AD bus.                                                                                                                                                                               |  |

| BootCS*        | 0    | <b>Boot Chip Select</b> : Programmable chip select signal to the boot device on the AD bus.                                                                                                                                                                          |  |

| Pin Name                       | Туре | Description                                                                                                                                                                                                                                                                                  |  |

|--------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Ready*                         | ı    | <b>Ready</b> : When not active, it extends the access to a device on the AD bus by adding wait cycles.                                                                                                                                                                                       |  |

| BufOE*                         | 0    | <b>Buffer Output Enable:</b> This signal has similar functionality to the DEN* signal of the i960JX, but is active during accesses to devices only. It is active during the data phase of accesses to devices on the AD bus. It is used with the W/R* to control external data transceivers. |  |

| PCMCIA & SIO<br>Shared Signals |      |                                                                                                                                                                                                                                                                                              |  |

| P/SAddr[1:0]                   | 0    | <b>PCMCIA/SIO Address</b> : Byte and half-word addresses for PCMCIA and SIO accesses.                                                                                                                                                                                                        |  |

| P/SData[15:0]                  | I/O  | Data Bus: Shared data bus for SIO and PCMCIA devices.                                                                                                                                                                                                                                        |  |

| SIO Interface                  |      |                                                                                                                                                                                                                                                                                              |  |

| SBE[1:0]*                      | 0    | <b>SIO Byte Enable:</b> Selects which of the two bytes on the SIO bus participates in the current data transfer.                                                                                                                                                                             |  |

| SCS[3:0]*                      | 0    | SIO Chip Select: Chip Select for devices on the SIO bus.                                                                                                                                                                                                                                     |  |

| SRd*                           | 0    | SIO Read: Active during a read from a device on the SIO bus.                                                                                                                                                                                                                                 |  |

| SWr*                           | 0    | SIO Write: Active during a write to a device on the SIO bus.                                                                                                                                                                                                                                 |  |

| SWait*                         | I    | <b>SIO Wait:</b> Extends bus cycle, used to generate wait states by SIO devices.                                                                                                                                                                                                             |  |

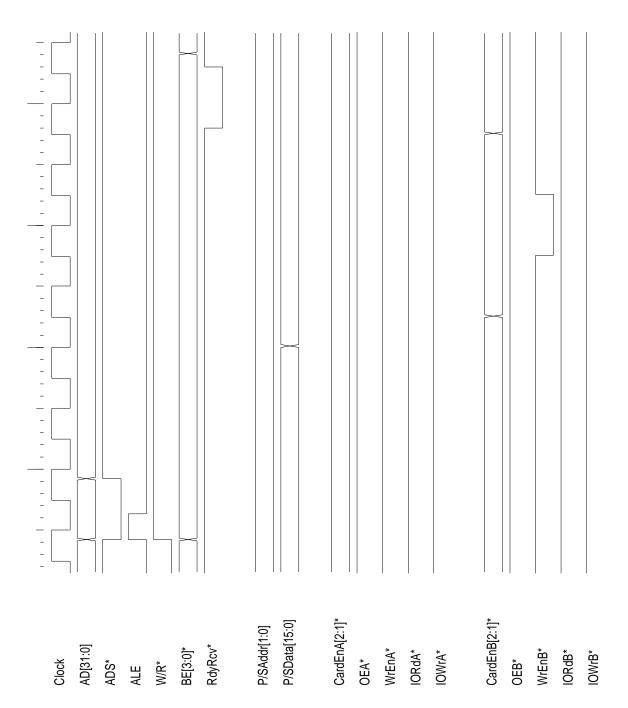

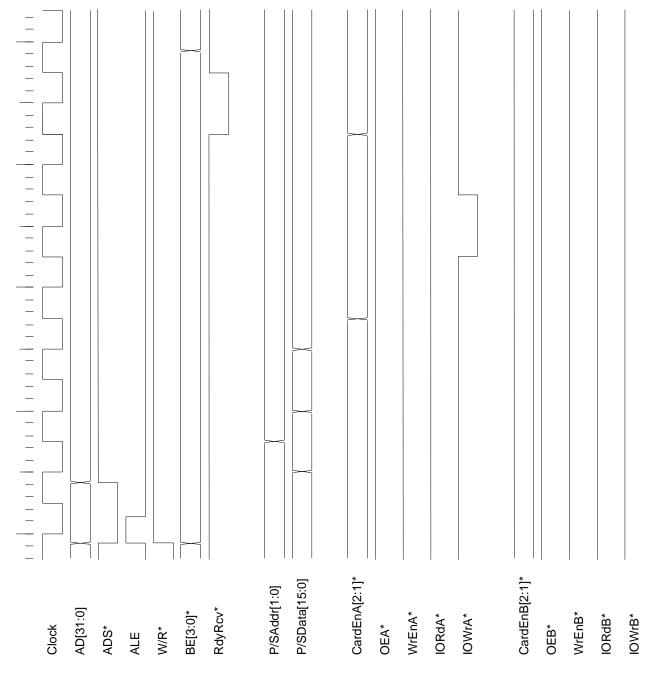

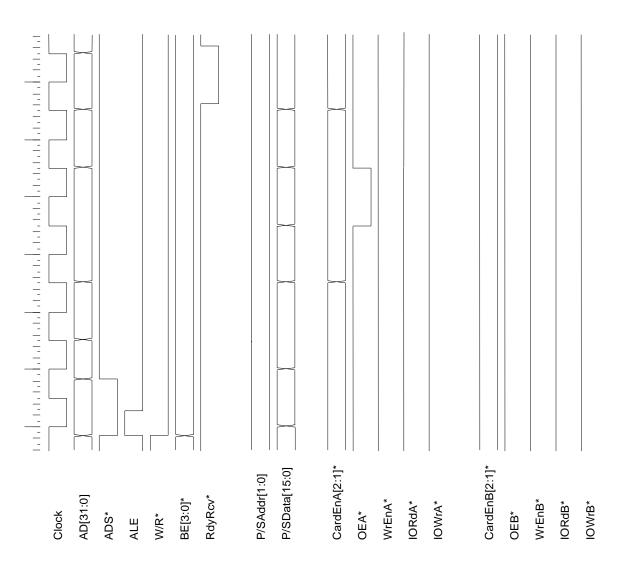

| PCMCIA Card A                  |      |                                                                                                                                                                                                                                                                                              |  |

| CardEnA[2:1]*                  | 0    | <b>Card Enable A:</b> CardEnA[1] enables the even address bytes, and CardEnA[2] enables the odd address bytes.                                                                                                                                                                               |  |

| OEA*                           | 0    | Output Enable A: Controls the output of data from card.                                                                                                                                                                                                                                      |  |

| WaitA*                         | I    | <b>Wait A:</b> Extends bus cycle, used to generate wait states by the card.                                                                                                                                                                                                                  |  |

| WrEnA*                         | 0    | Write Enable A: Indicates write accesses by the GT-32090 to the card.                                                                                                                                                                                                                        |  |

| IORdA*                         | 0    | I/O Read A: Activated to read data from the card's I/O space.                                                                                                                                                                                                                                |  |

| IOWrA*                         | 0    | I/O Write A: Activated to write data to the card's I/O space.                                                                                                                                                                                                                                |  |

| PCMCIA Card B                  |      |                                                                                                                                                                                                                                                                                              |  |

| CardEnB[2:1]*                  | 0    | Card Enable B: CardEnB[1] enables the even address bytes, and CardEnB[2] enables the odd address bytes.                                                                                                                                                                                      |  |

| OEB*                           | 0    | Output Enable B: Controls the output of data from card.                                                                                                                                                                                                                                      |  |

| WaitB*                         | I    | Wait B: Extends bus cycle, used to generate wait states by the card.                                                                                                                                                                                                                         |  |

| WrEnB*                         | 0    | Write Enable B: Indicates write accesses by the GT-32090 to the card.                                                                                                                                                                                                                        |  |

| IORdB*                         | 0    | I/O Read B: Activated to read data from the card's I/O space.                                                                                                                                                                                                                                |  |

| IOWrB*                         | 0    | I/O Write B: Activated to write data to the card's I/O space.                                                                                                                                                                                                                                |  |

| DMA                            |      |                                                                                                                                                                                                                                                                                              |  |

| ADBusReq                       | I    | <b>Bus Request:</b> Signals a request from the external agent to the GT-32090 for acquisition of the AD bus.                                                                                                                                                                                 |  |

| Pin Name      | Туре | Description                                                                                                                                                                         |

|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADBusGnt      | 0    | <b>Bus Grant:</b> Signals that the GT-32090 grants mastership on the AD bus to the external agent.                                                                                  |

| DMAReq[2:0]   | I    | <b>DMA Request:</b> A request for a DMA operation directed at the internal arbiter. When Rst* is asserted these bits are sampled into the Device Address Space register bits [6:4]. |

| DMAAck[2:0]*  | I/O  | DMA Acknowledgement:                                                                                                                                                                |

|               |      | Outputs - The internal arbiter grants a DMA operation to a requesting device.                                                                                                       |

|               |      | Inputs - When Rst* is asserted, these bits are sampled into the Internal Space Decode & Control register bits [5:3].                                                                |

|               |      | These pins are inputs when Rst* is active, until 2 clocks after Rst* is deasserted. They are outputs at all other times.                                                            |

| DMAInt[2:0]*  | 0    | Interrupt: Each interrupt corresponds to one of the DMA channels.                                                                                                                   |

| Miscellaneous |      |                                                                                                                                                                                     |

| Rst*          | 1    | <b>Reset:</b> Resets all internal logic and state machines to a known state.                                                                                                        |

| Clock         | I    | Clock: The input clock to the GT-32090.                                                                                                                                             |

| JTAG          |      |                                                                                                                                                                                     |

| JTDI          | I    | Test Data Input Pin: JTAG's serial input                                                                                                                                            |

| JTMS          | 1    | <b>Test Mode Select:</b> Used to issue serial instructions to the TAP controller's state machine.                                                                                   |

| JTClk         | I    | Test Clock: JTAG's input clock                                                                                                                                                      |

| JTRst*        | I    | Test Reset: Active low asynchronous reset for the TAP controller                                                                                                                    |

| JTDO          | 0    | Test Data Output: JTAG's serial output                                                                                                                                              |

| SCAN          |      |                                                                                                                                                                                     |

| Test*         | I    | <b>Test:</b> When active, indicates that the GT-32090 is in Scan mode.                                                                                                              |

|               |      | 0 - Scan mode                                                                                                                                                                       |

|               |      | 1 - Normal operation                                                                                                                                                                |

| HiZAII*       | I    | <b>Tri-State:</b> When active, the GT-32090 drives all outputs and I/O pins to High impedance.                                                                                      |

|               |      | 0 - Tri-State                                                                                                                                                                       |

|               |      | 1 - Normal operation                                                                                                                                                                |

## 2 FUNCTIONAL DESCRIPTION

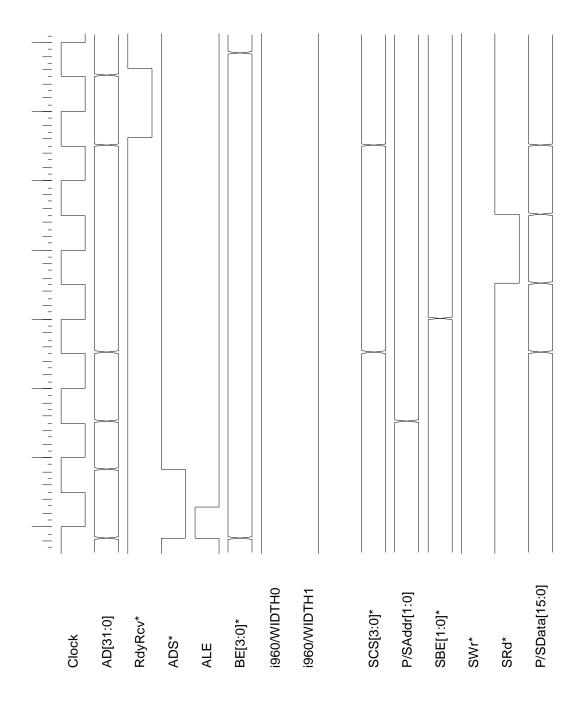

#### 2.1 CPU Interface

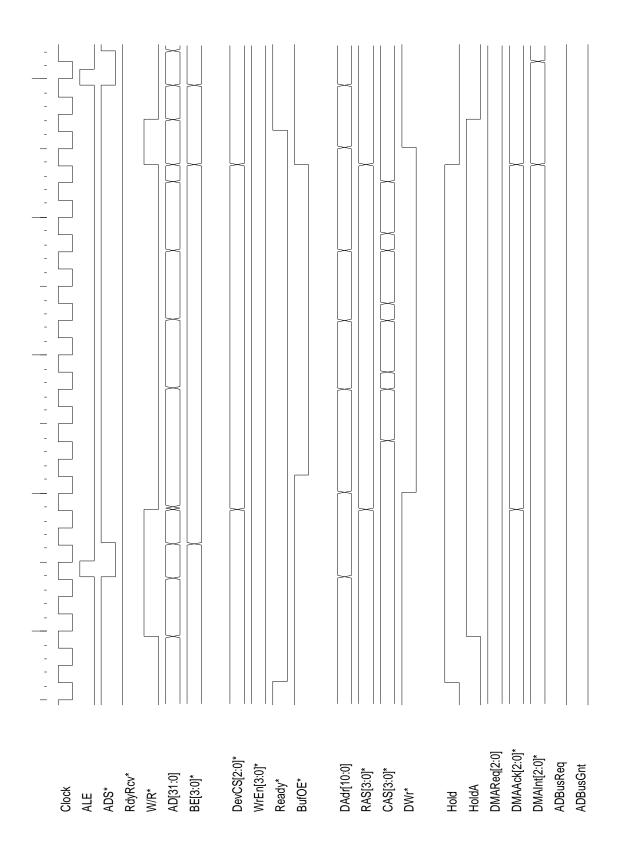

The GT-32090 has a glueless interface to the Intel i960JX family of processors with bus frequencies between 16MHz and 33MHz. External agents can take control of the AD bus and access all of the GT-32090 resources. The GT-32090 handles the priorities between the internal DMA resources, the CPU and the external agent. It will request the AD bus from the CPU and relinquish the bus to the external agent. For systems that need extension of the capabilities offered by the GT-32090, up to four GT-32090 devices can support one CPU. For example, with four GT-32090's, the system can have up to 512MBytes of DRAM and 12 DMA channels.

## 2.2 Address Space Decode

The GT-32090 decodes the address space in two stages. In the first stage, the decoding is done to eight groups that include the following: four spaces of 32 MBytes for the AD bus devices, 128 MBytes for the DRAM, 128 MBytes for the Simple I/O bus (SIO bus), 256 MBytes for the PCMCIA, and 64 MBytes for the internal address space. The decoding in the first stage is done by comparing the high order address bits with the Address Space registers' values. This way, four groups of devices are provided in order to enable mappings of 8-, 16- and 32bit devices in the same system, using different PMCONs (PMCONs are the i960JX's Physical Memory Configuration registers - see i960JX User's Manual). In the second stage, there is additional decoding to the specific device bank, DRAM bank, internal register, SIO bank, or PCM-CIA bank. The sub-decoding for the DRAM and the AD bus device banks is programmable while the sub-decoding for the internal registers, the PCMCIA cards, and the SIO devices, is fixed.

Each DRAM bank can have a programmable address space of 1MByte to 16MBytes that can be located anywhere in the DRAM address space. The address space size programmability enables a contiguous address space when accessing the different DRAM banks even when the banks have different sizes. The decoding is done by comparing address bits 25:20 to be between two values (High and Low) in the DRAM bank registers.

Each AD bus device bank can have a programmable address space of 2MBytes to 32MBytes. Similar to the DRAM banks, it enables a contiguous address space for different AD device bank sizes. The decoding is done by comparing address bits 24:21 to be between two values (High and Low) in the AD device bank registers.

The PCMCIA is allocated a 256MByte block that has a

fixed sub-decoding to four 64MByte spaces. The first 128MBytes are allocated to card A and the second 128MBytes to card B. Each 128MBytes are divided so that the first 64MBytes are for memory space and the second 64MBytes are for I/O address space.

The SIO space is sub-decoded to four fixed 16 MByte spaces for the SIO Chip Selects, or eight 16MByte spaces with external sub-decoding to create a 128MByte space.

The internal address space is sub-decoded for the control and status registers that reside on the GT-32090.

The GT-32090 will not respond to addresses that are not allocated to it, since that address space might be used for other devices.

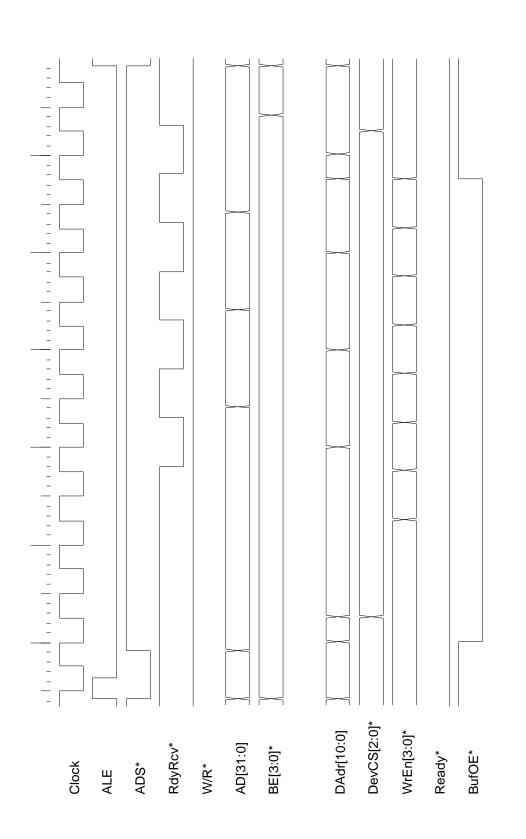

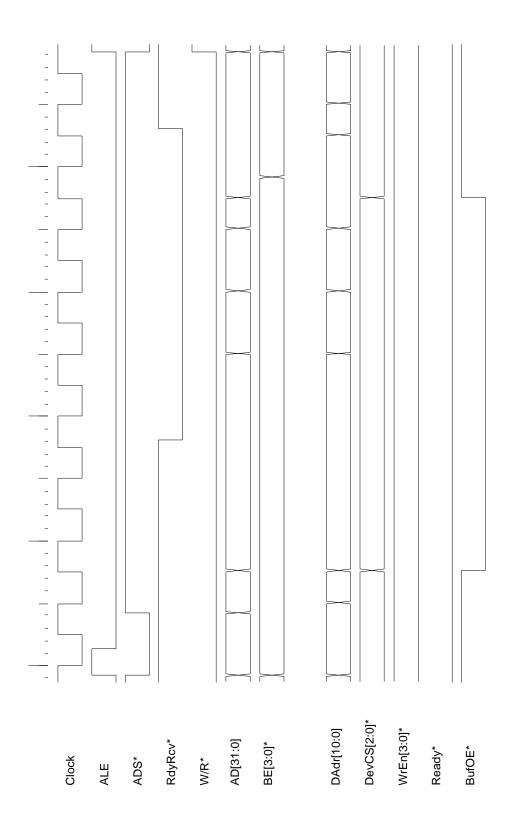

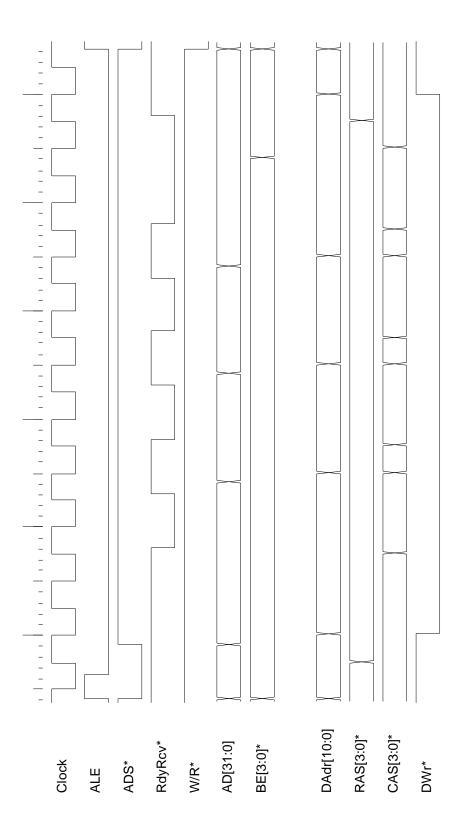

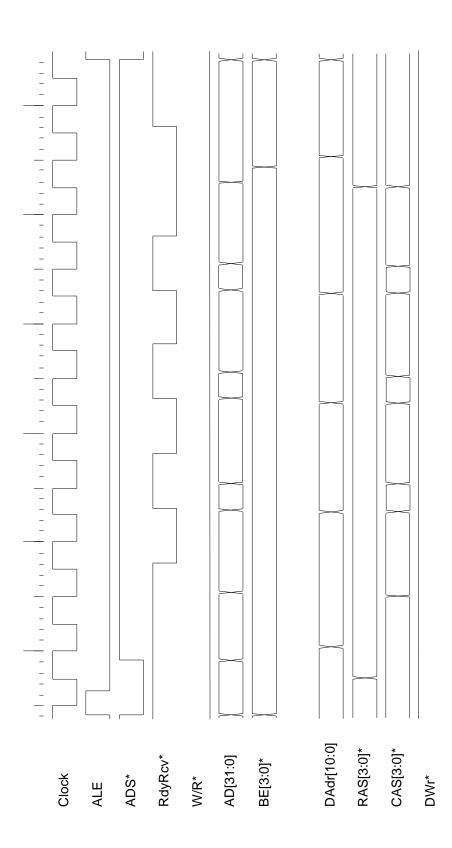

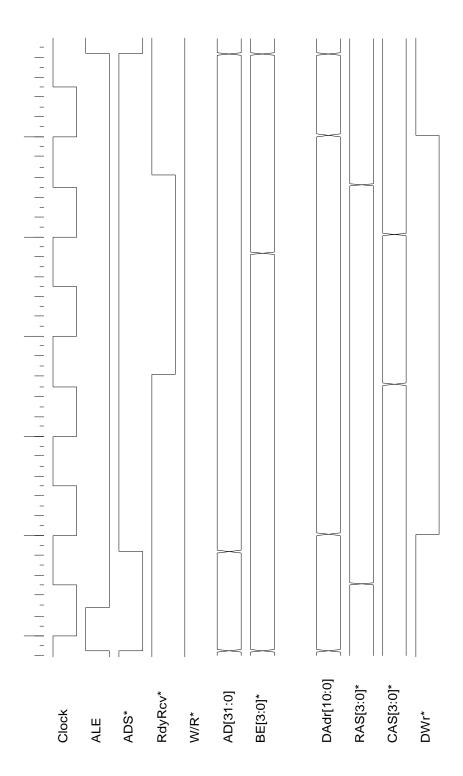

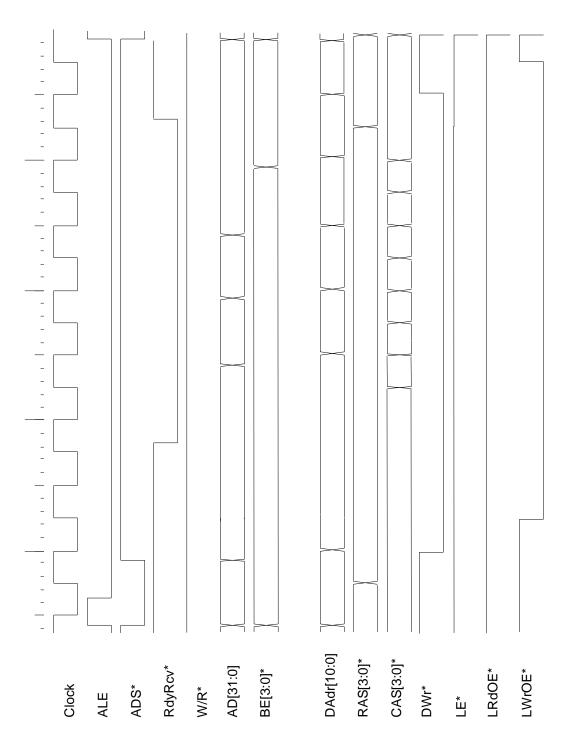

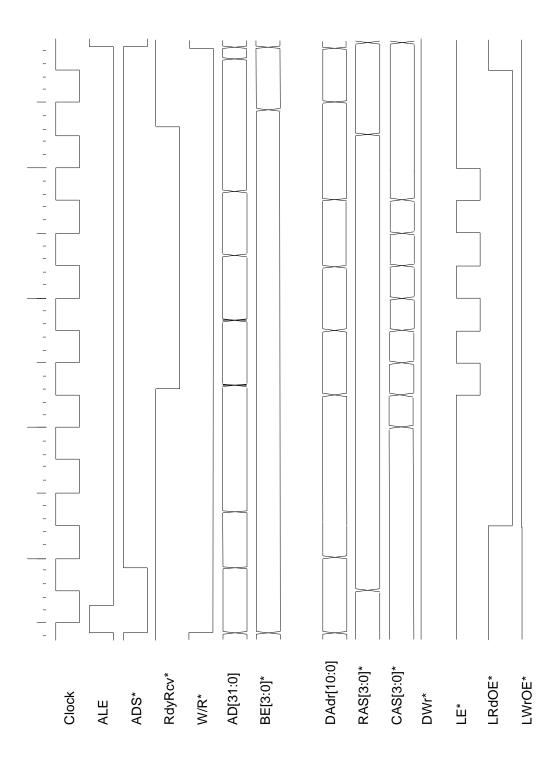

### 2.3 DRAM Controller

The DRAM controller supports 4 banks of page mode or EDO DRAMs. DRAM types supported are those with 0.5K, 1K, and 2K refresh, as well as asymmetric RAS/ CAS addressing. The depth of the DRAM devices can vary for each bank separately from 256K to 4M, and the width of all banks is 32-bits. With these options, each DRAM bank size can vary from 1MByte to 16MBytes. The DRAM timing is optimized for the different frequencies and device types supported. There is optional support for an external bi-directional latch on the DRAM's data bus for improved DRAM performance.

At 33MHz, a CPU read access from an EDO DRAM will have the pattern xxDDDD, which means 2 wait-states to first data and zero wait-state for each additional word. At 33MHz, with standard DRAMs, the pattern will be xxDxDxDxDx, meaning 2 wait-states to the first data and 1 wait-state for each additional word. At 25MHz, standard DRAM with latch or EDO DRAM will have a performance of xDDDD (one wait-state to first data). At 25MHz, standard DRAM without latches will be xxDxDxDxDx (2 waitstates to first data, 1 wait-state to burst data. At 20MHz and 16MHz using standard DRAM with latches or EDO DRAM, the pattern will be DDDD, zero wait-states to the first data and zero wait-states for each additional word. At 20MHz and 16MHz, DRAM performance is xxDxDxDxDx. DMA burst accesses can be one per clock, using the same parameters as for the CPU access.

Refresh can be programmed to different periods by a 16-bit refresh counter. Staggered and non-staggered refresh modes are supported. In staggered mode, the four banks of DRAM will be refreshed with one cycle delay between each bank, while in non-staggered mode all four banks will be refreshed together.

For systems that require more than 64MBytes of DRAM, it is possible to add 4 more DRAM banks with a simple external multiplexer, to get to a total of 128MBytes of DRAM with 8 RAS control signals, using Address[26] to multiplex between two banks. For instance, the demultiplexing can be implemented with a Quality Semiconductor QS3257.

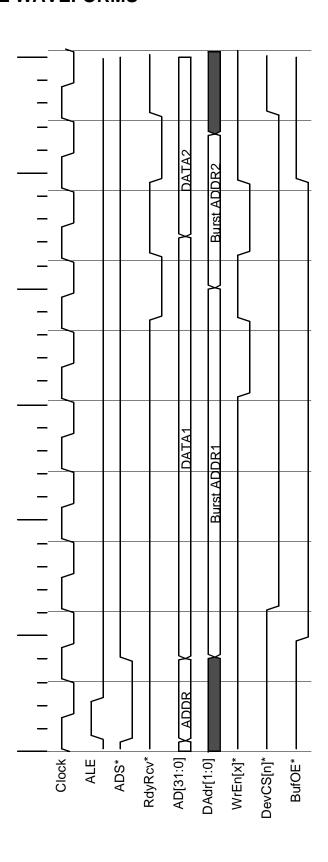

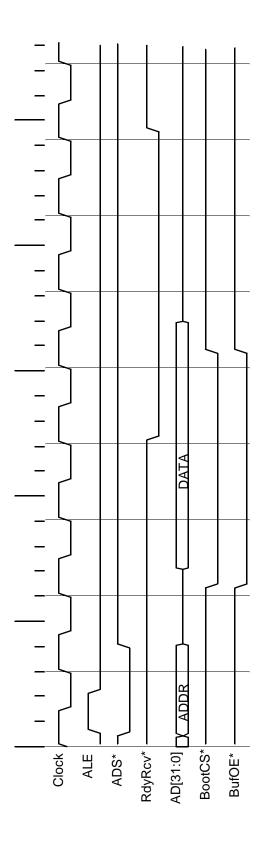

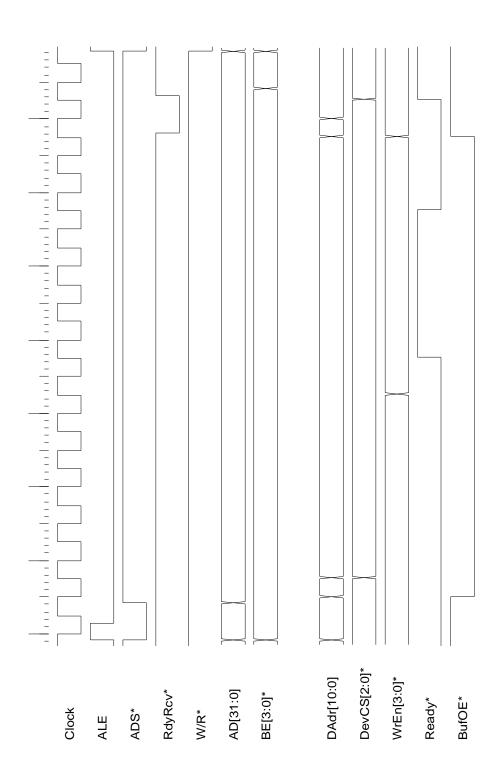

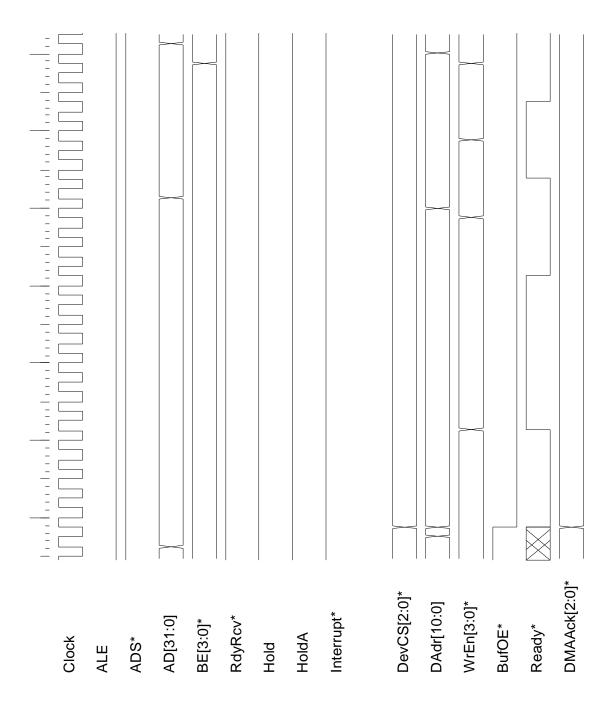

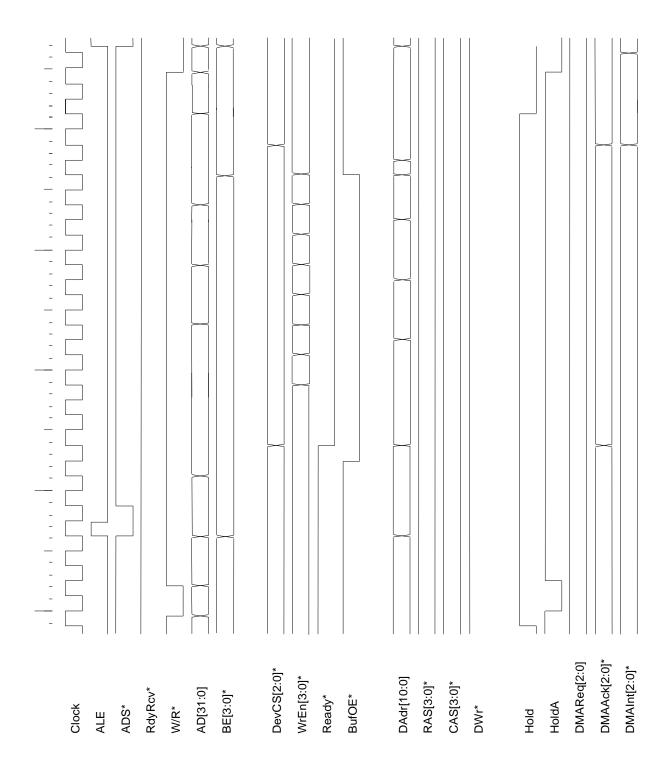

#### 2.4 AD Bus Device Controller

The GT-32090 supports directly four devices on the AD bus, one boot device and three general purpose devices such as Flash, SRAM, ROM, FIFO, or any other read/ write peripheral device. External logic can sub-decode the four chip selects to any number, using the Address for the sub-decoding. The device controller has several control signals to enable read and write accesses (including chip selects, reads, writes, and buffer control). Each Chip Select has a programmable address space of 2MBytes to 32MBytes to enable contiguous address space between the different banks. Byte writes are enabled through four Write Enable signals. The write signals can be shaped by specifying in the Device Bank Parameters registers the following: the number of cycles from the assertion of DevCS\* to the first assertion of write (CsToWr); the number of cycles the write pulse is active (WrActive); and the number of cycles the write signal is non-active between consecutive writes(WrHigh). The timing parameters of the write signals determine the length of active DevCS\* and DMAAck\* (when allocated to an AD bus device).

In read cycles, the following parameters are programmable: the number of cycles from the assertion of Chip Select to the rising edge of the clock that samples the first data (DelayToFirst), the number of cycles from when data is sampled to the next time data is sampled (DelayToNext); and the number of cycles between the deassertion of DevCS\* to a new AD bus cycle (TurnOff).

Each device can be configured as 8-, 16- or 32-bits wide, by programming the appropriate i960Jx's PMCON register to the desired bus width, and mapping the appropriate Device n Address Space decode register into this address space. Each PMCON configures the bus width of a memory region with a specific Addr[31:29] while the Device n Address Space decode register maps device #n into a region with a specific Addr[31:25].

The device controller supports read or write bursts of up to four data elements. The burst address is supported by a 2-bit wide address bus that is multiplexed with the two least significant bits of the DRAM address (DAdr[1:0]) when the device is 32-bits wide. For an 8-bit device the burst address is the CPU's BE[1:0]\*, and for a 16-bit

device the burst address is the CPU's {A2, BE[1]\*}. For an 8-bit device the write signal is WrEn[0]\*, and for a 16-bit device the write signals are WrEn[3]\* (Write High Byte) and WrEn[0]\* (Write Low Byte).

The Ready\* pin enables an extension of a device cycle beyond the values that are programmed in the Device Bank Parameters register. All the control signals will continue to be in their state when the Ready\* signal is sampled inactive, and until it becomes active. The internal state machine counters will continue to count to the programmed values, even when Ready\* is HIGH. The control signals will change only when the Ready\* is LOW and the counters are at terminal count. After insertion of wait states and re-assertion of Ready\*, there are two clock cycles to data transfer. The use of the Ready\* signal is individually optional for each bank through a programmable bit in the Device Bank Parameters registers.

In systems where the devices on the AD bus represent a large load, or where there are devices with long turn-off times, the GT-32090 supports an optional bi-directional transceiver (245 type) to isolate the device bus from the CPU's AD bus. The BufOE\* signal controls the bi-directional transceiver's OE\* and the W/R\* signal controls its direction.

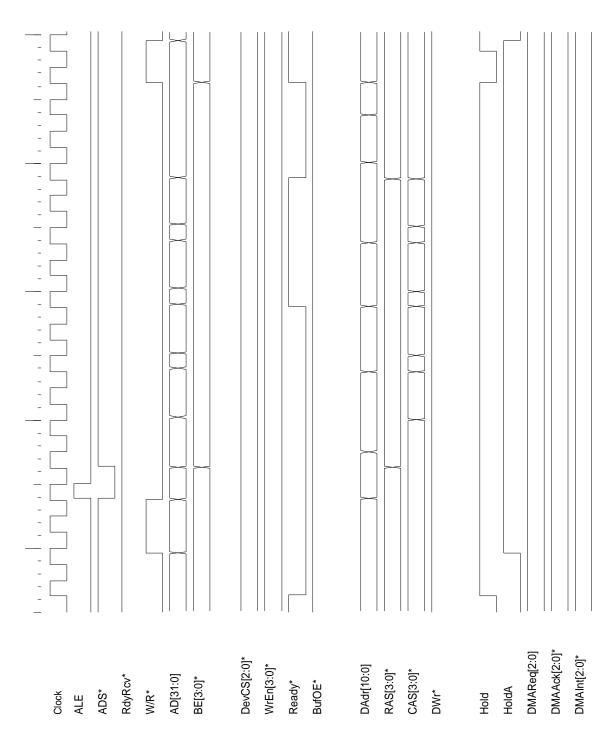

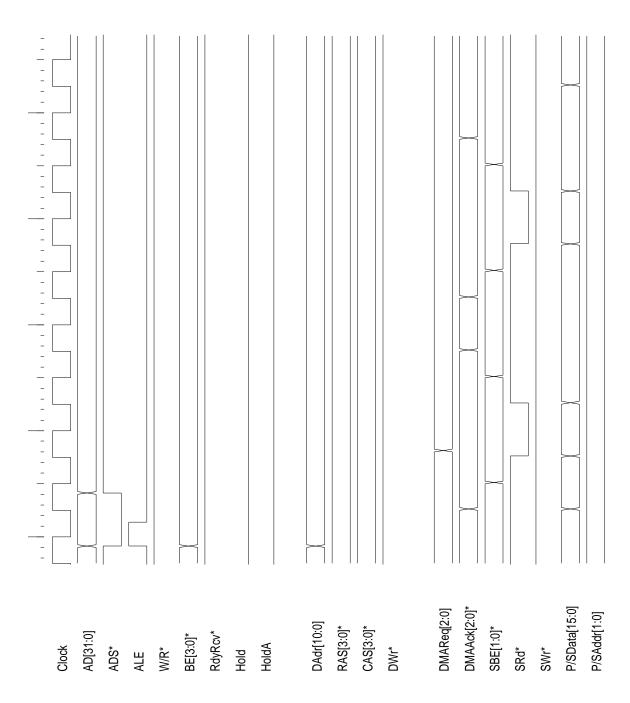

#### 2.5 DMA

The DMA controller can move data between devices on the AD bus, or between devices on the AD bus and devices on the SIO bus. There are two DMA subsystems on the GT-32090, one handles the DMA activity on the SIO bus, and the other handles the activity on the AD bus. Each DMA subsystem has its own data storage resources and arbiters. The two DMA subsystems can work simultaneously or independently, except for the time that they transfer data between the SIO bus and the AD bus. Both subsystems can have at one time three DMA channels active. Each of the three channels can be allocated to service the SIO bus or the AD bus.

DMA accesses can be initiated by an external request by asserting one of the three DMAReq pins (Demand mode), or by setting an internal bit in a register (Block mode). Access can be non-aligned both at the source and at the destination, and up to 64KBytes of data can be transferred in each transaction.

The AD bus DMA can transfer data in two ways: through an internal 16-byte FIFO, or directly between the DRAM and an AD bus device ("fly-by"). In the internal mode, data is transferred from the source device/DRAM into the internal FIFO, and from the internal FIFO to the destination device/DRAM. In "fly-by" mode, the access is to

DRAM with assertion of DevCS\*, DMAAck\*, and WrEn\*, if necessary. The WrEn\* signals are not toggled. The length of each DMA access can be limited to 1, 2, or 4 32-bit words.

For a 32-bit device, the write signals are WrEn[3:0]\*. For a 16-bit device, the write signals are WrEn[3]\* for write high byte, and WrEn[0]\* for write low byte. For an 8-bit device, the write signal is WrEn[0]\*.

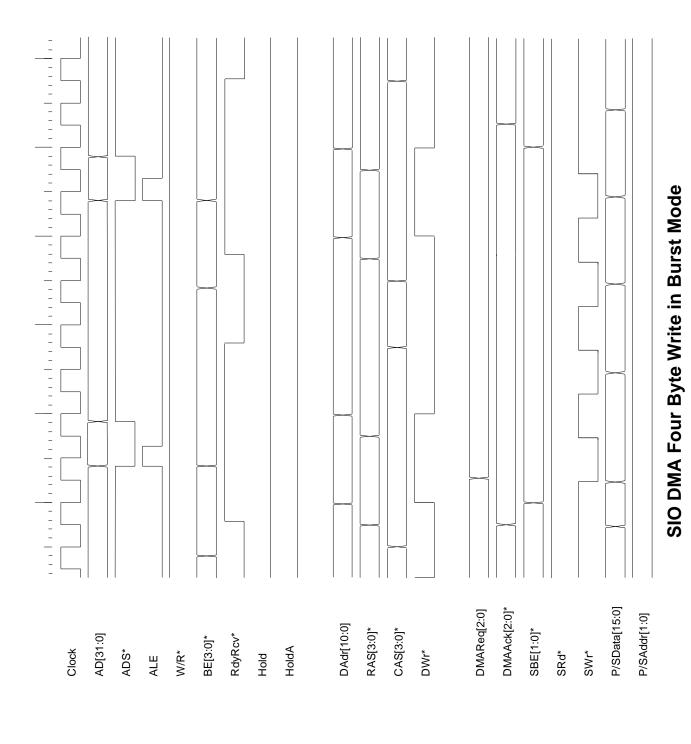

The SIO bus DMA can transfer data between an 8- or 16-bit wide device on the SIO bus, and a 32-bit wide device/DRAM on the AD bus. In read accesses (from an SIO device to an AD bus device), the SIO DMA uses one of three internal packing registers (one for each channel), that pack 8- or 16-bit data into 32-bit words. In write accesses (from an AD bus device to an SIO device), the SIO DMA uses one of three internal unpacking registers (one for each channel), that unpack 32-bit words into 8-or 16-bit data.

The SIO channel can be programmed as read (source) or write (destination) depending on bit 5 of the Channel Mode register.

During an SIO DMA, data is transferred in two stages that involve one of the SIO local packing and unpacking registers, and the FIFO in the AD DMA unit.

During an SIO DMA read access, the SIO device will arbitrate for the SIO bus in the local SIO arbiter, and will move data into its channel packing register. When the register is full, or when the DMA counter reaches terminal count, the packing register will arbitrate in the AD DMA arbiter for the AD DMA FIFO, and will transfer the data to it. When the data is in the FIFO, the FIFO will request the AD bus and will transfer data to the AD bus device.

During an SIO DMA write access, the AD DMA will move data from the AD bus to its internal FIFO. From the FIFO, it will move the data into the SIO unpacking register, and then the SIO DMA will unpack and transfer the data to the requesting SIO device.

The SIO packing/unpacking register can be flushed by writing to the Channel Flush/Reset register (see section 3.11).

The SIO channel can be programmed to two possibilities of arbitration:

- 1) Access Arbitration: Arbitration between SIO channels is done in every SIO DMA access (byte or 16-bit word).

- 2) Word Arbitration: Arbitration between SIO channels is done only when the DMA finishes packing/unpacking its register (four byte transfers or two 16-bit word trans-

fers).

The DMA controller supports chained and non-chained modes of operation. In the non-chained mode, the CPU programs the DMA channel for each DMA transaction. In chained mode, the DMA controller programs itself for the next DMA operation by fetching the information from a linked list of records in memory.

The DMA controller can be programmed to assert an interrupt in chained mode, at the end of every DMA transaction or when the Next Pointer Register is NULL and Byte Count reaches terminal count. In non-chained mode, the DMA will assert an interrupt every time the Byte Count reaches terminal count.

There are two separate arbiters for DMA accesses. One arbiter prioritizes accesses between devices on the SIO bus for data transfers between SIO devices and their packing/unpacking registers. The second arbiter prioritizes accesses between devices on the AD bus and SIO devices. The two arbiters have programmable priorities and are identical in their functionality. The arbiter programmable options work as follows: Channels 0 and 1 are in one group, and channel 2 in the second group. Inside the two channel group, the priority can be fixed with a selected channel number having the higher priority, or both can have the same priority in round robin fashion. The same scheme applies between the two groups, they can have fixed or round robin priority.

In systems with EDO DRAM at 33MHz or Page Mode DRAM at 16 to 25MHz that require high bandwidth, the data phase should be extended. In order to extend the data phase, a bi-directional latch should be used. The GT-32090 controls the latch- read output enable (DRAM Data to CPU Bus), write output enable (CPU Data to DRAM Data), read latch enable (DRAM Data). The latching at the CPU bus is done with the use of the system clock. The correct timing of the controls is derived from the system's parameters - ADFreq, Type, and Latch, which are programmed in the DRAM Parameters register.

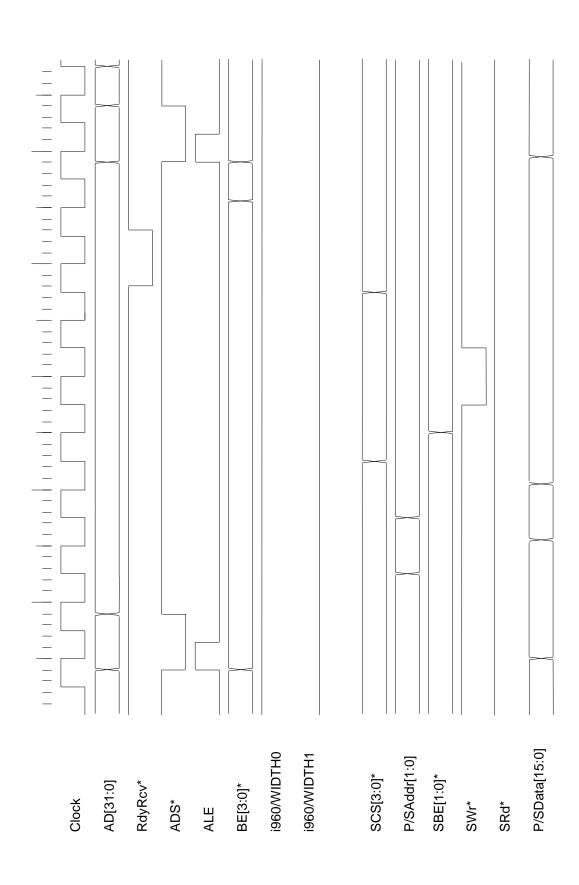

#### 2.6 SIO

The SIO interface is a simple Read/Write with Chip Select bus interface. The interface includes: a dedicated 16-bit wide data bus that is shared with the PCMCIA devices, an address bus that is shared with the AD bus devices, dedicated byte and 16-bit word address, byte enables (SBE[1:0]\*), four chip selects (SCS[3:0]\*), read (SRd\*) and write (SWr\*) control signals, and a flow control signal (SWait\*), in addition to the DMA signals.

The SWait\* pin is used to extend a data cycle. Two cycles prior to the end of an access, SWait\* is sampled. If it is asserted, then the access is extended. When SWait\* is again deasserted, two more cycles will be executed until the end of the data transfer.

Standard address space is 64MBytes. Each of the Chip Select signals has a 16 MByte address space, can be configured as 8-bit or 16-bit wide, and has programmable timing. Big and little endian conversion is supported for each device. The SIO supports up to three slave DMA devices as described in section 2.5. Further sub-decoding can result in four Chip Selects for a total of 128 MBytes of address space.

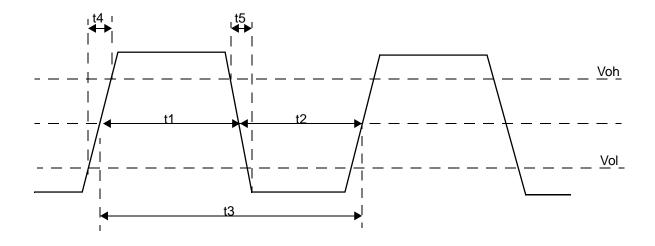

Timing for an SIO bus DMA or CPU access is programmable. The user can specify the width of active SRd\* and SWr\* signals, and the Turn-Off time of the device. The width of SRd\* and SWr\* dictate the shapes of SCS\* and DMAAck\*. They are asserted one cycle before SRd\* or SWr\* become active, and remain active for one cycle after SRd\* or SWr\* is deasserted. The GT-32090 will not start a new read cycle from a different SIO device and will not start a new write access on the SIO bus as long as the Turn-Off time is not satisfied. The Turn-Off Width will start counting when SCS\* is deasserted to terminal count.

When the channel is programmed to Word arbitration, a device will be served until all the remaining bytes are packed/unpacked. Between accesses, DMAAck\* will be deasserted for 1 cycle and SWr\* /SRd\* for 3 cycles. When the channel is programmed to Burst Mode with Word arbitration, DMAAck\* will stay asserted through the entire burst. It will be asserted one cycle before SRd\* (or SWr\*) becomes active, and remain asserted until one cycle after the last SRd\* (or SWr\*) of the burst is deasserted. The SRd\* or SWr\* signals will be asserted for the number of clocks programmed in PulsWid and deasserted for one clock.

The partition between the devices is fixed and decoding in the SIO is done on address bits 25:24.

SCS[0]\*: Address[25:24] = 00 SCS[1]\*: Address[25:24] = 01 SCS[2]\*: Address[25:24] = 10 SCS[3]\*: Address[25:24] = 11

#### 2.7 PCMCIA

Two PCMCIA cards can be supported directly by the GT-32090. Each card has a 128MByte address space dedicated to it, 64MBytes for I/O space and 64MBytes for memory space. There is support for big or little endian data formats and 8-bit or 16-bit accesses. The timing of

the control signals to the cards is programmable. All the control signals between the cards and the GT-32090 can be connected without glue logic except for the static control and status signals. They are interfaced to the GT-32090 through an external latch and buffer, as shown in the application section.

The partition between PCMCIA devices is fixed and decoding is done on address bits 27:26.

PCMCIAa Memory : Address[27:26] = 00

PCMCIAa I/O : Address[27:26] = 01

PCMCIAb Memory : Address[27:26] = 10

PCMCIAb I/O : Address[27:26] = 11

## 2.8 JTAG (Boundary Scan)

The GT-32090 supports JTAG test features compatible with the IEEE Standard Test Access Port And Boundary Scan Architecture (IEEE 1149.1.A).

The JTAG features supported are:

| Test Name | Binary Code |

|-----------|-------------|

| EXTEST    | 000         |

| SAMPLE    | 010         |

| IDCODE    | 001         |

| STCTST    | 101         |

| INTEST    | 100         |

| BYPASS    | 111         |

The GT-32090 IDCode is 03290115h.

Bit[31:28]: Version: '0000'

Bit[27:12]: Part Number: '0011001010010000'

Bit[11:1]: Manufacturer ID: '00010001010'

Bit[0]: IDCode's bit[0] is '1' by definition.

### Boundary Scan Pins Order:

All the control signals are active LOW, that is, the output is enabled when its control signal is "0".

| pad signal | chain<br>pos | pad<br>type | scan<br>type | control signal |

|------------|--------------|-------------|--------------|----------------|

| -          | [145]        | ctrl        | norm         | s_io_oe_buf3_Z |

| P/SData[0] | [144]        | bidir       | norm         | s_io_oe_buf3_Z |

| P/SData[1] | [143]        | bidir       | norm         | s_io_oe_buf3_Z |

| P/SData[2] | [142]        | bidir       | norm         | s_io_oe_buf3_Z |

| P/SData[3] | [141]        | bidir       | norm         | s_io_oe_buf3_Z |

| P/SData[4] | [140]        | bidir       | norm         | s_io_oe_buf3_Z |

|            |              |             |              |                |

| pad signal       | chain<br>pos  | pad<br>type    | scan<br>type | control signal               |

|------------------|---------------|----------------|--------------|------------------------------|

| P/SData[5]       | [139]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[6]       | [138]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[7]       | [137]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[8]       | [136]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[9]       | [135]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[10]      | [134]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[11]      | [133]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[12]      | [132]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[13]      | [131]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[14]      | [130]         | bidir          | norm         | s_io_oe_buf3_Z               |

| P/SData[15]      | [129]         | bidir          | norm         | s_io_oe_buf3_Z               |

| Test*            | [128]         | input          | obsrv        |                              |

| Rst*             | [127]         | input          | obsrv        |                              |

| -                | [126]         | ctrl           | norm         | adbusgnt_pad_<br>bst_oe_PO   |

| ADBusGnt         | [125]         | 3state         | norm         | adbusgnt_pad_<br>bst_oe_PO   |

| ADBusReq         | [124]         | input          | obsrv        |                              |

| -                | [123]         | ctrl           | norm         | p_test*                      |

| DMAInt[2,0:1]*   | [122:<br>120] | 3state         | norm         | p_test*                      |

| Hold             | [119]         | 3state         | norm         | p_test*                      |

| RdyRcv*          | [118]         | 3state         | norm         | p_test*                      |

| -                | [117]         | ctrl           | norm         | ad_en_buf2_Z                 |

| AD[0]            | [116]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[1]            | [115]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[2]            | [114]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[3]            | [113]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[4]            | [112]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[5]            | [111]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[6]            | [110]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[7]            | [109]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[8]            | [108]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[9]            | [107]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[10]           | [106]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[11]           | [105]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[12]           | [104]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[13]           | [103]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[14]           | [102]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[15]           | [101]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[16]           | [100]         | bidir          | norm         | ad_en_buf2_Z                 |

| AD[17]           | [99]          | bidir          | norm         | ad_en_buf2_Z                 |

|                  | [00]          |                |              |                              |

| AD[18]           | [98]          | bidir          | norm         | ad_en_buf2_Z                 |

| AD[18]<br>AD[19] |               | bidir<br>bidir | norm         | ad_en_buf2_Z<br>ad_en_buf2_Z |

|                  | [98]          |                |              |                              |

| pad signal   | chain<br>pos | pad<br>type | scan<br>type | control signal |

|--------------|--------------|-------------|--------------|----------------|

| AD[22]       | [94]         | bidir       | norm         | ad_en_buf2_Z   |

| AD[23]       | [93]         | bidir       | norm         | ad_en_buf2_Z   |

| AD[24]       | [92]         | bidir       | norm         | ad_en_buf2_Z   |

| AD[25]       | [91]         | bidir       | norm         | ad_en_buf2_Z   |

| AD[26]       | [90]         | bidir       | norm         | ad_en_buf2_Z   |

| AD[27]       | [89]         | bidir       | norm         | ad_en_buf2_Z   |

| AD[28]       | [88]         | bidir       | norm         | ad_en_buf2_Z   |

| AD[29]       | [87]         | bidir       | norm         | ad_en_buf2_Z   |

| AD[30]       | [86]         | bidir       | norm         | ad_en_buf2_Z   |

| AD[31]       | [85]         | bidir       | norm         | ad_en_buf2_Z   |

| Clock        | [84]         | input       | obsrv        |                |

| -            | [83]         | ctrl        | norm         | p_io_oe1_buf_Z |

| BE[3:0]*     | [82:79]      | bidir       | norm         | p_io_oe1_buf_Z |

| -            | [78]         | input       | obsrv        |                |

| -            | [77]         | ctrl        | norm         | p_io_oe0*      |

| ALE          | [76]         | bidir       | norm         | p_io_oe0*      |

| HoldA        | [75]         | input       | obsrv        |                |

| W/R*         | [74]         | bidir       | norm         | p_io_oe0*      |

| ADS*         | [73]         | bidir       | norm         | p_io_oe0*      |

| -            | [72]         | ctrl        | norm         | d_test1*       |

| LE*          | [71]         | 3state      | norm         | d_test1*       |

| LRdOE*       | [70]         | 3state      | norm         | d_test1*       |

| LWrOE*       | [69]         | 3state      | norm         | d_test1*       |

| DWr*         | [68]         | 3state      | norm         | d_test1*       |

| RAS[3:0]*    | [67:64]      | 3state      | norm         | d_test1*       |

|              | [63]         | ctrl        | norm         | d_test0_buf_Z  |

| CAS[3:0]*    | [62:59]      | 3state      | norm         | d_test0_buf_Z  |

|              | [58]         | ctrl        | norm         | d_test0_i*     |

| DAdr[0:10]   | [57:47]      | 3state      | norm         | d_test0_i*     |

| Ready*       | [46]         | input       | obsrv        |                |

|              | [45]         | ctrl        | norm         | p_test_buf_Z   |

| BufOE*       | [44]         | 3state      | norm         | p_test_buf_Z   |

| _            | [43]         | ctrl        | norm         | d_test1*       |

| WrEn[3:0]*   | [42:39]      | 3state      | norm         | d_test1*       |

| BootCS*      | [38]         | 3state      | norm         | d_test1*       |

| DevCS[2:0]*  | [37:35]      | 3state      | norm         | d_test1*       |

|              | [34]         | ctrl        | norm         | s_test*        |

| SCS[3:0]     | [33:30]      | 3state      | norm         | s_test*        |

| DMAReq[2:0]  | [29:27]      | input       | obsrv        |                |

| _            | [26]         | ctrl        | norm         | s_test1*       |

| DMAAck[2:0]* | [25:23]      | bidir       | norm         | s_test1*       |

| SBE[1:0]*    | [22:21]      | 3state      | norm         | s_test*        |

| SRd*         | [20]         | 3state      | norm         | s_test*        |

| SWr*         | [19]         | 3state      | norm         | s_test*        |

| SWait*       | [18]         | input       | obsrv        |                |

|              |              |             |              |                |

| pad signal    | chain<br>pos | pad<br>type | scan<br>type | control signal |

|---------------|--------------|-------------|--------------|----------------|

| _             | [17]         | ctrl        | norm         | sp_test*       |

| IOWrA*        | [16]         | 3state      | norm         | sp_test*       |

| IORdA*        | [15]         | 3state      | norm         | sp_test*       |

| WrEnA*        | [14]         | 3state      | norm         | sp_test*       |

| OEA*          | [13]         | 3state      | norm         | sp_test*       |

| CardEnA[2:1]* | [12:11]      | 3state      | norm         | sp_test*       |

| WaitA*        | [10]         | input       | obsrv        |                |

| IOWrB*        | [9]          | 3state      | norm         | sp_test*       |

| IORdB*        | [8]          | 3state      | norm         | sp_test*       |

| WrEnB*        | [7]          | 3state      | norm         | sp_test*       |

| OEB*          | [6]          | 3state      | norm         | sp_test*       |

| CardEnB[2:1]* | [5:4]        | 3state      | norm         | sp_test*       |

| WaitB*        | [3]          | input       | obsrv        |                |

| -             | [2]          | ctrl        | norm         | s_test_Z       |

| P/SAddr[1:0]  | [1:0]        | 3state      | norm         | s_test_Z       |

| •             |              |             |              |                |

# 2.9 Reset Configuration

The GT-32090 must acquire some knowledge of the system before it is configured by the software. The following configuration pins are sampled from when Rst\* is asserted, until 4 Clock cycles after it is deasserted:

DMAAck[2:0]\* - Indicates the three MSB's of the GT-32090 Internal address space decode, bits 31:29. These bits are sampled into the Internal Address Space Decode & Control register bits [5:3].

DMAReq[2:0] - Indicates the three MSB's of the GT-32090's four devices address, bits 31:29. These bits are sampled into bits [6:4] of the Device n Address Space registers.

## 3 REGISTER TABLES

The GT-32090's internal registers are memory mapped and can be accessed by the CPU. The registers' address is comprised of the value in the Internal Address Space Decode and Control register and the register's Offset. For example, to access the "Channel 0 DMA Byte Count" register (Offset 0x800) immediately after reset, assuming that during reset DMAAck[2:0]\*'s value was "110", the following occurs: the value in the "Internal Address Space Decode and Control" register bits [5:0] will be "0x33", which must match the AD bus bits [31:26] as "110011", and the offset being 0x800, will result in a 32-bit address of 0xcc000800. The location of the registers in the memory space can be changed by changing the value programmed into the Internal Address Space Decode and Control register. For example, after changing the value in this register by writing to 0xcc00001c a value of "0x28", an access to the "Channel 0 DMA Byte Count" register will be with 0xa0000800.

The GT-32090's internal registers are 32-bits wide and consequently the appropriate memory region must be configured as a 32-bits region, which is done by programming the CPU's appropriate PMCON register.

## 3.1 Register Map

| Group Address Space  DRAM Address Space  Device 0 Address Space | 0x000<br>0x004<br>0x008 |

|-----------------------------------------------------------------|-------------------------|

| Device 0 Address Space                                          | 0x004                   |

| ,                                                               |                         |

| Davidas A Aslalasas Ossass                                      | 0x008                   |

| Device 1 Address Space                                          |                         |

| Device 2 Address Space                                          | 0x00c                   |

| Boot Device Address Space                                       | 0x010                   |

| SIO Address Space                                               | 0x014                   |

| PCMCIA Address Space                                            | 0x018                   |

| Internal Address Space Decode and Control                       | 0x01c                   |

| DRAM Address Space                                              |                         |

| RAS[0] Decode Address                                           | 0x400                   |

| RAS[1] Decode Address                                           | 0x404                   |

| RAS[2] Decode Address                                           | 0x408                   |

| RAS[3] Decode Address                                           | 0x40c                   |

| Device Address Space                                            |                         |

| CS[0] Decode Address                                            | 0x410                   |

| CS[1] Decode Address                                            | 0x414                   |

| CS[2] Decode Address                                            | 0x418                   |

| BootCS Decode Address                                           | 0x41c                   |

| DRAM Refresh Configuration                                      |                         |

| Refresh Configuration                                           | 0x420                   |

| DRAM Parameters                                                 |                         |

| DRAM Parameters                                                 | 0x424                   |

| Device Parameters                                               |                         |

| Device Bank0 Parameters                                         | 0x428                   |

| Device Bank1 Parameters                                         | 0x42c                   |

| Device Bank2 Parameters                                         | 0x430                   |

| Device Boot Bank Parameters                                     | 0x434                   |

| Channel 0 DMA Byte Count Channel 1 DMA Byte Count Channel 2 DMA Byte Count Channel 2 DMA Byte Count Channel 0 DMA Source Address Channel 1 DMA Source Address Channel 1 DMA Source Address Ox810 Channel 2 DMA Source Address Ox814 Channel 2 DMA Source Address Ox820 Channel 0 DMA Destination Address Channel 1 DMA Destination Address Ox824 Channel 2 DMA Destination Address Ox828 Channel 0 Next Record Pointer Ox830 Channel 1 Next Record Pointer Ox834 Channel 2 Next Record Pointer Ox838  DMA Channel Control Channel 1 Control Ox840 Channel 2 Control Ox848  DMA Arbiter Arbiter Control Ox860  SIO Configuration Arbiter Control Ox604 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel 1 DMA Byte Count Channel 2 DMA Byte Count Channel 0 DMA Source Address Channel 1 DMA Source Address Channel 1 DMA Source Address Channel 2 DMA Source Address Channel 0 DMA Destination Address Channel 1 DMA Destination Address Channel 1 DMA Destination Address Channel 2 DMA Destination Address Channel 2 DMA Destination Address Channel 0 Next Record Pointer Ox830 Channel 1 Next Record Pointer Ox834 Channel 2 Next Record Pointer Ox838  DMA Channel Control Channel 0 Control Channel 1 Control Channel 2 Control Ox844 Channel 2 Control Ox848  DMA Arbiter Arbiter Control Ox860  SIO Configuration Arbiter Control Oxc00      |

| Channel 2 DMA Byte Count Channel 0 DMA Source Address Ox810 Channel 1 DMA Source Address Ox814 Channel 2 DMA Source Address Ox818 Channel 0 DMA Destination Address Channel 1 DMA Destination Address Ox820 Channel 1 DMA Destination Address Ox824 Channel 2 DMA Destination Address Ox828 Channel 0 Next Record Pointer Ox830 Channel 1 Next Record Pointer Ox834 Channel 2 Next Record Pointer Ox838  DMA Channel Control Channel 1 Control Ox844 Channel 2 Control Ox848  DMA Arbiter Arbiter Control Ox860  SIO Configuration Arbiter Control Oxc00                                                                                              |

| Channel 0 DMA Source Address Channel 1 DMA Source Address Ox814 Channel 2 DMA Source Address Channel 0 DMA Destination Address Channel 1 DMA Destination Address Ox820 Channel 1 DMA Destination Address Ox824 Channel 2 DMA Destination Address Ox828 Channel 0 Next Record Pointer Ox830 Channel 1 Next Record Pointer Ox834 Channel 2 Next Record Pointer Ox838  DMA Channel Control  Channel 0 Control Ox840 Channel 1 Control Ox844 Channel 2 Control Ox848  DMA Arbiter  Arbiter Control Ox860  SIO Configuration Arbiter Control Oxc00                                                                                                         |

| Channel 1 DMA Source Address Channel 2 DMA Source Address Channel 0 DMA Destination Address Channel 1 DMA Destination Address Channel 2 DMA Destination Address Channel 2 DMA Destination Address Channel 0 Next Record Pointer 0x830 Channel 1 Next Record Pointer 0x834 Channel 2 Next Record Pointer 0x838  DMA Channel Control Channel 0 Control Channel 1 Control 0x844 Channel 2 Control 0x848  DMA Arbiter Arbiter Control 0x860  SIO Configuration Arbiter Control 0xc00                                                                                                                                                                      |

| Channel 2 DMA Source Address Channel 0 DMA Destination Address Channel 1 DMA Destination Address Channel 2 DMA Destination Address Channel 2 DMA Destination Address Channel 0 Next Record Pointer Channel 1 Next Record Pointer Channel 1 Next Record Pointer Channel 2 Next Record Pointer Ox834 Channel 2 Next Record Pointer Ox838  DMA Channel Control Channel 0 Control Channel 1 Control Channel 2 Control Ox844 Channel 2 Control Ox848  DMA Arbiter Arbiter Control SIO Configuration Arbiter Control Oxc00                                                                                                                                  |

| Channel 0 DMA Destination Address Channel 1 DMA Destination Address Ox824 Channel 2 DMA Destination Address Ox828 Channel 0 Next Record Pointer Ox830 Channel 1 Next Record Pointer Ox834 Channel 2 Next Record Pointer Ox838  DMA Channel Control Channel 0 Control Ox840 Channel 1 Control Ox844 Channel 2 Control Ox848  DMA Arbiter Arbiter Control SIO Configuration Arbiter Control Ox600                                                                                                                                                                                                                                                       |

| Channel 1 DMA Destination Address Channel 2 DMA Destination Address Ox828 Channel 0 Next Record Pointer Ox830 Channel 1 Next Record Pointer Ox834 Channel 2 Next Record Pointer Ox838  DMA Channel Control Channel 0 Control Ox840 Channel 1 Control Ox844 Channel 2 Control Ox848  DMA Arbiter Arbiter Control Ox860  SIO Configuration Arbiter Control Oxc00                                                                                                                                                                                                                                                                                        |

| Channel 2 DMA Destination Address Channel 0 Next Record Pointer Ox830 Channel 1 Next Record Pointer Ox834 Channel 2 Next Record Pointer Ox838  DMA Channel Control Channel 0 Control Ox840 Channel 1 Control Ox844 Channel 2 Control Ox848  DMA Arbiter Arbiter Control Ox860  SIO Configuration Arbiter Control Oxc00                                                                                                                                                                                                                                                                                                                                |

| Channel 0 Next Record Pointer 0x830 Channel 1 Next Record Pointer 0x834 Channel 2 Next Record Pointer 0x838  DMA Channel Control Channel 0 Control 0x840 Channel 1 Control 0x844 Channel 2 Control 0x848  DMA Arbiter Arbiter Control 0x860  SIO Configuration Arbiter Control 0x000                                                                                                                                                                                                                                                                                                                                                                  |

| Channel 1 Next Record Pointer         0x834           Channel 2 Next Record Pointer         0x838           DMA Channel Control         0x840           Channel 0 Control         0x840           Channel 1 Control         0x844           Channel 2 Control         0x848           DMA Arbiter           Arbiter Control         0x860           SIO Configuration           Arbiter Control         0xc00                                                                                                                                                                                                                                         |

| Channel 2 Next Record Pointer         0x838           DMA Channel Control           Channel 0 Control         0x840           Channel 1 Control         0x844           Channel 2 Control         0x848           DMA Arbiter         0x860           SIO Configuration         0xc00                                                                                                                                                                                                                                                                                                                                                                 |

| DMA Channel Control         0x840           Channel 0 Control         0x844           Channel 1 Control         0x844           Channel 2 Control         0x848           DMA Arbiter           Arbiter Control         0x860           SIO Configuration           Arbiter Control         0xc00                                                                                                                                                                                                                                                                                                                                                     |

| Channel 0 Control         0x840           Channel 1 Control         0x844           Channel 2 Control         0x848           DMA Arbiter           Arbiter Control         0x860           SIO Configuration           Arbiter Control         0xc00                                                                                                                                                                                                                                                                                                                                                                                                 |

| Channel 1 Control         0x844           Channel 2 Control         0x848           DMA Arbiter         0x860           SIO Configuration         0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Channel 2 Control 0x848  DMA Arbiter  Arbiter Control 0x860  SIO Configuration  Arbiter Control 0xc00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DMA Arbiter Arbiter Control 0x860  SIO Configuration Arbiter Control 0xc00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Arbiter Control 0x860  SIO Configuration  Arbiter Control 0xc00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SIO Configuration Arbiter Control 0xc00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Arbiter Control 0xc00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Channal Flush/Paget                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Channel Flush/Reset 0xc04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Channel 0 Mode 0xc08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Channel 1 Mode 0xc0c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

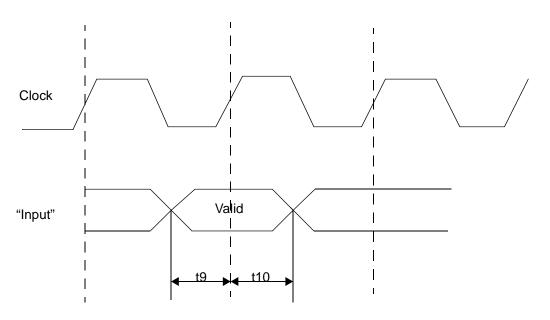

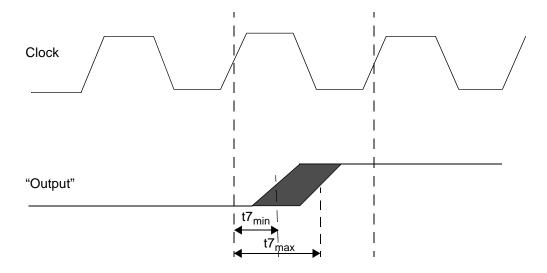

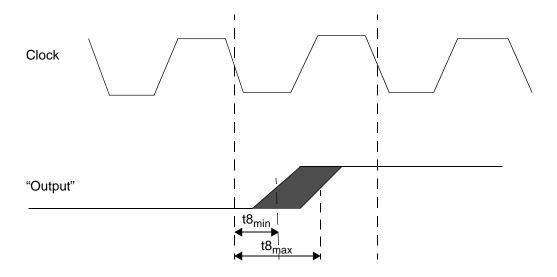

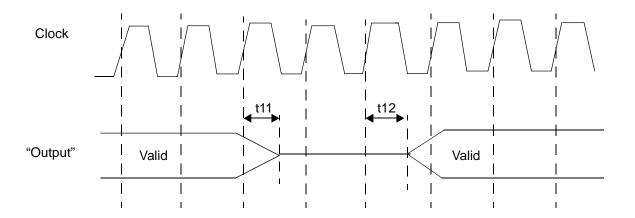

| Channel 2 Mode 0xc10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |