### **Advance Information**

May 1994

#### **DESCRIPTION**

The SSI 32H6811/6811B Servo and MSC Drivers, a CMOS monolithic integrated circuit housed in a 64-lead TQFP package, operates from a single 5V supply. It provides a fully integrated servo driver and a spindle motor commutator with internal power FETs. The servo driver is intended for use in disk drive head positioning systems employing linear or rotary voice coil motors. The commutator in conjunction with a microprocessor ( $\mu$ P) or digital signal processor (DSP), provides a complete spindle motor speed control system. It also includes two 10-bit D/A converters, with a serial interface to commonly used  $\mu$ P or DSP, for commanding the servo positioner and the spindle motor respectively. The device is ideal for use in 5V small-form disk driver applications.

#### **FEATURES**

- Internal 1.0A servo driver with no deadband, class-B output

- Thermal overload protection

- Power fault detection with built-in retract circuitry

- 10-bit VCM D/A converter with 4 μs digital delay

- Gain select switch for a wide dynamic range of servo inputs

- Internal precision voltage reference

- Programmable commutation delay for optimal motor efficiency

- 10-bit MSC D/A converter with 4 μs digital delay

- Internal 1.0A spindle driver

- Switch-mode current limiting for spindle motor start-up

- Serial interface compatible with 80C196 and 68HC16

- Low power CMOS design with Sleep and Power Saving modes

- 64-lead TQPF package

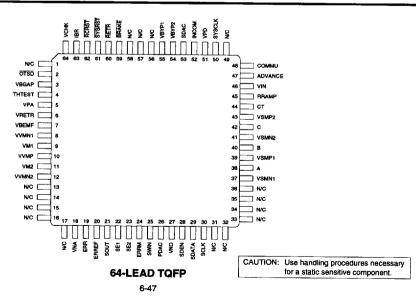

#### **PIN DIAGRAM**

0594 - rev.

8253965 0014675 564 📟

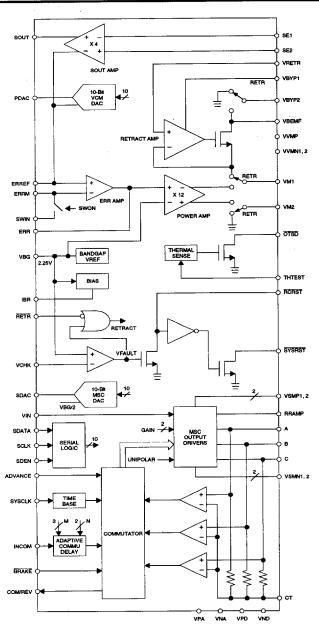

FIGURE 1: SSI 32H6811/6811B Functional Block Diagram

6-48

**8253965 0014676 4T0**

#### **FUNCTIONAL DESCRIPTION**

As shown in Figure 1, the SSI 32H6811 can be divided into four major sections: Servo positioner, Spindle motor commutator/driver, Control circuitry and Serial interface port.

#### Servo Positioner

The servo positioner is a power transconductance amplifier for use in driving a voice coil servo motor (VCM). It has two Primary modes of operation, normal (or linear) and retract. The Retract mode is activated by a power supply failure or when RETR is asserted low while BRAKE being high. Otherwise the device operates in Linear mode. The servo positioner consists of SOUT amplifier, ERR amplifier, retract amplifier, power amplifier and 10-bit VCM D/A converter.

#### **SOUT Amplifier**

The SOUT amplifier generates a voltage at SOUT, proportional to positioner current, by sensing the voltage across Rs, amplifying and referencing to ERREF. Since the Common mode voltage on Rs can range over the full power supply, while the differential voltage is in the order of millivolts, the SOUT amplifier is realized with a high input common mode rejection and low input offset.

#### **ERR Amplifier**

The ERR amplifier is a high gain op amp. Due to the fixed gain of the power amp, ERR is proportional to the VCM voltage. The negative input of this amplifier is the system summing junction for the currents which are proportional to the desired VCM current, the measured VCM current, and the VCM voltage.

#### **Power Amplifier**

The power amplifier is a fixed gain voltage amplifier with differential inputs and outputs. Its input is the differential voltage between ERR and VBG. Its output drives the VCM directly through an internal NMOS bridge. An internal charge pump generates gate voltages higher than VVMP so the upper NMOS devices can drive VM1 and VM2 up to VVMP.

#### **Retract Amplifier**

When a voltage fault is sensed, or when RETR is asserted low while BRAKE being high, the servo positioner enters into Retract mode. In this mode, it is

assumed that no current is available for VVMP. Thus power for this mode comes from VBEMF, the rectified spindle back emf voltage, and from VBYP1, a voltage generated from an external storage capacitor CBYP. The retract amplifier is powered by VBYP1. It senses the voltage at VRETR and, through a power NMOS source follower, raises VM1 to VRETR. The drain of the source follower is VBEMF.

#### VCM D/A Converter

Switched-capacitor circuit technique is employed to implement the VCM D/A converter with two non-overlapped clock phases, one phase for auto-zeroing and another one for evaluation. These two phases run synchronously with an internal 500 kHz clock, which is derived directly from the system clock at SYSCLK.

The request of the VCM D/A converter is initiated by writing to the VCM D/A register (00) through the serial interface port. The input data word must be coded in two's complement form. Note that there would be a maximum of 2  $\mu$ s of latency between a conversion request and the actual start of conversion. The conversion delay from the actual start of conversion to when the analog output begins to slew to a new value is 2  $\mu$ s. Therefore a maximum of 4  $\mu$ s is required for a conversion in addition to the time needed for completion of a serial data transfer, which is equal to 16/SCLK.

The VCM D/A converter provided at PDAC is referenced to ERREF, which also serves as a reference voltage for the error amplifier and the current sense amplifier.

#### **Spindle Motor Commutator/Driver**

The spindle motor commutator in conjunction with external components provides the motor driving capability for starting, accelerating and rotational speed regulation for brushless DC motors without the need for Hall sensors. The speed regulation control loop is completed with a  $\mu P$  or DSP external to this device.

#### Commutator

Motor armature position is determined by monitoring the coil voltage of the winding that is not presently being driven by the drivers. The back EMF from the coil, in conjunction with the state of the output drivers, indicates the armature position. The back EMF is compared with a reference at CT and initiates commutation "events" when the appropriate comparison is made. Commutation is the sequential switching of drive cur-

6-49

8253965 0014677 337 |

rent to the motor windings. Because the back EMF comparison event occurs prior to the time when optimum commutation should occur, it is preferred to delay commutation by a predetermined time after the comparison. There are two modes of commutation delay. namely adaptive or one-shot, which can be selected via the M, N bits in the MODE1 register (10) per Table 1. In Adaptive mode (default), the commutation delay is provided by a circuit which measures the interval between comparison events and delays commutation by a time equal to 3/7 of the prior measured interval. The circuit is adaptive and will provide the optimum delay for a wide range of motor speeds (-80% to 50% of the nominal value). Since the commutation of motor coils typically causes transients, the commutation delay circuit also provides a noise blanking function which prevents the circuit from responding back EMF comparison events for a period of time equal to the maximum of 5/7 of the interval between events and 64 µs after the comparison event. INCOM pin can be selected as a test pin if it is high impedance, otherwise it should be selected as "IN" for the Adaptive mode to work properly.

In one-shot mode, an input voltage at INCOM pin will provide a fixed delay and noise blank. For start-up, INCOM = VDD/2 is recommended; delay will be about 500 microseconds and noise blank about 850 microseconds. The commutation table is described in Table 2.

Motor speed control may be accomplished by measuring the period of the output signal at COM/REV. COM/REV may be defined as COMMU, the LSB of the commutation counter; REVCLK, the revolution clock of the motor; or RAWCOM, the back EMF comparator output. These are selected by the COMMUX0 and the COMMUX1 bits.

#### **Transconductance Amplifier**

Input pin VIN is the non-inverting input of a transconductance amplifier which uses the lower driver transistor, that is presently active per the commutation state, as the power driver element. An external resistor is used to sense the current flowing through the drive transistor source (and hence the motor coil current). The voltage across the sense resistor is amplified by a gain stage (Av = 5, 10, 20 or 30 selected by the GAIN bits in the MODE1 register) and fed to the inverting input of the transconductance output stage.

The 10-bit MSC D/A converter, referenced to VBG/2, is provided at SDAC for converting the commanding signal in digital format into an analog voltage. Its operation is similar to the VCM D/A converter, but is initiated by writing to the MSC D/A register (01) in two's complement form.

#### **Power Amplifier**

The output pins A, B and C are intended to drive motor coils directly. The output drivers operate to reduce switching noise transients by limiting dv/dt during commutation. Each output consists of two N-channel MOSFET drivers, one for pullup to VSMP1 or VSMP2 and one for pulldown to VSMN1 or VSMN2. The pullup FET functions as a switch (1.5 $\Omega$  maximum) with voltage rise and fall times of about 25 microseconds. The pulldown FET is a part of the transconductance amplifier (Imotor = VIN/(Rsense • Av), where Av is either 5, 10, 20 or 30). When the pulldown output is commutating to the off state, dv/dt on the respective pin is controlled such that dv/dt is approximately 15/RRAMP volts per microseconds, where RRAMP is measured in  $k\Omega$ .

**TABLE 1: Modes of Commutation Delay**

| MODE1 | 1 REGISTER (10)<br>N | SWITCH<br>MODE | DELAY<br>MODE | INCOM<br>PIN   |

|-------|----------------------|----------------|---------------|----------------|

| 0     | 0                    | NO             | Adaptive      | Test (default) |

| 0     | 1,2                  | NO             | Adaptive      | In             |

| 0     | 3                    | NO             | One shot      | In             |

| >0    | X                    | YES            | One shot      | In             |

6-50

## Servo Motor Speed 5V Driver/DACs

#### **Motor Start-Up**

Motor starting is accomplished by a companion  $\mu P$  or DSP via ADVANCE,  $\overline{RETR}$ ,  $\overline{BRAKE}$  and COM/REV. The  $\mu P$  can assert  $\overline{RETR}$  and  $\overline{BRAKE}$  low to initialize the commutation counter and then increment the counter with ADVANCE. After  $\overline{RETR}$  and  $\overline{BRAKE}$  are asserted low and de-asserted (the power-up condition for preparation to begin a starting sequence), the commutation state will be state 0 per Table 2, but the lower driver output B remains inactive to prevent current flowing through the motor (out of A which is high). On the first ADVANCE set high, the commutation state 1 is selected and the drivers are per Table 2. ADVANCE at logic high excludes internal commutations. COM/REV provides feedback to the  $\mu P$  on motor activity.

#### **Switch-Mode Operation**

Switch-mode operation is provided for limiting the motor current during motor start-up. Two values M and N, loaded into the MODE1 register (10) through the

serial interface, determines the basic switching parameters for the operation. The M (3 bits) sets the minimum "on" time of the lower drivers and sample delay time. The N (2 bits) sets the switching period. The timing is given by:

Minimum "on" time =  $(M+1) \cdot 4 \mu s$

Sample delay time = M • 4 µs

Switching period =  $(N+2) \cdot (M+1) \cdot 4 \mu s$

Hence, Minimum duty cycle = 1/(N+2)

Sample delay time, defined as the time from turning the lower drivers "on" until switching transients have settled, is a function of the particular application and will be determined by the user.

The value of M=0 is defined as Linear mode, no switching except normal commutation will occur.

| TARI | E 2. | Commutation States |

|------|------|--------------------|

|      |      |                    |

|       |       |     | Pulldown | s   |     | Pullups |     |

|-------|-------|-----|----------|-----|-----|---------|-----|

| STATE | СОММО | A   | В        | С   | A   | В       | C   |

| 0     | 0     | OFF | ON       | OFF | ON  | OFF     | OFF |

| 1     | 1     | OFF | OFF      | ON  | ON  | OFF     | OFF |

| 2     | 0     | OFF | OFF      | ON  | OFF | ON      | OFF |

| 3     | 1     | ON  | OFF      | OFF | OFF | ON      | OFF |

| 4     | 0     | ON  | OFF      | OFF | OFF | OFF     | ON  |

| 5     | 1     | OFF | ON       | OFF | OFF | OFF     | ON  |

**TABLE 3: Modes of Operation**

| STANDBY | OTSD | VCHK ><br>VBG | RETR | BRAKE | Mode          | VCM<br>Analog | SPM<br>Analog | VCM<br>Driver | SPM<br>Driver |

|---------|------|---------------|------|-------|---------------|---------------|---------------|---------------|---------------|

| x       | 0    | х             | x    | х     | Shutdown      | OFF           | ON            | Float         | Float         |

| х       | 1    | 0             | x    | 0     | Fault/Brake   | OFF           | OFF           | Retract       | Low Z         |

| х       | 1    | 0             | х    | 1     | Fault/Retract | OFF           | OFF           | Retract       | Float         |

| х       | 1    | 1             | 0    | 0     | Sleep         | OFF           | OFF           | Float         | Float         |

| х       | 1    | 1             | 0    | 1     | Retract       | OFF           | ON            | Retract       | Float         |

| x       | 1    | 1             | 1    | 0     | Brake         | OFF           | ON            | Float         | Low Z         |

| 0       | 1    | 1             | 1    | 1     | Run           | ON            | ON            | Active        | Active        |

| 1       | 1    | 1             | 1    | 1     | Standby       | OFF           | ON            | Retract       | Active        |

6-51

■ 8253965 0014679 lot ■

#### Switch-Mode Operation (continued)

For a proper switch-mode operation, three flyback diodes from outputs A, B, and C, and a blocking diode from the system power supply VCC to the VSMP1 and VSMP2 pins are required. The flyback diodes will provide power for retract (during power failure) at pins VSMP1 and VSMP2.

#### **Control Circuitry**

The control circuitry consists of a power fault detector, a thermal overload circuit, and control logic. The inputs to the control circuitry are VCHK, RETR, BRAKE, and the STANDBY bit in MODE2 register, along with the internal signals from the thermal overload detector. The voltage fault detector monitors the system power supply VCC to prevent the VCM driver from responding to a false command during a power failure. The system power supply is applied at VCHK through an external resistor divider and compared with an internal voltage reference at VBG.

Five operating modes are selected via RETR and BRAKE (when the system power supply is present) per Table 3. With RETR and BRAKE asserted low, both VCM and SPM drivers are in a high impedance state, and analog circuits are de-biased. This is the "Sleep" mode. With RETR asserted, BRAKE de-asserted, both VCM and SPM drivers are in a high impedance state, and the retract amplifier is activated and powered by the back emf of a spinning motor for retracting heads. For BRAKE asserted, and RETR de-asserted, the VCM drivers are in a high impedance state, the SPM driver outputs are low impedance to ground (without current limiting). Normal mode is given for RETR and BRAKE de-asserted and the STANDBY bit is low. When the STANDBY bit is high with RETR and BRAKE

de-asserted, the VCM driver is in retract while the SPM driver remains active. Notice that whenever VCM drivers are in either Retract or Float mode, the VCM analog circuitry is turned off except the retract amplifier.

When a power failure is sensed, the SYSRST is asserted low and the Retract mode is activated. If the die temperature exceeds approximately 135°C, the OTSD is asserted low and all output drivers (both VCM and SPM) are turned off. The drivers will become operative after the temperature is reduced and the ADVANCE is asserted high.

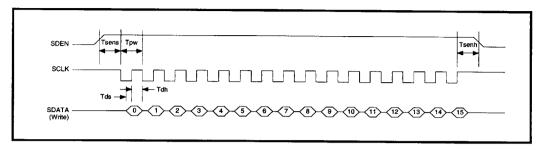

#### Serial Interface Port

A synchronous serial port, compatible with the commonly used  $\mu P$  such as 80C196 and 68HC16, is used to input digital words for D/A converters and mode registers. It is shift register based I/O interface and consists of three pins SDEN, SCLK and SDATA. Data from  $\mu P$  is transferred 8 bits (one byte) at a time with the LSB first. A complete transfer requires two bytes which are formatted into an instruction and a data field.

Data received through SDATA is clocked into an internal 16-bit shift register at the rising edge of SCLK while SDEN is active high. At the end of each transfer, SDEN must return low. If SDEN remains high after the last bit (which is the MSB of the second byte) is received, any additional data on SDATA will be ignored. Data must be two bytes for each transfer. If, for any reasons, SDEN is brought low prior to the completion of the second byte, the write operation of the data will be aborted.

The instruction field includes the first six bits of the first byte and is defined per the table below. The data field is 10-bit wide and includes the last two bits of the first byte and the second byte.

**TABLE 4: COMM/REV Selection Modes**

| COMMUX1 | COMMUXO | COM/REV Selection                          |

|---------|---------|--------------------------------------------|

| 0       | 0       | LSB of commutation state counter (default) |

| 0       | 1       | Revolution clock                           |

| 1       | х       | Back EMF comparator output RAWCOM          |

6-52

8253965 0014680 921 📟

# Servo Motor Speed 5V Driver/DACs

#### **REGISTER DESCRIPTION**

| BIT      | NAME           | DESCRIPTION                                                                                   |                                                                                                                                                 |                                                    |  |  |  |

|----------|----------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| 0 (LSB)  | R/W            | Read/Write control. It must be '0' for this device since all of its registers are write only. |                                                                                                                                                 |                                                    |  |  |  |

| 1, 2, 3  | DID02          |                                                                                               | Device ID. These three bits define the SSI device for which the serial communication is to be established. '111' is designated for this device. |                                                    |  |  |  |

| 4, 5     | ADDR01         | Register address. These two bits define the internal register to which data is transferred.   |                                                                                                                                                 |                                                    |  |  |  |

|          |                | ADDR1                                                                                         | ADDR0                                                                                                                                           | <u>Register</u>                                    |  |  |  |

|          |                | 0                                                                                             | 0                                                                                                                                               | VCM D/A                                            |  |  |  |

|          |                | 0                                                                                             | 1                                                                                                                                               | MSC D/A                                            |  |  |  |

|          |                | 1                                                                                             | 0                                                                                                                                               | MODE1                                              |  |  |  |

|          |                | 1                                                                                             | 1                                                                                                                                               | MODE2                                              |  |  |  |

| The MODE | 1 register (10 | ) is defined as:                                                                              |                                                                                                                                                 |                                                    |  |  |  |

| 0        | SWON           | Analog switch enable                                                                          |                                                                                                                                                 | ·                                                  |  |  |  |

| 1, 2     | GAIN0, 1       | Sense amplifier gain select                                                                   |                                                                                                                                                 |                                                    |  |  |  |

|          |                | GAIN1                                                                                         | GAIN0                                                                                                                                           | <u>Gain</u>                                        |  |  |  |

|          |                | 0                                                                                             | . 0                                                                                                                                             | 30 (defaut)                                        |  |  |  |

|          |                | 0                                                                                             | 1                                                                                                                                               | 20                                                 |  |  |  |

|          |                | 1                                                                                             | 0                                                                                                                                               | 10                                                 |  |  |  |

|          |                | 1                                                                                             | 1                                                                                                                                               | 5                                                  |  |  |  |

| 3        | UNIPOLAR       | Unipolar mode enable                                                                          |                                                                                                                                                 |                                                    |  |  |  |

| 4        | N0             | LSB of N value - Combination delays and basic switching r                                     |                                                                                                                                                 | ine the modes of commutation eters. (See Table 1). |  |  |  |

| 5        | N1             | MSB of N value                                                                                |                                                                                                                                                 |                                                    |  |  |  |

| 6        | MO             | LSB of M value                                                                                |                                                                                                                                                 |                                                    |  |  |  |

| 7        | M1             | M value                                                                                       |                                                                                                                                                 |                                                    |  |  |  |

| 8        | M2             | MSB of M value.                                                                               |                                                                                                                                                 |                                                    |  |  |  |

| 9        | COMMUX0        | Works with COMMU1 in MC                                                                       | DE2 register as shown                                                                                                                           | n in Table 4.                                      |  |  |  |

| The MODE | 2 register (11 | ) is defined as:                                                                              | -                                                                                                                                               |                                                    |  |  |  |

| 0        | COMMUX1        | Works with COMMUX0 in M                                                                       | ODE1 register as show                                                                                                                           | vn in Table 4.                                     |  |  |  |

| 1        | STANDBY        | Standby mode control bit, se                                                                  |                                                                                                                                                 |                                                    |  |  |  |

8253965 0014681 868 📟

# Servo Motor Speed 5V Driver/DACs

#### PIN DESCRIPTION

#### **POWER SUPPLIES**

| NAME     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                    |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPA      | -    | Analog positive supply.                                                                                                                                                                                                                                        |

| VNA      | -    | Analog ground.                                                                                                                                                                                                                                                 |

| VPD      | -    | Digital positive supply. It should be shorted externally with VPA.                                                                                                                                                                                             |

| VND      | -    | Digital ground. It should be shorted externally with VNA. VND is also the low side input to the current sense amplifier of the spindle motor and thus care should be taken to keep VND and the low side of the external resistor Rsense at the same potential. |

| VVMP *   | _    | Positive supply used for voice coil motor.                                                                                                                                                                                                                     |

| VVMN1, 2 | -    | Negative supply used for voice coil motor.                                                                                                                                                                                                                     |

| VSMP1, 2 | -    | Positive supply used for spindle motor.                                                                                                                                                                                                                        |

| VSMN1, 2 | -    | Negative supply used for spindle motor. They are also the high side inputs to the current sense amplifier of the spindle motor.                                                                                                                                |

<sup>\*</sup> The circuit board contacts for VVMP, VVMN1, VVMN2, VSMP1, VSMP2, VSMN1, and VSMN2 must be sized in accordance with anticipated motor currents. All pins must be connected with low resistance circuit board traces.

#### **SERVO POSITIONER**

| SWIN  | I | The analog switch input. The other side of the switch is connected to ERRM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ERRM  | 1 | The inverting input of the error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ERREF | I | The reference voltage for the error amplifier, the VCM D/A converter and the current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ERR   | 0 | The error amplifier output. ERR is to provide compensation to the transconductance loop and is reference to VBG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SOUT  | 0 | The current sense amplifier output. SOUT is referenced to ERREF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VRETR | 1 | The retract voltage. It must be provided externally at VRETR pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VBYP1 | 1 | The bypassed power supply. An external voltage for Brake and Retract circuits. An external capacitor is connected to this pin and BYP2 and an internal circuit will charge this pin to Vdd. The charge stored on this external capacitor is used by Brake and Retract circuits when Vdd is removed (power-off). The capacitor must hold sufficient charge during the period when Vdd is lost while retract is taking place (20 to 50 milliseconds) so it will have enough voltage to drive the outputs during braking. Very little current is used during power-off braking so that the external capacitor C can be chosen from the retract conditions: |

|       |   | C ≥ T <sub>RETRACT</sub> • I <sub>VBYP</sub> (Float mode)/0.5V or approximately:  C ≥ 40E-6 • T <sub>RETRACT</sub> This pin is normally a diode drop below Vdd, rising by VBEMF during retract.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **SERVO POSITIONER** (continued)

| NAME    | TYPE | DESCRIPTION                                                                                                                |

|---------|------|----------------------------------------------------------------------------------------------------------------------------|

| VBYP2   | - 1  | The other side of the bypass capacitor is connected to this pin. It is normally at ground, rising to VBEMF during retract. |

| VBEMF   | Ī    | Rectified spindle back emf voltage. This input provides current to the internal retract power amplifier.                   |

| VM1     | 0    | One side of the voice coil motor.                                                                                          |

| VM2     | 0    | The other side of the voice coil motor and sense resistor combination.                                                     |

| SE1,SE2 | ı    | The voltage across the sense resistor for the voice coil motor current.                                                    |

| RETR    | i    | When asserted low, it forces a retract. Refer to Table 3.                                                                  |

| PDAC    | 0    | The 10-bit VCM D/A converter output. It is referenced to ERREF.                                                            |

#### SPINDLE MOTOR COMMUTATOR/DRIVER

| SYSCLK  | 1        | System clock input. SYSCLK is internally divided by a divider to generate an internal clock. SYSCLK is nominally 8 MHz resulting in a 4 MHz internal clock. Varying SYSCLK, varies the internal clock. SYSCLK values between 6 and 10 MHz are possible.                                                                  |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COM/REV | 0        | Multiplexed output signal of COMMU, REVCLK, or RAWCOM selected through COMMUX1 and COMMUX0 bits, see Table 4.                                                                                                                                                                                                            |

| ADVANCE | l        | ADVANCE is used to increment the commutation counter externally. The rising edge of ADVANCE will increment the counter by 1. When held high, it inhibits the counter from internal incrementing. When held low, it permits the normal operation of commutation from back emf events.                                     |

| INCOM   | I        | Commutation delay control. Adaptive commutation delay may be adjusted from its nominal value of one half the commutation interval by sinking or sourcing current from this pin. This should be done via an external control loop which can compensate for the range of internal circuit parameter variations.            |

| SDAC    | 0        | The 10-bit MSC D/A converter output. It is referenced to VBG/2.                                                                                                                                                                                                                                                          |

| VIN     | 1        | Control voltage input. The combination of the MOSFET drivers and the predriver circuit forms a transconductance amplifier which sets the motor current in relation to VIN. In conjunction with Rsense connected at VSMN and the gain of the sense amplifier, the transconductance is defined by:                         |

|         |          | Gm = Im/VIN = 1/Rsense • gain, gain = 5, 10, 20, 30                                                                                                                                                                                                                                                                      |

| A, B, C | 0        | Spindle motor driver outputs.                                                                                                                                                                                                                                                                                            |

| СТ      | I        | Back emf input from spindle motor coil center tap. Internal circuit uses the back emf voltages to determine the rotor position and effect commutation.                                                                                                                                                                   |

| RRAMP   | <b> </b> | Lower driver turn-off dv/dt setting resistor. External resistor from VPA to this pin sets the dv/dt slope of the motor coil voltage when the lower drivers are commutating to the off state. The dv/dt is approximately given by the relationship: dv/dt=15/RRAMP, where dv/dt is expressed in volts/μs and RRAMP in kΩ. |

| BRAKE   | l        | BRAKE is used to provide a delay between the initiation of fault-induced head retract and spindle motor braking. A capacitor to ground and a resistor to SYSRST are selected such that 1.2RC is equal to the maximum time required for retract.                                                                          |

8253965 0014683 630 🚥

# Servo Motor Speed 5V Driver/DACs

#### **CONTROL CIRCUITRY**

| NAME   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                     |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCHK   | 1.   | Comparator input for power supply monitoring. When VCHK is below VBG, an internal voltage fault is generated.                                                                                                                                                                                                   |

| VBG    | 0    | Voltage reference, generated from the internal bandgap voltage, for use with the power supply monitor comparator.                                                                                                                                                                                               |

| IBR    | 0    | A resistor is tied from this pin to ground to establish a bias current for internal circuitry.                                                                                                                                                                                                                  |

| RCRST  | O/C  | This pin serves the dual purpose of providing power-on-reset and stretching short internal VFAULT pulses to a width suitable for the host micro controller.  An external RC network sets the minimum width of any SYSRST pulse. If RCRST is pulled low by external circuitry, this device will pull SYSRST low. |

| SYSRST | O/C  | When low, this open-collector output indicates that an internal voltage fault has occurred.                                                                                                                                                                                                                     |

| OTSD   | O/C  | Thermal shut-down. When low, this open- collector output indicates that the junction temperature has exceeded the recommended operating range and the device is in thermal shut-down. In thermal shut-down, all output drivers are turned off and analog circuit de-biased.                                     |

| THTEST | ı    | Biased low with an internal pull-down. When asserted high, RETR will be connected to the thermal overload test circuitry for use as a test input.                                                                                                                                                               |

#### **SERIAL INTERFACE PORT**

| SDATA | 1 | Serial data input passing digital words for internal registers.                                           |

|-------|---|-----------------------------------------------------------------------------------------------------------|

| SCLK  | ı | Serial data timing reference. The rising edge of the SCLK is to strobe SDATA while SDEN is asserted high. |

| SDEN  | ı | Serial data transfer enable. When active high, the serial data transfer is enabled.                       |

#### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device or affect device reliability.

| PARAMETER                               |                                            | RATING               |

|-----------------------------------------|--------------------------------------------|----------------------|

| Supply voltage @<br>VPA, VPD, VVMP, VSM | Vdd<br>IP1, VSMP2                          | -0.3 to 7.0V         |

| Motor current @<br>A, B, C, VM1, VM2    | lmax                                       | ±1.0 A               |

| Max Output Current Du                   | ration Ta = 70°C<br>Output Current = 1.0 A | 8 seconds            |

| Input voltage @                         |                                            |                      |

|                                         | CT, A, B, C, VBEMF, VBYP1, VBYP2           | -0.3 to 12.0V        |

|                                         | VM1, VM2, SE1, SE2                         | -0.3 to 7.0V         |

|                                         | Other pins                                 | -0.3 to (Vdd + 0.3)V |

| Storage temperature                     | Tstg                                       | -65 to 150°C         |

| Lead temperature (10 sec duration)      | Tlead                                      | 0 to 300°C           |

#### RECOMMENDED OPERATING CONDITIONS

The recommended operating conditions for the device are indicated in the table below. Performance specifications do not apply when the device is operated outside the recommended conditions.

| PARAMETER                    |           | CONDITIONS | MIN | NOM | MAX     | UNIT |

|------------------------------|-----------|------------|-----|-----|---------|------|

| Supply voltage               | Vdd       |            | 4.5 |     | 5.5     | V    |

| Supply current               |           |            |     |     |         |      |

| VPA,VPD                      | ldd       |            |     |     | 20      | mA   |

| Sleep mode                   | Isleep    |            |     |     | 2.0     | mA   |

| Standby mode                 | Istandby  |            |     |     | 15      | mA   |

| VBYP1,braking                | lbrk      |            |     |     | 10      | μΑ   |

| VBYP1,retract                | Iret      |            |     |     | 20      | μΑ   |

| Input voltage @ VBEMF        | VBEMF     |            | 1.0 |     | 10      | ٧    |

| Input voltage @ ERREF        | ERREF     |            | 0.5 | VBG | Vdd-2.0 | ٧    |

| Input voltage @ VIN          | VIN       |            | 0   |     | 2.5     | V    |

| Input voltage @ VSMN         | VSMN      |            | 0   |     | 0.5     | ٧    |

| ADVANCE active low pulse     | width     |            | 0.1 |     | 12      | μs   |

| Ambient temperature          | Ta        |            | 0   |     | 70      | °C   |

| Capacitive load on digital o | utputs CI |            |     |     | 100     | pF   |

#### **RECOMMENDED OPERATING CONDITIONS (continued)**

| PARAMETER                     |          | CONDITIONS | MIN | NOM | MAX | UNIT |

|-------------------------------|----------|------------|-----|-----|-----|------|

| Analog output load            | CI       |            |     |     | 40  | pF   |

|                               | RI       |            | 10  |     |     | kΩ   |

| System clock                  |          |            |     |     |     |      |

| Frequency tolerance           | fc       |            | 6   |     | 10  | MHz  |

| Pulse width                   | Twh, Twl |            | 40  |     |     | ns   |

| Biasing resistor Rbias = 22.6 | Ω Rbias  |            | 22  |     | 24  | kΩ   |

| External resistors            | Rf,Rc    |            | 10  |     |     | kΩ   |

#### PERFORMANCE SPECIFICATIONS

#### DIGITAL I/O

| Digital input @ SDATA, SCLK, S | SDEN,    |               |     |     |    |

|--------------------------------|----------|---------------|-----|-----|----|

| ADVANCE, SYSCLK, RETR          | Vil      |               | 0.8 |     | V  |

|                                | Vih      |               |     | 2.0 | ٧  |

|                                | lil, lih |               |     | ±1  | μΑ |

| Digital input @ BRAKE          | Vil      |               | 1.2 |     | V  |

|                                | Vih      |               |     | 2.4 | V  |

|                                | lil, lih |               |     | ±1  | μА |

| Digital O/C output @ RCRST,    | loh      | Voh = Vdd     |     | 1   | μА |

| SYSRST, OTSD                   | lol      | Voi = 0.4     | 4   |     | mA |

| Digital Output @ COM/REV       | Vol      | lol = 2.0 mA  |     | 0.4 | V  |

|                                | Voh      | loh = -100 μA | 2.4 |     | ٧  |

## Servo Motor Speed 5V Driver/DACs

#### **SERVO POSITIONER**

The following VCM performance specifications are measured with  $16\Omega$  resistive load and  $0.5\Omega$  sense resitor for 8 MHz SYSCLK, unless otherwise noted.

| PARAMETER                                                | CONDITIONS                                        | MIN  | NOM      | MAX      | UNIT |

|----------------------------------------------------------|---------------------------------------------------|------|----------|----------|------|

| BEMF current                                             |                                                   |      |          |          |      |

| Normal mode                                              | VBEMF = 4V                                        |      |          | 300      | μА   |

| Retract mode                                             | VBEMF = 3V, Power off<br>VRETR = 0.5V, VBYP1 = 4V |      |          | 20       | μА   |

| SOUT amplifier                                           |                                                   |      |          |          |      |

| Gain                                                     |                                                   | 3.9  |          | 4.1      | V/V  |

| Input offset                                             | SOUT = ERREF                                      | -3   |          | 3        | mV   |

| Output swing                                             | $R_i = 10 \text{ k}\Omega \text{ to ERREF}$       | 0.15 |          | Vdd-1    | V    |

| ERRAMP amplifier                                         |                                                   |      | <u> </u> |          |      |

| Input offset                                             | ERR = ERRM                                        |      |          | ±15      | mV   |

| Output swing                                             |                                                   | 0.15 |          | Vdd-1.25 | ٧    |

| Gain                                                     |                                                   | 60   |          |          | dB   |

| Unit Gain Bandwidth                                      |                                                   | 1    |          |          | MHz  |

| Power amplifier (VCM Driver) Gain (VM1-VM2)/(ERR-VBG)    |                                                   | 11   |          | 13       | V/V  |

| Output voltage drop                                      | Imotor = 0.2A                                     |      |          | 0.5      | V    |

| VCM transconductance                                     |                                                   | 0.4  |          | 0.6      | A/V  |

| Bridge crossover time                                    |                                                   |      |          |          |      |

| lvcm = 10 mA, pk                                         | Step input                                        | •    |          | 10       | μs   |

| VCM output THD                                           |                                                   |      |          |          |      |

| lvcm=100 mA, pk @ 100 Hz                                 | $R_i = 16\Omega$                                  |      |          | 2        | %    |

| SWIN on resistance                                       |                                                   |      |          | 250      | Ω    |

| Retract amplifier (retract),<br>VRETR = 0.5V, VBEMF ≥ 1V |                                                   |      |          |          |      |

| offset                                                   |                                                   | -100 |          | 0        | mV   |

| Maximum output current,<br>VRETR = 0.5V, VBYP1 = 4.5V    |                                                   |      |          |          |      |

| VBEMF = 1V, VM1 = VM2                                    |                                                   | 60   |          |          | mA   |

| VBEMF = 1.5V, VM1 = VM2                                  |                                                   | 100  |          |          | mA   |

| Retract Amplifier (normal)                               |                                                   |      |          |          |      |

| VRETR leakage                                            |                                                   |      |          | ±1       | μА   |

6-59

## SSI 32H6811/6811B Servo Motor Speed

### 5V Driver/DACs

| SPINDLE MOTOR | COMMUTAT | OR/DRIVER |

|---------------|----------|-----------|

|               |          |           |

| PARAMETER                               | CONDITIONS             | MIN | NOM | MAX  | UNIT |

|-----------------------------------------|------------------------|-----|-----|------|------|

| Input current @ VIN                     | 0 ≤ VIN ≤ 2.5V         |     |     | ±1   | μΑ   |

| Total FETs voltage drop                 | Imotor = 0.5A          |     |     | 0.85 | ٧    |

| Outputs @ CT, A, B, C while not driving |                        |     |     |      |      |

| Rin                                     | -0.3V ≤ Vin ≤ 7V       | 10  |     |      | kΩ   |

| Outputs @ CT while not driving          |                        |     |     | 1    |      |

| Rin                                     | $-0.3V \le Vin \le 7V$ | 3   | İ   |      | kΩ   |

#### **CONTROL CIRCUITRY**

| Vdd voltage for SYSRST<br>& RCRST in operation |                | 2    |     | 5.5  | ٧  |

|------------------------------------------------|----------------|------|-----|------|----|

| VBG                                            | lout < ±0.2 mA | 2.13 |     | 2.37 | V  |

| VCHK comparator offset                         |                |      |     | ±15  | mV |

| Thermal shutdown                               |                |      |     |      | Ì  |

| Temperature threshold                          |                |      | 125 | İ    | ∘c |

#### D/A CONVERTER

| Full-scale voltage        | VBG      | V    |

|---------------------------|----------|------|

| Resolution                | 10       | bits |

| Digital Delay             | 4        | μs   |

| LSB volatge               | VBG/1024 | V    |

| Differential nonlinearity | ±1       | LSB  |

#### SERIAL INTERFACE PORT

| SDEN setup time prior to SCLK       | Tsens | 35  | ns |

|-------------------------------------|-------|-----|----|

| SDEN hold time after SCLK           | Tsenh | 50  | ns |

| SDATA setup time prior to SCLK rise | Tds   | 15  | ns |

| SDATA hold time after SCLK fall     | Tdh   | 15  | ns |

| SCLK pulse width                    | Tpw   | 100 | ns |

6-60

FIGURE 2: SSI 32H6811 Serial Interface Timing Diagram

#### **APPLICATIONS INFORMATION**

FIGURE 3: Power Dissipation Derating

6-61

**■** 8253965 0014689 059 **■**

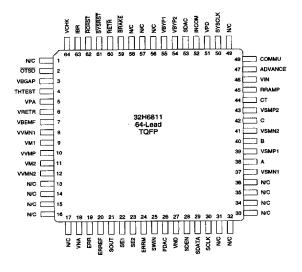

#### PACKAGE PIN DESIGNATIONS

(Top View)

CAUTION: Use handling procedures necessary for a static sensitive component.

**64-LEAD TQFP**

Advance Information: Indicates a product still in the design cycle, and any specifications are based on design goals only. Do not use for final design.

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680-7022 (714) 573-6000, FAX (714) 573-6914

©1993 Silicon Systems, Inc.

6-62

0594 - rev.

**8253965 0014690 870**