#### Introduction

The L64765 Color and Raster-Block Converter performs two main functions: color conversion among RGB, YCbCr, and Y-only formats; and reformatting between raster-ordered and block-ordered image data. The L64765 can be used either as a preprocessor in image encoding systems, or a reconstructor in decoding systems.

Image data can be supplied to the L64765 in nine formats to ensure compatibility with most standard video devices.

Three internal correction tables apply a transformation to each color at the RGB interface. This transformation is typically a gamma correction. Data in the correction tables is downloaded to the L64765.

The color conversion is performed by a fixed digital matrix defined to convert between RGB and YCbCr as defined by the CCIR Recommendations 601, Mod F. A range limiter forces out-of-range data values into the usable range. Color conversion can be bypassed.

The L64765 includes internal resampling filters that downsample YCbCr data into a 2:1:1 ratio in the encoder direction and reconstruct the data in the decoder direction.

The raster-block reformatting uses an external strip memory to store eight scan lines. The L64765 includes an internal buffer RAM to assist in the reformatting process. The L64765 supports an 8x8 block format, and can process scan lines

L64765 Die Photograph

up to 8192 pixels wide. Raster-block reformatting can be bypassed.

The L64765 is a member of the JPEG image compression chipset, which also includes the L64735 DCT Processor and the L64745 JPEG Coder. These three devices provide a complete solution for compression or decompression of digital raster-scanned RGB data to coded bit stream. When combined with a small number of external memory and support devices, these chips implement a complete still-image compression and decompression system.

## **Features**

- Performs raster-to-block or block-to-raster conversion

- Performs color space conversions in either direction:

- RGB-to-YCbCr or YCbCr-to-RGB

- RGB-to-Y-only or Y-only-to-RGB

- YCbCr-to-Y-only or Y-only-to-YCbCr

- Applies gamma correction from user-defined internal gamma correction tables

- Supports nine image data formats

- Support eight scan lines up to 8192 active pixels wide

- Supports user-programmable active window area synchronized to video sync signals

- Interfaces directly to LSI Logic L64735 DCT Processor

- Implements CCIR Recommendation 601, Mod F, for color space conversion

- Supports 2:1:1 downsampling with decimation and interpolation

- Operates at 27 MHz clock speed

- Is supplied in 100-pin ceramic pin-grid array (CPGA) package

©1991 LSI Logic Corporation

Pre-release Version, May 15, 1991

Order Number L64765

## System Applications

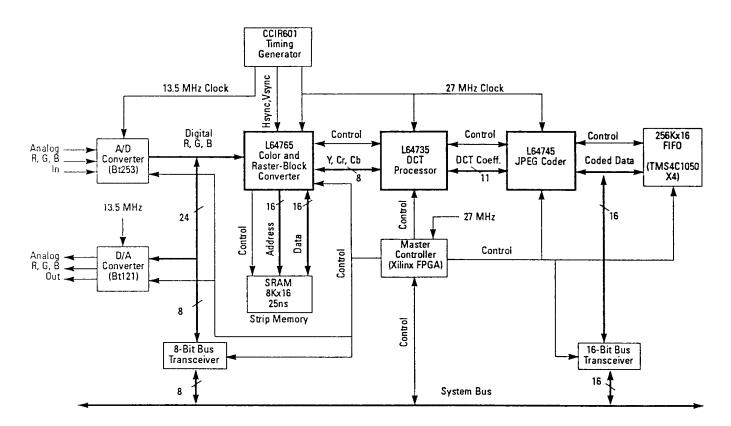

Figure 1 shows a typical system application of the L64765. This system design supports encoding and decoding applications. The example shows the use of the other members of the JPEG chipset, the L64735 DCT Processor and the L64745 JPEG Coder. The text following the figure describes the function of the devices in the example.

Figure 1. Typical Video Real-Time Image Processing Application

In encoding applications, the A/D Converter converts analog input RGB data into 24-bit digital RGB data for input to the L64765. The L64765 converts RGB values to luminance (Y) and chrominance ( $C_b$ ,  $C_r$ ) components and arranges the raster image into 8x8 blocks. The Strip Memory buffers eight lines of the raster-scanned image to assist in the raster-to-block conversion. The L64735 DCT Processor performs a discrete cosine transform on the 8x8 blocks to produce DCT coefficients. The L64745 JPEG Coder quantizes and encodes the DCT coefficients into a compressed data stream.

The FIFO stores the compressed data stream. In the application shown, the FIFO provides 512 Kbytes of storage for the compressed image. At a typical 24:1 compression ratio, this memory can store an image as large as 12 Mbyte, or 16 NTSC images (512 X 480 X 24).

The Master Controller provides all control signals and performs the handshaking between the host and the L64745, and the host and the FIFO. The Master Controller initializes all three chips in the chipset and controls the transfer of data between the L64745 and the FIFO, and the FIFO and the system bus.

In decoding applications, the data flow is reversed. The *D/A Converter* converts the digital RGB image data from the L64765 into analog RGB data.

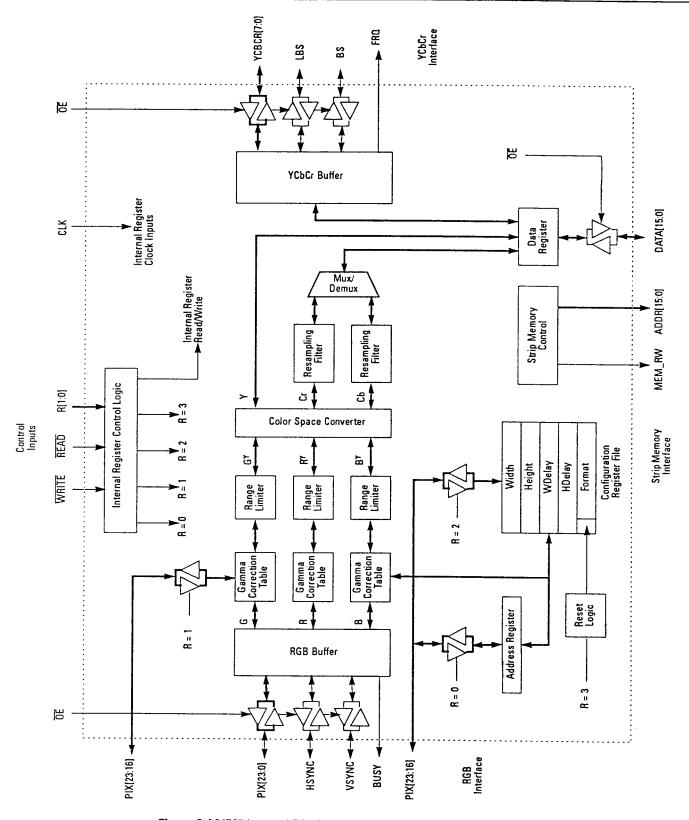

Figure 2. L64765 Internal Block Diagram

## **Functional Overview**

Figure 2 is a block diagram showing major functional blocks of the L64765. Bold lines indicate buses (more than one signal).

## **RGB** Interface

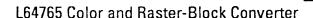

The RGB interface operates at a sample rate of at least 13.5MHz. These bidirectional lines are configured as either inputs or outputs depending on the direction of the conversion. The RGB interface reads or writes data in one of the data formats described below. The data format used by the L64765 is set in the Format Register described later in "Control Registers."

## ■ 24 bit RGB

Twenty four bits of RGB data (8 bits each) are transferred on the RGB interface at rates up to 13.5 M samples/sec. The original source signal is assumed to be band-limited and in the range 0-255 for each component.

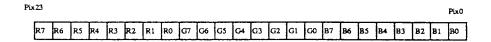

## 24 bit YCbCr

Twenty four bits of YCbCr data (8 bits each) are transferred on the RGB interface. The sample rate of the signal is 13.5MHz or greater. Y,Cr and Cb are all unsigned, Cr and Cb being level shifted by +128. The original source signal is assumed to be band-limited and in the range 0-255 for each component.

## ■ 16 bit YCbCr (4:2:2 or 2:1:10

This mode is compatible with the Phillips SAA7151 and SAA7197 digital television decoders and Brook-tree VideoNet transceivers. The Cr and Cb data is time multiplexed onto the same eight pins since it is already sampled at half the frequency of Y. Cr and Cb are level shifted and range limited as above. The first active pixel on each scan line is always a Y-Cb pair.

| Pi       | x 23 |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |     |     |     |     |     |     |     | Pix0 |

|----------|------|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|------|

| t<br>t+l | х    | х | х | х | х | х | х | х | Y7 | Y6 | Y5 | Y4 | Y3 | Y2 | Υl | YO | Съ7 | C56 | Ст  | Съ4 | Съз | Съ2 | Сы  | Сю   |

|          | х    | х | х | х | х | х | x | х | ۲7 | Y6 | Y5 | Y4 | Y3 | Y2 | Υı | YO | Cr7 | Стб | Cr5 | C-4 | Cr3 | Cr2 | Crl | Сю   |

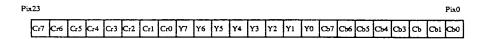

## ■ 16 Bit RGB

Three 16-bit RGB formats are commonly implemented in graphics systems. In RGB order these are (X,5,5,5), (6,6,4) and (5,6,5).

#### ■ 32 Bit RGB

Two 32-bit RGB formats are supported. In each case, each pixel is represented by eight bits; the most significant eight bits are always unused. These modes differ from the 24-bit RGB mode in that the data is multiplexed onto the lower 16 bits of the RGB interface on alternate cycles.

## **RGB**

| t   | х | х | х | х | x | х | х | х | <b>G</b> 7 | G6 | G5 | G4 | G3 | G2 | Gl | GO | R7         | R6 | R5 | R4 | R3 | R2 | R1 | RO |

|-----|---|---|---|---|---|---|---|---|------------|----|----|----|----|----|----|----|------------|----|----|----|----|----|----|----|

| t+1 | х | x | х | х | х | х | х | х | х          | х  | х  | х  | х  | х  | х  | х  | <b>B</b> 7 | 86 | B5 | B4 | B3 | В2 | Bi | во |

| BGR |   |   |   |   |   |   |   |   |            |    |    |    |    |    |    |    |            |    |    |    |    |    |    |    |

| t   | х | х | x | х | х | x | х | х | <b>G</b> 7 | G6 | GS | G4 | G3 | G2 | Gı | GO | <b>B</b> 7 | В6 | B5 | В4 | B3 | B2 | Bl | B0 |

| t+1 | х | х | х | х | х | х | х | х | x          | х  | х  | х  | х  | х  | х  | х  | <b>R</b> 7 | R6 | R5 | R4 | R3 | R2 | RI | RO |

## **Gamma Correction Tables**

Each channel can be transformed by a user-defined function, e.g., gamma correction. The function is stored in an independent 256 X 8 lookup table for each channel. The lookup tables can be read or written as described later in "Initialization and Control."

## **Color Space Converter**

Color space conversion is performed by a digital matrix. To allow the same matrix to be used for CCIR-compatible YCbCr data streams and RGB data streams, data in either form must be in the range 16-235. If input data falls outside this range, the range limiters clamp the data to the appropriate boundary value.

The color conversion matrix may be bypassed in either direction to allow systems with images already in YCbCr space to use the raster to block conversion function.

The RGB-to-YCbCr and YCbCr-to-RGB matrices are defined in the CCIR601 specification. The matrices for these conversions are shown in Figure 3 and Figure 4 below.

$$Y = (77/256)R + (150/256)G + (29/256)B$$

$$Cr = (131/256)R - (110/256)G - (21/256)B + 128$$

$$Cb = (-44/256)R - (87/256)G + (131/256)B + 128$$

Figure 3. RGB-to-YCbCr Matrix

$$R = Y + 1.370 (Cr - 128)$$

$$G = Y - 0.698 (Cr - 128) - 0.336 (Cb - 128)$$

$$B = Y + 1.730 (Cb - 128)$$

## Figure 4. YCbCr-to-RGB Matrix

## **Resampling Filters**

The resampling filters implement one of two built-in transfer functions depending on the direction of the conversion. In the forward (RGB-to-YCbCr) direction, the filters downsample the RGB components in a 2:1:1 ratio. The built-in forward transfer function H uses the values of the current pixel  $Z_0$  and the two adjacent pixels  $Z_1$  and  $Z_1$ . The first and last pixel in each scan line are not filtered. Figure 5 shows the forward transfer function.

$$H(Z) = (128/256)Z^{0} + (64/256)(Z^{-1} + Z^{1})$$

# Figure 5. Resampling Filter Forward Transfer Function

In the reverse (YCrCB-to-RGB) direction, the pixel value is reconstructed based on the values of the adjacent pixels. The first and last pixel in each scan line require no reconstruction. Figure 6 shows the reverse transfer function.

$$H(Z) = (128/256)(Z^{-1} + Z^{1})$$

## Figure 6. Resampling Filter Reverse Transfer Function

In some pixel formats, the resampling filters are automatically bypassed. See "Control Registers" for more information on pixel formats.

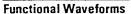

## **Strip Memory Interface**

Raster data is stored in an external strip memory to facilitate raster-to-block conversion. Since a 16 bit YCr/Cb pixel must be read and written every 74 ns at 13.5 MHz, the strip memory interface is 16 bits wide for a cycle time of 37 ns. 25ns RAMs can be used in the strip memory. In sustained operation a pixel is first read from the memory before a new raster sample is written to the same address. After eight scan lines have been written, the process is repeated. The read-then-write scheme reduces the number of addressing operations and increases the utilization of the strip memory.

The 16-bit address bus can access up to 64K pixels. This memory addressing range is enough to support eight 17-inch scan lines at 300 dpi (40,800 pixels). However, the system configuration need only include the amount of memory that will actually be used. The L64765 always uses the minimum amount of memory as shown in the equation below, where M is the memory size in 16-bit words and width is the width of the active window in pixels:

$$M = 8 \times width$$

For example, an image 512 pixels wide requires a strip memory of 4K (4,196) 16-bit words.

Addresses are always generated starting at zero after reset.

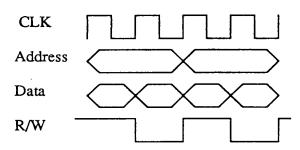

The memory access cycle is optimized for static RAMS. The read/write cycle occurs every 2 CLK cycles. The memory cycle is fully synchronous with respect to the device clock. Figure 7 shows the memory access cycle.

Figure 7. Memory Access Timing

The active image area is restricted to contain only complete MCUs (minimum coded units). In the L64765, an MCU contains two data blocks of the luminance component and one data block each of the two chrominance components (2:1:1). An MCU is 8 pixels high by 16 pixels wide.

## YCbCr Interface

The YCbCr interface transfers the reformatted and subsampled data to and from the L64735 DCT Processor. The 8-bit wide data bus is organized in 8x8 blocks for the L64735 DCT Processor. An optional Y only mode is supported by forcing the Cr and Cb components to zero. This allows the YCbCr interface to operate at the same rate regardless of mode. The sustained data transfer rate is 2x(sample frequency). The raster to block conversion function and 2:1:1 data reformatting may be optionally bypassed. In this case data on the YCbCr interface is in the format YCbYCr; i.e. a time-multiplexed raster-ordered signal similar to the one described in CCIR 601.

## **External Interface**

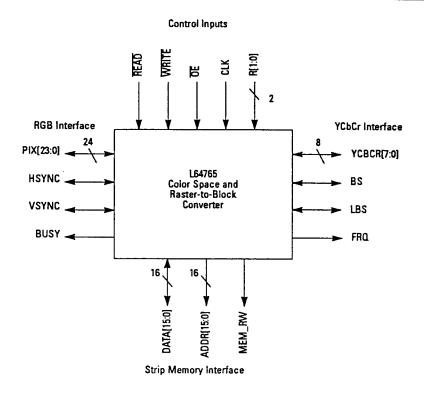

The external interface to the L64765 consists of the signals shown in Figure 8. Each signal is described in the text following the figure.

Figure 8. L64765 Logic Symbol

#### **RGB Interface Signals**

These signals comprise the interface to the digital RGB signals.

## PIX[23:0]

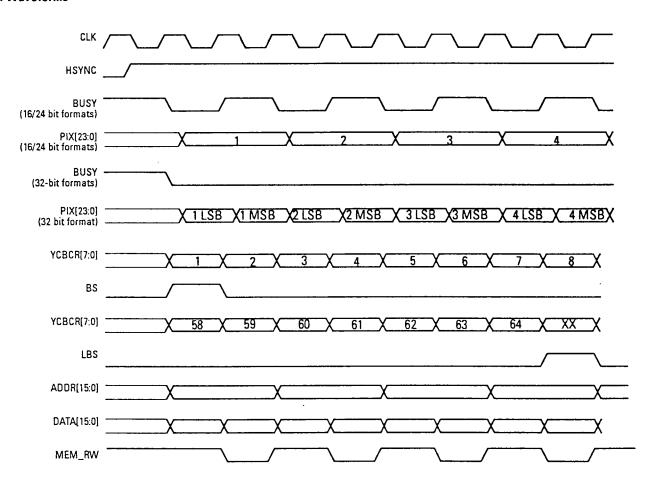

24 bit RGB interface data I/O. In encode mode, PIX[23:0] are inputs. In decode mode, PIX[23:0] are outputs. Data on PIX[23:0] is translated according to the control bits in the format control register. The upper 8 bits of this bus, PIX[23:16], are used to read from and write to the internal control registers. See "Control Registers" for more information.

# **HSYNC**

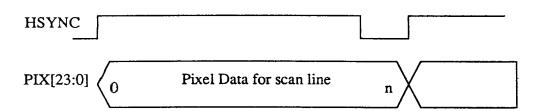

A positive-going pulse indicates to the L64765 that the input data source has reached the beginning of a scan line. HDelay is measured from HSYNC going HIGH. HSYNC is synchronous with respect to the device clock CLK. HSYNC is allowed to go low before all the pixels in a scan are sampled so that images without a line flyback interval may be handled. HSYNC is an input in both encode and decode mode, except in decode raster mode when HSYNC is an output. In block decode mode the L64765 uses inputs HSYNC and VSYNC to sync the device to the external video source.

Figure 9. HSYNC Timing for Image with No Horizontal Flyback Interval

#### **VSYNC**

A positive-going input pulse indicates that the beginning of a frame has been reached. VDelay is measured from VSYNC going high. The L64765 uses a combination of VSYNC and the active display area to determine when LBS is to be asserted. As above, VSYNC may be asserted before the last scanline of the image is reached to deal with the case of image scanners with no vertical retrace interval. VSYNC is assumed synchronous with respect to the device clock, and is an input in both encoder and decoder mode, except decode raster mode where it is an output.

## BUSY

In encoder operation, the L64765 asserts BUSY (HIGH) to inhibit the input of data on the PIX bus.

## Strip Memory Interface

These signals comprise the interface between the L64765 and the external 16-bit wide strip memory.

## DATA[15:0]

16 bit bidirectional data bus. DATA[15:0] are used to read and write data to the strip memory.

## ADDR[15:0]

16 bit address output bus. ADDR[15:0] selects the address of the strip memory.

## MEM\_R/W

Read/Write output. MEM\_R/W designates a strip memory operation as a read or write cycle. MEM\_R/W is asserted HIGH for read operations and deasserted LOW for Write.

## YCbCr Interface

These signals comprise the interface between the L64765 and the portion of the system that processes YCbCr data. In a typical system such as the one shown previously in "System Applications," these signals interface directly to the L64735 DCT Processor.

## YCBCR[7:0]

8 bit subsampled data I/O bus. Data on this bus is presented in the 2:1:1 format used by the L64735 in JPEG blocking mode, or in YCbYCr time-multiplexed format in raster mode. YCBCR[7:0] are bidirectional, operating as outputs in encoder mode and as inputs in decoder mode.

## BS

Block Start. BS indicates the beginning of a new block of input or output samples on YCBCR[7:0] during JPEG blocking mode. BS is always coincident with the first pixel of the block. In raster mode it is a copy of HSYNC, delayed by the pipeline delay of the L64765.

## LBS

Last Block Strobe. LBS indicates that the last block of an image was just passed over YCBCR[7:0]. LBS is asserted on the first sample *after* the last pixel in the active window is presented on YCBCR[7:0]. In encode mode, LBS is generated by the L64765 after processing of the last block in the image window. In decode mode, LBS is typically generated by the L64745. In raster mode, LBS is a copy of VSYNC delayed by the pipeline delay of the L64765 in both the encode and decode direction

#### FRQ

Freeze Request output. FRQ controls the optional external gating of the device clocks to the L64735 and L64745 so that data flow is correctly controlled during horizontal and vertical blanking intervals.

#### **Control Inputs**

These input signals comprise the control interface to the L64765.

## R[1:0]

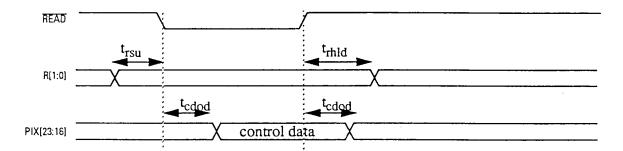

Register address input bits. R[1:0] set the internal register or table being accessed during a read or write operation as shown in Table 1.

## READ

Active low signal. When READ is asserted, the L64765 initiates a read operation from the internal register or table indicated by R[1:0]. Reading from the Gamma Table or Initialization Table registers causes the data pointed to by the current value of the address register to be read. The address register increments after each read.

## WRITE

Active low signal. Data is written to the control register indicated by R[1:0] on the rising edge of WRITE.

## ŌĒ

Active low output enable pin. When OE is LOW, PIX[23:0] and YCBCR[7:0] are 3-stated.

#### CLK

The L64765 is clocked on the rising edge of CLK.

## **Control Registers**

The L64765 uses PIX[23:16], the eight most significant bits of the PIX bus, to access the internal control registers. An external eight-bit bidirectional buffer is required to prevent contention between the external bus and the 8 most significant bits of the PIX bus (PIX[23:16]) during normal operation. Register loading is asynchronous with respect to the L64765 clock. The register select inputs [R0,R1] select the internal register or table to be accessed as shown in Table 1. The access is performed when READ or WRITE are asserted.

Table 1. R[1:0] Meaning

| R[1:0]               | Accesses:                                                                  |

|----------------------|----------------------------------------------------------------------------|

| 00<br>01<br>10<br>11 | Address Register Gamma Correction Tables Configuration Register File Reset |

## **Address Register**

The Address Register functions as a pointer to an internal location. The control inputs R[1:0] determine whether the Address Register points to an entry in a gamma table or a register in the configuration register file. To write a new value into the Address Register:

- 1. Place the address value on PIX[23:16].

- 2. Set R[1:0] to 00. (Steps 1 and 2 can be done in either order).

- 3. Assert WRITE. The address value is stored in the Address Register on the rising edge of WRITE.

## **Gamma Correction Tables**

The L64765 has three separate gamma correction tables, one each for the R,G, and B digital inputs. Each table holds 256 entries. The Address Register points to a gamma address when R[1:0] is set to 01. The data written to a gamma address must be written in order: Red, Green, then Blue. Once the Blue value has been written, the Address Register automatically increments. The sequence for writing the complete gamma tables is:

- Set the address register to 0x00 as described earlier in "Address Register."

- 2. Set R[1:0] to 01. The address register now points to address 00 of the R gamma table.

- 3. Place the Red value on PIX[23:16] and assert WRITE for one CLK cycle. This writes the value into the Red gamma table.

- 4. Write the Green value in the same way as the Red.

- 5. Write the Blue value in the same way as the Red. Once the Blue value is written, the Address Register automatically increments to 0x01.

- 6. Repeat steps 3, 4, and 5 until all 256 entries (address = 0xFF) have been written to all three tables.

Partial write operations are allowed: the Address Register can be set to any gamma table address, and the write operation does not have to go to the highest address (0xFF). However, for each gamma table address, the write operation must begin with Red.

## **Configuration Registers**

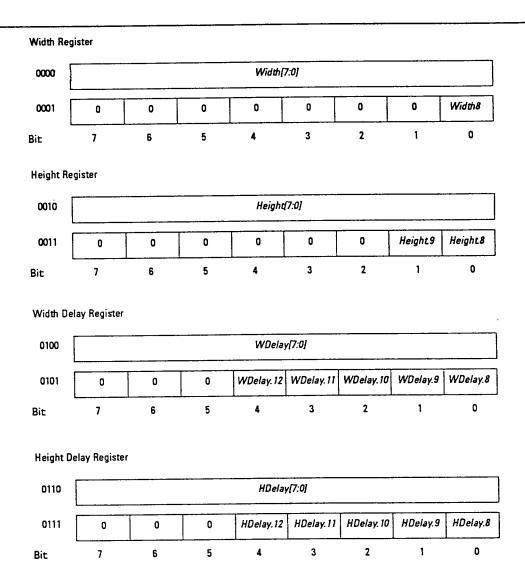

The L64765 contains five internal configuration registers. The Format Register sets the format of the input RGB data on the PIX bus and controls other aspects of device operation. The four window control registers, Width, Height, WDelay, and HDelay, control the active window area of the image.

The configuration registers are addressed in the same manner as the correction tables. For all registers except the Format register, two load operations are required to write the full contents of the register. The less significant byte is always written first to the address shown in Table 2. The more significant byte is written to the next address. The address of each configuration register is shown in Table 2.

**Table 2 Configuration Register Addresses**

| Address  | Register | # of Loads Required |

|----------|----------|---------------------|

| XXXX0000 | Width    | 2                   |

| XXXX0010 | Height   | 2                   |

| XXXX0100 | WDelay   | 2                   |

| XXXX0110 | HDelay   | 2                   |

| XXXX1XXX | Format   | 1                   |

## Format Register

The Format Register is accessed by any address with PIX.19 set to 1 and R[1:0] equal to 10<sub>2</sub>. Figure 10 shows the content of the Format Register. Descriptions of the meaning of each field follow the figure.

| Register Bit | 7  | 6   | 5   | 4 | 3 | 2   | 1 | 0 |

|--------------|----|-----|-----|---|---|-----|---|---|

|              | Go | 0EN | Enc |   |   | Fmt |   |   |

Figure 10. Format Register

## Go Go Control

Go controls the start of frame processing. Go must be set before frame processing can begin.

In encode mode, the L64765 is enabled for frame processing when Go is set to one. The L64765 waits for the first pixel of the active window to begin processing.

In decode mode, the L64765 starts sampling the BS pin and filling the strip memory as appropriate. Once the strip memory is filled the L64765 waits until the first pixel of the active window before outputting the data on the PIX bus.

If Go is cleared to zero, the FRQ pin is reset to LOW. In encode mode, BS and LBS are deasserted to LOW. In decode mode, BS and LBS are ignored.

## OEN Output Enable Control

OEN controls the state of all bidirectional signals. When OEN is set to one, all bidirectional signals are disabled. The  $\overline{OE}$  input pin also disables the bidirectional signals; see "Pin Descriptions." For the bidirectional signals to be enabled, both OEN must be set to zero, and the  $\overline{OE}$  pin must be deasserted (HIGH).

# Enc Code Operation Control

Enc controls the direction of data flow. When Enc is set to one, the data input is from the PIX bus, and data output is on the YCBCR bus. When Enc is reset to zero, the dat input is from the YCBCR bus, and data output is on the PIX bus.

#### Fmt Format Control

Fmt is a five-bit field that controls how the L64765 interprets the PIX and YCBCR buses. Table 3 shows the meaning of the Fmt field.

Table 3. FMT[4:0] Meaning

| FMT[4:0] | PIX[23:0]       | Order       | YCBCR[7:0]          | Filter    |             |

|----------|-----------------|-------------|---------------------|-----------|-------------|

| 10000    | 16-bit YCbCr    | Raster      | YCbYCr              | No Filter | S           |

| 00000    | 16-bit YCbCr    | Block       | YYCbCr              | No Filter | YCbCr Modes |

| 10001    | 24-bit YCbCr    | Raster      | YCbYCr              | Filter    | Ž           |

| 00001    | 24-bit YCbCr    | Block       | YYCbCr              | Filter    | Ş           |

| 11001    | 16/24-bit YCbCr | Raster      | YCbYCr1             | No Filter | 12          |

| 01001    | 16/24-bit YCbCr | Raster Biog | ,                   | No Filter |             |

| 10010    | (8,8,8) RGB     | Raster      | YCbYCr              | Filter    | 1           |

| 00010    | (8,8,8) RGB     | Block       | YYCbCr              | Filter    | es          |

| 10011    | (5,5,5) RGB     | Raster      | YCbYCr              | Filter    | Modes       |

| 00011    | (5,5,5) RGB     | Block       | YYCbCr              | Filter    | GBN         |

| 10100    | (6,6,4) RGB     | Raster      | YCbYCr              | Filter    | RG          |

| 00100    | (6,6,4) RGB     | Block       | YYCbCr              | Filter    | cycle       |

| 10101    | (5,6,5) RGB     | Raster      | YCbYCr              | Filter    | 5           |

| 00101    | (5,6,5) RGB     | Block       | YYCbCr              | Filter    | -           |

| 11010    | (8,8,8) RGB     | Raster      | YCbYCr <sup>1</sup> | Filter    |             |

| 01010    | (8,8,8) RGB     | Block       | YYCbCr <sup>1</sup> | Filter    | س ا         |

| 10110    | (X,8,8,8) RGB   | Raster      | YCbYCr              | Filter    | RGB         |

| 00110    | (X,8,8,8) RGB   | Block       | YYCbCr              | Filter    | le I        |

| 10111    | (X,8,8,8) BGR   | Raster      | YCbYCr              | Filter    | cycle       |

| 00111    | (X,8,8,8) BGR   | Block       | YYCbCr              | Filter    | 7           |

Note:

1. In these formats, Cb and Cr data are set to zeroes.

Window Control Registers

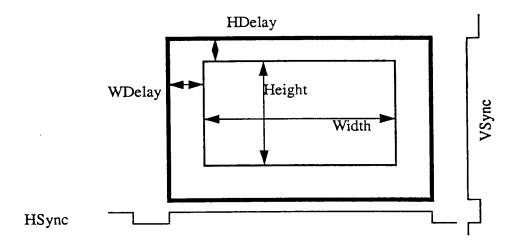

The Window Control registers contain the values of four parameters: Width, Height, WDelay, and HDelay. Each Window Control register is 16 bits wide. The bits that are not used return zeros when read. Figure 11 shows the format of each register. The fields are defined in the text following the figure.

Figure 11. Window Control Registers

## Width[8:0] Image Width

The width of the active image area in multiples of 16 pixels. The L64765 supports images up to 8192 pixels or 512 MCUs wide (1 MCU is 16 pixels wide).

## Height[9:0] Image Height

The height of the active image area in multiples of 8 pixels. The L64765 supports images up to 8192 pixels 1024 MCUs high (1 MCU is 8 pixels high).

## WDelay[12:0]Width Delay

The delay in pixels from the horizontal sync pulse to the first active pixel. WDelay[12:0] is in the range 0 to 8191.

## HDelay[12:0] Height Delay

The delay in scan lines from the vertical sync pulse to the first active scan line. HDelay[12:0] is in the range 0 to 8191.

The four parameters described above define the active image area as shown in Figure 12.

Figure 12. Active Image Area Defined by Window Parameters

## Reset

A write operation to the Reset Register performs a reset operation on the L64765. (The value written is ignored). A reset operation clears the *Go* bit in the Format Register but does not otherwise affect the state of the L64765. The contents of the gamma correction tables and the configuration registers are unchanged after a reset operation.

## Initialization

When the L64765 is powered on, the contents of the internal registers is undefined. Before the device is put into operation, this initialization sequence should be performed.

- 1. Set the values of Width, Height, WDelay, and HDelay as described earlier in "Window Control Registers."

- 2. Set the values of the operating parameters in the Format Register as described earlier in "Format Register." Do not set the *Go* bit yet.

- 3. Load the gamma correction into the tables as described earlier in "Gamma Correction Tables."

- 4. Perform a reset operation as described earlier in "Reset."

- 5. Set the Go bit. The L64765 is now ready for operation.

Figure 13. Functional Waveforms

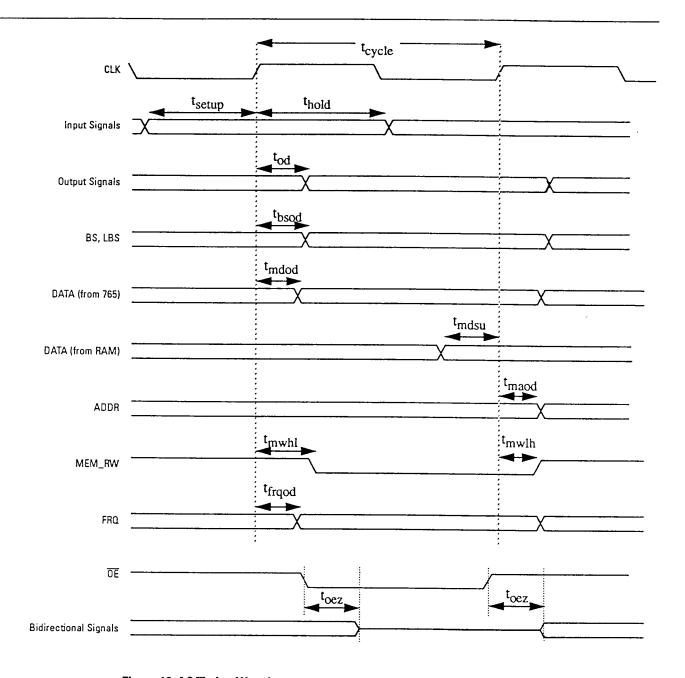

# **AC Timing**

This section presents the AC timing information for the L64765, including:

- Table 4, AC Timing Values

- Figure 16, Write Timing Waveforms

Figure 14, Read Timing Waveforms

- Figure 15, AC Timing Waveforms All parameters in Table 4 are measured for  $T_A = 0$  to 70 C,  $V_{DD} = 4.75$  to 5.25 volts.

**Table 4. AC Timing Values**

|                    |                                                     | 27  | MHz |       |

|--------------------|-----------------------------------------------------|-----|-----|-------|

| Symbol             | Parameter                                           | Min | Max | Units |

| t <sub>cycle</sub> | CLK cycle time                                      | 37  |     | ns    |

| t <sub>setup</sub> | Input signal setup                                  | 10  |     | ns    |

| t <sub>hold</sub>  | Input signal hold                                   | 6   |     | ns    |

| t <sub>bsod</sub>  | BS, LBS output delay <sup>1</sup>                   |     | 24  | ns    |

| t <sub>od</sub>    | Output delay <sup>1,3</sup>                         |     | 22  | ns    |

| t <sub>mdsu</sub>  | Memory data setup                                   | 0   |     | ns    |

| t <sub>mdod</sub>  | Memory data output delay <sup>1</sup>               |     | 20  | ns    |

| t <sub>maod</sub>  | Memory address output delay <sup>2</sup>            |     | 11  | ns    |

| t <sub>mwhi</sub>  | MEM_RW High-to-Low delay <sup>2</sup>               |     | 9   | ns    |

| t <sub>mwih</sub>  | MEM_RW Low-to-High delay <sup>2</sup>               |     | 8   | ns    |

| t <sub>frqod</sub> | FRQ output delay <sup>2</sup>                       |     | 12  | ns    |

| t <sub>rsu</sub>   | R[1:0] setup                                        | 11  |     | ns    |

| t <sub>rhid</sub>  | R[1:0] hold                                         | 11  |     | ns    |

| t <sub>cdsu</sub>  | Control data (PIX[23:16]) setup                     | 11  |     | ns    |

| t <sub>cdhid</sub> | Control data (PIX(23:16)) hold                      | 5   |     | ns    |

| t <sub>edod</sub>  | Control data (PIX[23:16]) output delay <sup>1</sup> |     | 19  | ns    |

| t <sub>oez</sub>   | Output tri-state delay from OE active               |     | 18  | ns    |

## Notes:

- Output loading = 85 pF.

- 2. Output loading = 50 pF.

- 3.  $t_{od}$  applies to output signals YCBCR[7:0], HSYNC, VSYNC, BUSY, and PIX[23:0] except when PIX[23:16] are used for control read and write operations.

Figure 14. Write Timing Waveforms

Figure 15. Read Timing Waveforms

Figure 16. AC Timing Waveforms

## **Electrical Characteristics**

This section presents the electrical characteristics of the L64745:

- Absolute Maximum Ratings

- Recommended Operating Conditions

- DC Characteristics

**Table 5. Absolute Maximum Ratings**

| Parameter           | Symbol | Limits            | Units |

|---------------------|--------|-------------------|-------|

| DC supply voltage   | VDD    | -0.3 to +7        | V     |

| Input voltage       | VIN    | -0.3 to VDD + 0.3 | V     |

| DC input current    | IIN    | ±10               | mA    |

| Storage temperature | TSTG   | -65 to +150       | *c    |

**Table 6. Recommended Operating Conditions**

| Parameter                                                   | Symbol   | Limits                  | Units |

|-------------------------------------------------------------|----------|-------------------------|-------|

| DC supply voltage<br>Operating ambient<br>Temperature range | VDD      | +3 to +6                | ٧     |

| Military<br>Commercial                                      | TA<br>TA | -55 to +125<br>0 to +70 | .c    |

**Table 7. DC Characteristics**

| Symbol | Parameter                                 | Condition <sup>1</sup> | Min  | Тур | Max | Units |

|--------|-------------------------------------------|------------------------|------|-----|-----|-------|

| VIL    | LOW input voltage                         |                        |      |     | 0.8 | V     |

| VIH    | HIGH input voltage                        |                        | İ    |     |     |       |

|        | Commercial <sup>2</sup>                   |                        | 2.0  |     |     | V     |

|        | Military <sup>2</sup>                     |                        | 2.25 |     |     | Ιv    |

| IIN    | Input current                             | VIN = VDD              | -100 | -30 | -8  | μА    |

| VOL    | LOW output voltage                        |                        | ]    |     |     | '     |

|        | Commercial                                | IOL = -4 mA            | - 1  | 0.2 | 0.4 | l v   |

|        | Military                                  | IOL = -3.2 mA          | 1    | 0.2 | 0.4 | V     |

| VOH    | HIGH output voitage                       |                        |      |     | i   |       |

|        | Commercial                                | 10H = -4 mA            | 2.4  | 2.5 |     | l v   |

|        | Military                                  | 10H = -3.2 mA          | 2.4  | 2.5 |     | l v   |

| IOS    | Output short-circuit current <sup>3</sup> | VDD = Max, VO = VDD    | 15   |     | 130 | mA    |

| DDD    | Quiescent supply current                  | VIN = VDD or VSS       | i    | ł   | 10  | mΑ    |

| 100    | Operating supply current                  |                        | :    | 200 |     | mA    |

| CIN    | Input capacitance                         | Any input              |      | 5   | l   | pF    |

| COUT   | Output capacitance                        | Any output             |      | 10  |     | pF    |

#### Notes

- 1. All DC characteristics are specified for VDD = 5 V over the specified temperature and voltage ranges.

- 2. See "Recommended Operating Conditions" for commercial and military temperature ranges.

- Not more than one output should be shorted at a time. Duration of short circuit test must not exceed one second.

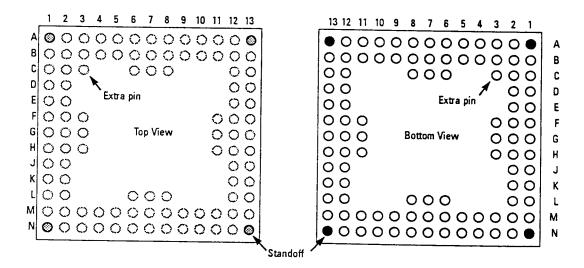

# **Packaging**

The L64745 is supplied in a 100-pin ceramic pin-grid array (CPGA). This section provides the following following information:

- Pin number to signal name correspondance

- Signal name to pin number correspondance

- Pin diagram for 100-pin CPGA package

- Mechanical dimensions

**Table 8. Signal Name to Pin Number Correspondance**

| Signal<br>Name                                                                                                                                                                          | Pin<br>No.                                                                                                       | Signal<br>Name                                                                                                            | Pin<br>No.                                                                                                                          | Signal Pi<br>Name No                                                                         |                                                                                                                       |                                                                                                                             | nal<br>me                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| ADDR.0<br>ADDR.1<br>ADDR.2<br>ADDR.3<br>ADDR.4<br>ADDR.5                                                                                                                                | J1<br>H3<br>H2<br>H1<br>G2<br>F1                                                                                 | DATA.7<br>DATA.8<br>DATA.9<br>DATA.10<br>DATA.11<br>DATA.12                                                               | M4<br>N3<br>M3<br>N2<br>M1<br>L1                                                                                                    | PIX.12<br>PIX.13<br>PIX.14<br>PIX.15<br>PIX.16<br>PIX.17                                     | B9<br>A9<br>C8<br>B8<br>A8<br>A7                                                                                      | VDD<br>VSS<br>VSS<br>VSS<br>VSS<br>VSS                                                                                      | N13<br>C1<br>C7<br>C12<br>G3<br>G11 |

| ADDR.6<br>ADDR.7<br>ADDR.8<br>ADDR.10<br>ADDR.11<br>ADDR.12<br>ADDR.13<br>ADDR.14<br>ADDR.15<br>BS<br>BUSY<br>CLK<br>DATA.0<br>DATA.1<br>DATA.2<br>DATA.3<br>DATA.4<br>DATA.5<br>DATA.6 | F2<br>F3<br>E1<br>E2<br>D1<br>D2<br>C2<br>B3<br>A2<br>A3<br>N8<br>F13<br>H13<br>M7<br>N6<br>M6<br>L6<br>N5<br>M5 | DATA.13 DATA.14 DATA.15 FRQ HSYNC LBS MEM_RW OE PIX.0 PIX.1 PIX.2 PIX.3 PIX.4 PIX.5 PIX.6 PIX.7 PIX.8 PIX.9 PIX.10 PIX.11 | K2<br>K1<br>J2<br>H12<br>G13<br>M8<br>B4<br>K12<br>F11<br>E13<br>E12<br>D13<br>D12<br>C13<br>B13<br>A12<br>B11<br>A11<br>B10<br>A10 | PIX.18 PIX.19 PIX.20 PIX.21 PIX.22 PIX.23 R.0 R.1 READ VDD VDD VDD VDD VDD VDD VDD VDD VDD V | A6<br>B6<br>C6<br>A5<br>B5<br>A4<br>J12<br>K13<br>J13<br>A1<br>A13<br>B2<br>B7<br>B12<br>G1<br>G12<br>M2<br>M13<br>N1 | VSS VSS VSS VSYNC WRITE YCBCR.0 YCBCR.1 YCBCR.2 YCBCR.3 YCBCR.4 YCBCR.5 YCBCR.6 YCBCR.7 Reserved Reserved Reserved Reserved | L12<br>N12<br>N11<br>M10            |

Notes:

1. Reserved pins must be left unconnected for normal operation.

| Table 9 . Pin Number to Signal Name Correspondance |                |     |          |     |                       |     |               |  |  |  |  |  |

|----------------------------------------------------|----------------|-----|----------|-----|-----------------------|-----|---------------|--|--|--|--|--|

| Pin<br>No.                                         | Signal<br>Name | Pin | Signal   | Pin | Signal                | Pin | Signal        |  |  |  |  |  |

| 140.                                               | Name           | No. | Name     | No. | Name                  | No. | Name          |  |  |  |  |  |

| A1                                                 | VDD            | C1  | VSS      | G12 | VDD                   | M4  | DATA.7        |  |  |  |  |  |

| A2                                                 | ADDR.14        | C2  | ADDR.12  | G13 | HSYNC                 | M5  | DATA.5        |  |  |  |  |  |

| A3                                                 | ADDR.15        | C3  | Reserved | H1  | ADDR.3                | M6  | DATA.2        |  |  |  |  |  |

| A4                                                 | PIX.23         | C6  | PIX.20   | H2  | ADDR.2                | M7  | DATA.0        |  |  |  |  |  |

| A5                                                 | PIX.21         | C7  | VSS      | H3  | ADDR.1                | M8  | LBS           |  |  |  |  |  |

| A6                                                 | PIX.18         | C8  | PIX.14   | H11 | WRITE                 | M9  | YCBCR.6       |  |  |  |  |  |

| A7                                                 | PIX.17         | C12 | VSS      | H12 | FRQ                   | M10 | YCBCR.4       |  |  |  |  |  |

| A8                                                 | PIX.16         | C13 | PIX.5    | H13 | CLK                   | M11 | VSS           |  |  |  |  |  |

| A9                                                 | PIX.13         | D1  | ADDR.10  | J1  | ADDR.0                | M12 | Reservedi     |  |  |  |  |  |

| A10                                                | PIX.11         | D2  | ADDR.11  | J2  | DATA.15               | M13 | VDD           |  |  |  |  |  |

| A11                                                | PIX.9          | D12 | PIX.4    | J12 | R.0                   | N1  | VDD           |  |  |  |  |  |

| A12                                                | PIX.7          | D13 | PIX.3    | J13 | READ                  | N2  | DATA.10       |  |  |  |  |  |

| A13                                                | VDD ,          | E1  | ADDR.8   | K1  | DATA.14               | N3  | DATA.8        |  |  |  |  |  |

| B1                                                 | Reserved       | E2  | ADDR.9   | K2  | DATA.13               | N4  | DATA.6        |  |  |  |  |  |

| B2                                                 | VDD            | E12 | PIX.2    | K12 | <u>oe</u>             | N5  | DATA.4        |  |  |  |  |  |

| B3                                                 | ADDR.13        | E13 | PIX.1    | K13 | R.1                   | N6  | DATA.1        |  |  |  |  |  |

| B4                                                 | MEM_RW         | F1  | ADDR.5   | L1  | DATA.12               | N7  | VDD           |  |  |  |  |  |

| B5                                                 | PIX.22         | F2  | ADDR.6   | L2  | VSS                   | N8  | BS            |  |  |  |  |  |

| B6                                                 | PIX.19         | F3  | ADDR.7   | L6  | DATA.3                | N9  | YCBCR.7       |  |  |  |  |  |

| B7                                                 | VDD            | F11 | PIX.0    | L7  | VSS                   | N10 | YCBCR.5       |  |  |  |  |  |

| B8                                                 | PIX.15         | F12 | VSYNC    | L8  | Reserved <sup>1</sup> | N11 | YCBCR.3       |  |  |  |  |  |

| B9                                                 | PIX.12         | F13 | BUSY     | L12 | YCBCR.1               | N12 | YCBCR.2       |  |  |  |  |  |

| B10                                                | PIX.10         | G1  | VDD      | L13 | YCBCR.0               | N13 | VDD           |  |  |  |  |  |

| B11                                                | PIX.8          | G2  | ADDR.4   | MI  | DATA.11               |     | · <del></del> |  |  |  |  |  |

| B12                                                | VDD            | G3  | VSS      | M2  | VDD                   |     |               |  |  |  |  |  |

| B13                                                | PIX.6          | G11 | VSS      | M3  | DATA.9                |     |               |  |  |  |  |  |

Notes:

1.Reserved pins must be left unconnected for normal operation.

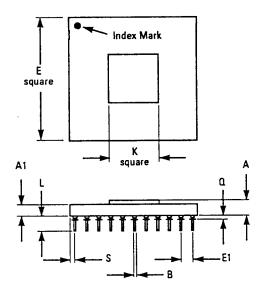

Figure 17. 100-Pin CPGA Pin Layout

| Dimension |     | 100-pin CPGA  |

|-----------|-----|---------------|

| A         | Max | 0.117 (2.972) |

| A1        | Ref | 0.080 (2.032) |

| В         | Min | 0.016 (0.406) |

|           | Max | 0.020 (0.508) |

| E         | Min | 1.308 (33.22) |

|           | Max | 1.332 (33.83) |

| E1        | Min | 0.095 (2.413) |

|           | Max | 0.105 (2.667) |

| L         | Min | 0.170 (4.318) |

|           | Max | 0.190 (4.826) |

| a         | Ref | 0.050 (1.270) |

| S         | Ref | 0.060 (1.524) |

| K         | Ref | 0.673 (17.09) |

Figure 18. 100-Pin CPGA Mechanical Dimensions

## **Ordering Information**

To order products or for more information, contact any LSI Logic sales office shown on the back cover.

## L64765 Ordering

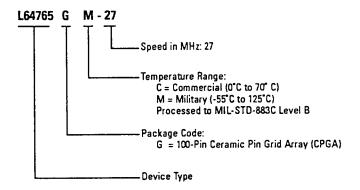

Figure 19 shows an example of a valid part number for ordering the L64765 and the codes for other options. The part number shown, L64765G M-27, designates an L64765 in a 100-pin ceramic pin-grid array (CPGA) rated for the military temperature range and a maximum clock speed of 27MHz.

Figure 19. L64765 Part Number Designation

# Trademark Information

The LSI Logic logo design is a registered trademark of LSI Logic Corporation.