# STE12PS

# 12 channel integrated PSE line manager

Preliminary Data

## Features

- PSE power control device

- Supports up to 12 independent or four 30W, "boosted" ports

- Wide operating range: up to 90V

- IEEE 802.3af compliant

- Open circuit detection: AC and DC methods

- Advanced power management algorithm

- Current sensing with as low as 500mΩ, external, series resistors

- No need for external FETs

- In-rush current control

- Short-circuit protection

- Adaptable signature detection capability

- On-chip 3.3V SMPS controller

- Low-noise, 12-bit ADC

- Standard I<sup>2</sup>C interface

- Parallel monitor interface

#### Description

STE12PS is designed to supply power over multiple Ethernet channels in order to avoid different, individual power supply units for applications such as Web cams, IP Phones, Bluetooth access points and WLAN access points.

The equipment that provides the power to the twisted pair cabling is referred to as Power Sourcing Equipment (PSE).

The PSE's main functions are: looking for links to a Powered Device (PD), classifying a PD, supplying power to the link, monitoring power on the link, and removing power from the link.

The STE12PS is fully programmable, supporting the detection and powering of IEEE802.3af as well as legacy PDs. The flexibility of the STE12PS allows the user to select a suitable system configuration: up to 12 ports as well as 4 "boosted" channels. If needed, the STE12PS can also efficiently manage cases or applications where a limited amount of power is available to the ports (smart-power capability) by means of integrated, power MOSFET devices. All operations are controlled via the I<sup>2</sup>C bus also notifying externally some ports status condition via dedicated pins.

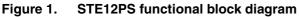

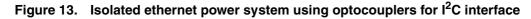

Ethernet port isolation can be easily maintained thanks to an integrated 3.3V SMPS power source and by means of optocouplers.

The STE12PS has five address selection inputs to choose up to 32 possible different addresses.

Power can be provided to the PD using either spare lines of the Ethernet cable or using the data wires, as specified by IEEE 802.3af.

November 2006

www.st.com

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

# Contents

| 1 | Block  | diagram                                       |

|---|--------|-----------------------------------------------|

| 2 | Pin de | escription                                    |

| 3 | Funct  | ional description9                            |

|   | 3.1    | Operating modes                               |

|   | 3.2    | Detection and classification 10               |

|   |        | 3.2.1 Detection                               |

|   |        | 3.2.2 Classification                          |

|   |        | 3.2.3 Detection and classification FSM        |

|   | 3.3    | Power ON                                      |

|   |        | 3.3.1 Under load (disconnection)14            |

|   |        | 3.3.2 Short circuit, overload and overcurrent |

|   |        | 3.3.3 Thermal monitoring                      |

|   | 3.4    | Internal 3.3V/10V generator                   |

|   | 3.5    | Logic interface                               |

|   | 3.6    | 6MHz clock generator 21                       |

|   | 3.7    | Smart-power mode 21                           |

|   | 3.8    | Power boost mode - 30W 22                     |

|   | 3.9    | Measurement and parameter codings 25          |

| 4 | I2C in | terface                                       |

| 5 | I2C sl | ave protocol overview                         |

|   | 5.1    | Functional description 27                     |

|   | 5.2    | Error cases                                   |

|   | 5.3    | Interrupts                                    |

|   | 5.4    | I2C device address                            |

|   | 5.5    | Register addressing: write command format     |

|   | 5.6    | Register addressing: read command format      |

|   | 5.7    | Parallel monitoring interface                 |

| 6 | Electr | ical specifications and timings               |

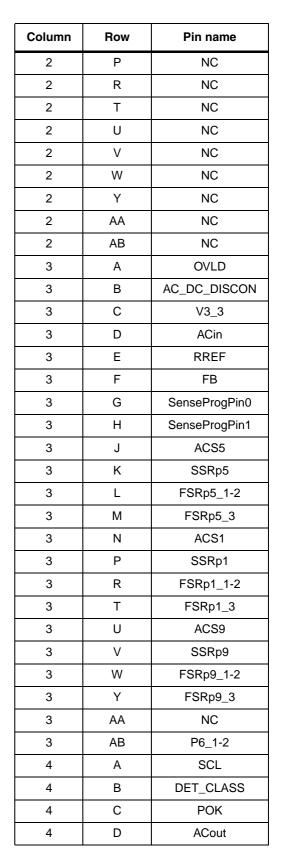

| 7  | Ball coordinates                      | 35 |

|----|---------------------------------------|----|

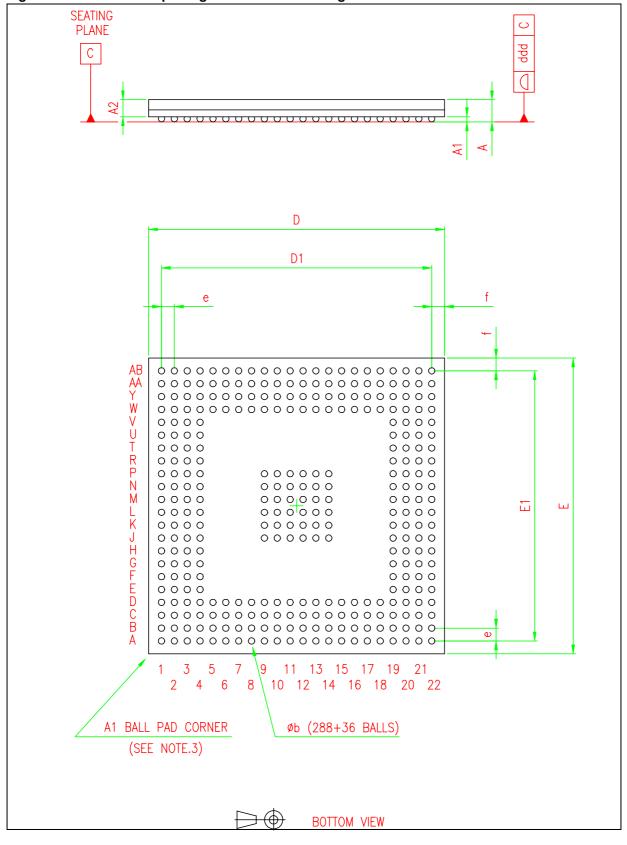

| 8  | Package information - mechanical data | 11 |

| 9  | Ordering information                  | 13 |

| 10 | Revision history                      | 13 |

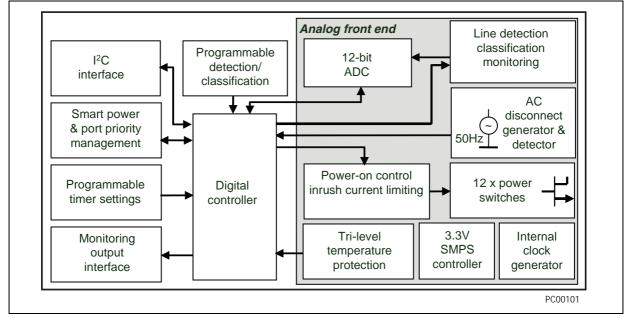

# 1 Block diagram

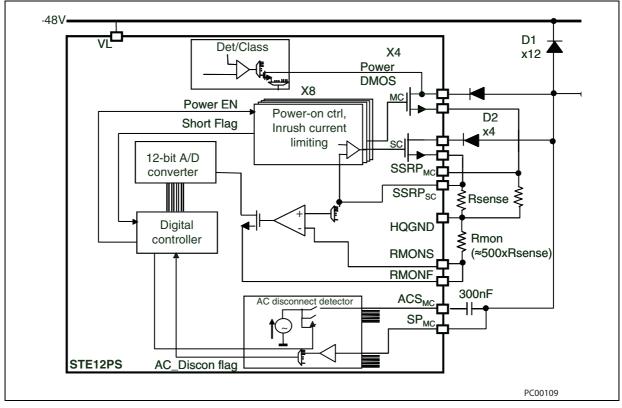

#### Figure 2. Typical application diagram

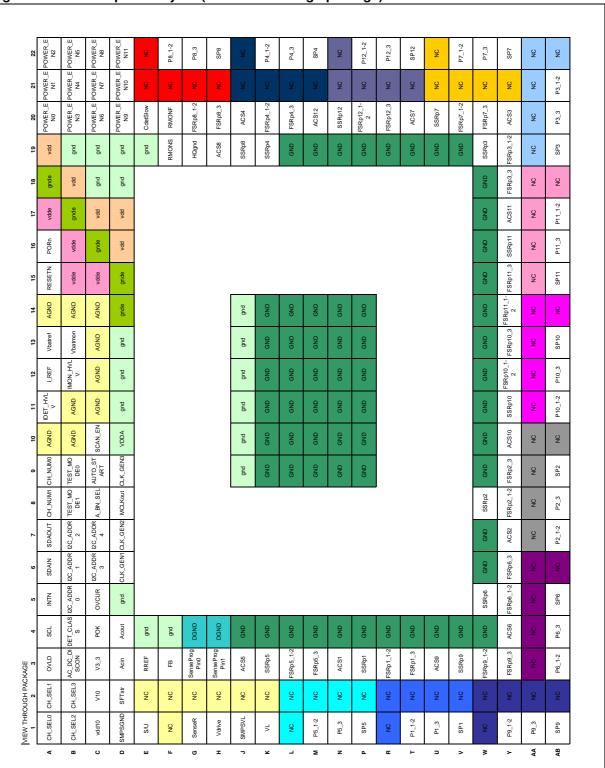

# 2 Pin description

| Pin name  | I/O | Function                                                                                                                                                              |  |

|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IDET_HVLV | 0   | Anti-aliasing filter capacitor to be connected between the analog input and ground to improve ADC noise performance. $C = 180 \text{ pF}$ .                           |  |

| IMON_HVLV | 0   | Anti-aliasing filter capacitor to be connected between the analog input and ground. $C = 180 pF$ .                                                                    |  |

| Vbat_mon  | 0   | Anti-aliasing filter capacitor to be connected between the analog input and ground. $C = 100$ nF.                                                                     |  |

| Vbatref   | 0   | Anti-aliasing filter capacitor to be connected between the analog input and ground. $C = 100$ nF.                                                                     |  |

| I_REF     | 0   | Anti-aliasing filter capacitor to be connected between the analog input and ground. $C = 180 pF$ .                                                                    |  |

| CDETSLOW  | 0   | Detection rise/fall time capacitor (up to 25nF). Tr/f can be set from 1 ns to 4 ms.                                                                                   |  |

| RSENSE    | 0   | SMPS precision, external, current limiting reference resistor: $100m\Omega$                                                                                           |  |

| VDRIVE    | 0   | External p-channel MOSFET gate driving voltage for SMPS. It provides a square wave with VL as upper limit and (VL-10V) as lower limit voltage.                        |  |

| SFTSTR    | 0   | Switched Mode Power Supply (SMPS) soft start capacitor, 200nF.                                                                                                        |  |

| FB        | IO  | SMPS feedback pin, Cfb = 2.2nF                                                                                                                                        |  |

| Pn        | 0   | Power DMOS device drain, if DMOS is turned-on, channel "n" where n = 1,12 is activated.                                                                               |  |

| ACSn      | 0   | It provides a 50Hz AC disconnection signal for port "n", $n = 1, 12$ .                                                                                                |  |

| SPn       | I   | Detection classification and AC disconnection sensing port "n", n = 1, 12.                                                                                            |  |

| SSRPn     | I   | Line current to the monitoring resistor for channel "n", $n = 1,$ 12. Allowed values are 0.523, 1.05, 1.58 and 2.1 ohms (see also SENSPROG preset pins). Sensing pin. |  |

| FSRPn     | 0   | Source terminal for power DMOS connected to the sense resistor for channel "n", $n = 1,, 12$ , a "forcing" pin.                                                       |  |

| RMONF     | 0   | Mirror monitoring resistance (500 $\times$ $R_{sense})$ pin to let internal ADC evaluate line currents. Forcing pin.                                                  |  |

| RMONS     | 0   | Mirror monitoring resistance (500 $\times$ R <sub>sense</sub> ) pin to let internal ADC evaluate line currents. A "sensing" pin.                                      |  |

| RREF      | I   | Reference bias resistor: 18.7kΩ                                                                                                                                       |  |

| CLK_GEN1  | I   | Crystal oscillator pin1 for high performance clock generation.                                                                                                        |  |

| CLK_GEN2  | I   | Crystal oscillator pin2 for high performance clock generation.                                                                                                        |  |

| MCLK      | 0   | Master clock output for multi device configuration.                                                                                                                   |  |

| CLK_GEN3  | I   | Low profile clock input pin or clock input pin in multi-device configuration.                                                                                         |  |

| ACin      | I   | 50Hz sinusoidal input                                                                                                                                                 |  |

| ACout     | 0   | 50Hz sinusoidal output, internally generated                                                                                                                          |  |

|           |     |                                                                                                                                                                       |  |

\_\_\_\_\_

#### Table 1.Analog pins description

| Pin name            | I/O | Function                                                                                                                                                                                                                                                                                       |  |

|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset               |     |                                                                                                                                                                                                                                                                                                |  |

| RESETN              | I   | Reset pin. Active LOW                                                                                                                                                                                                                                                                          |  |

| Status flag interfa | ce  |                                                                                                                                                                                                                                                                                                |  |

| CH_SELn             | Ο   | Channel identification "n", where n = 1, 12. Indicates the channel whose status flags (POK,) are currently notified externally. CH_SEL is incremente every 60 * MCLK clock cycles. The status flag notification is enabled via the configuration register Global_cfg2, STATUS_FLAG_EN bit.     |  |

| РОК                 | 0   | Power OK flag. This flag indicates condition of the currently powered channel:<br>'1'                                                                                                                                                                                                          |  |

| OVLD                | 0   | Overload Alarm Flag for the currently powered channel. Current overload condition (Icut is over threshold):<br>'1'                                                                                                                                                                             |  |

| OVCUR               | 0   | Short circuit Alarm Flag for the currently powered channel. Current limiting condition:<br>'1'→Overcurrent or detection failed condition detected<br>'0'→ANY Short Circuit condition detected                                                                                                  |  |

| AC_DC_DISCON        | 0   | AC/DC Disconnection Alarm Flag for the currently powered channel:<br>'1'—AC/DC disconnection detected<br>'0'—ANY disconnection detected                                                                                                                                                        |  |

| DET_CLASS           | 0   | Detection/Classification flag.<br>'1'-Detection or Classification procedure is running<br>'0'-Detection/Classification procedure is not running.                                                                                                                                               |  |

| Por_N               | 0   | '1' →VL, 10V and 3.3V supply Power ON succeeded                                                                                                                                                                                                                                                |  |

| Thermal monitoring  | Ig  |                                                                                                                                                                                                                                                                                                |  |

| T_MONITOR <i>x</i>  | 0   | Thermal monitoring (x = 0,1).<br>These bits encode the internal temperature's threshold measured in the<br>following way:<br>"00" →Temperature under 110°C<br>"01" →Temperature between the 110°C to 130°C<br>"11" →Temperature between the 130°C to 150°C<br>"10" →Temperature is above 150°C |  |

#### Table 2.Digital pins description

| able 2.     Digital pins description (continued)       Pin name     I/O   Function |            |                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                    |            | Function                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Configuration sign                                                                 | nals       |                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| A_BN_SEL                                                                           | I          | A or B alternative configuration mode select.<br>'0'→Alternative B (Midspan-PSE)<br>'1'→Alternative A (Endpoint-PSE)                                                                                                                                                                                                                                                                                           |  |  |

| CH_NUMx                                                                            | I          | 12- or 4-boost channel select. x = 0,1.<br>'00' →12 channels configuration<br>'01' →NA<br>'10' →NA<br>'11' → 4-boost channel configuration                                                                                                                                                                                                                                                                     |  |  |

| AUTO_START                                                                         | I          | AUTO Start Mode enable.<br>'0'→Auto Start Mode disabled: all the ports are disabled after Reset, Neither<br>detection nor power on is performed (MODE[1:0] register selected to Power<br>Down at the reset event)<br>'1'→Auto Start Mode enabled: all the ports are automatically enabled,<br>detection, classification and power are performed (MODE[1:0] register selected<br>to AUTO after the reset event) |  |  |

| S/UPIN                                                                             | I          | SMPS (Switch Mode Power Supply) mode selector bit (supplier / User). When Not connected the device works as DC-DC converter controller.                                                                                                                                                                                                                                                                        |  |  |

| SENSEPROGx                                                                         | I          | Preset pins for sensing resistor programmability (x=0,1). The programmed value must match the mounted $R_{sense}$ resistors.<br>'00' $\rightarrow R_{sense} = 0.5\Omega$<br>'01' $\rightarrow R_{sense} = 1\Omega$<br>'10' $\rightarrow R_{sense} = 1.5\Omega$<br>'11' $\rightarrow R_{sense} = 2\Omega$                                                                                                       |  |  |

| Power ON control                                                                   | er signals |                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| POWER_EN <i>x</i>                                                                  | Ι          | Reserved. (x = 0,11).                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| I <sup>2</sup> C Signals                                                           |            |                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| I2C_ADDRx                                                                          | I          | This defines the device address for the $I^2C$ interface. $x = 0, 4$ .                                                                                                                                                                                                                                                                                                                                         |  |  |

| SCLIN                                                                              | I          | Serial clock input pin for the I <sup>2</sup> C interface.                                                                                                                                                                                                                                                                                                                                                     |  |  |

| SDAIN                                                                              | I          | Serial data input pin for the I <sup>2</sup> C interface. When "jumpered" with the SDAOUT pin, this connection becomes the standard bi-directional serial data line (SDA).                                                                                                                                                                                                                                     |  |  |

| SDAOUT                                                                             | 0          | Serial data output pin for the $I^2C$ interface. When jumpered with the SDAIN pin, this connection becomes the standard bi-directional serial data line (SDA).                                                                                                                                                                                                                                                 |  |  |

| INTN                                                                               | 0          | I <sup>2</sup> C Open drain output that goes low when interrupt event is notified                                                                                                                                                                                                                                                                                                                              |  |  |

| Test mode signals                                                                  | ;          |                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| TEST_MODEx                                                                         | I          | Test Mode Enable (x = 0,1).<br>'00' →Functional mode<br>'01' →Reserved<br>'10' →Reserved<br>'11' →Reserved                                                                                                                                                                                                                                                                                                     |  |  |

| SCAN_EN                                                                            | I          | Reserved. Preset to '0'.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Table 2. | Digital pine  | s description | (continued) |

|----------|---------------|---------------|-------------|

|          | Digital pills | s uescription | (continueu) |

| Pin name        | I/O | Function                                                                        |

|-----------------|-----|---------------------------------------------------------------------------------|

| GND, AGND       | I   | Analog grounds                                                                  |

| SMPSGND         | Ι   | SMPS power ground                                                               |

| SMPS_VL         | Ι   | +48V battery voltage for SMPS                                                   |

| V3_3,Vdd,Vdde   | Ι   | 3.3V supply                                                                     |

| V10, Vdd10      | I/O | 10V supply to power-up the output DMOS and minimize its ON resistance           |

| HQGND           | Ι   | Dedicated ground for Kelvin line current sense resistor (a high quality ground) |

| DGND, gnd, gnde | Ι   | Digital grounds                                                                 |

| VL              | Ι   | +48V battery voltage.                                                           |

### Table 3. Power and ground pins description

# **3** Functional description

The STE12PS architecture provides a complete PSE interface and smart digital controller to efficiently manage the functions in a PoE system. All operations can be controlled through R/W registers via a standard  $I^2C$  bus interface.

The STE12PS is designed to control power delivery of up to 12 separate lines. This is performed by controlling 12 integrated, power MOS transistors connected to the low side of the line - monitoring the line voltage and sensing line current by means of external, series sensing resistors (one per port). Turning on a port means to switch the relative MOS transistor thus controlling the inrush current in order to rise the port voltage up to 48V (typical battery voltage) after a valid PD signature has been detected. The flexibility of the STE12PS allows the user to select a suitable system configuration: 12 "standard" 15W or 4 "boosted" 30W channels, by means of pins CH\_NUMn. Also, one can select the type of architecture (Endpoint PSE/ Alternative A or Midspan PSE/Alternative B) for all channels via pin A\_BN\_SEL.

Some typical applications for the STE12PS include:

- Ethernet switches/routers

- Midspan power supplies

- IP-PBX

- WLAN access points

## 3.1 Operating modes

The digital controller can operate in one of five possible modes for all the channels, selectable through the Global Configuration registers: Stand-by, Auto, Semi Auto, Manual or Power Down.

When the reset condition is removed, the controller defaults to Power Down mode if the AUTO\_START pin is tied low; if AUTO\_START is tied HIGH the mode is configured in AUTO. The mode can be changed only during a limited amount of time (100ms), after the reset is released, accessing the Global Configuration registers before the detection procedure is started, or placing the device in STAND-BY mode via the I<sup>2</sup>C interface.

The characteristics of the Five possible operating modes are described below:

- STAND-BY: the controller allows only the read write operations suitable for changing programmability. To enable this mode set the reset bit 1 of the REG0x05.

- AUTO: the controller autonomously performs detection, classification and Power ON command without the need of host commands. A subset of status flags stored in the channels monitor registers is reported externally through the Status Flag Notifies pins allowing operation without the presence of the host controller.

- SEMIAUTO: after a triggering command the controller autonomously performs detection and classification waiting a dedicated command from host processor for the power on. Based on the detection and classification results reported in the Channels Status registers, the host controller can decide to power on the selected channel. The disconnection of a channel is automatic as in the AUTO mode, unless disabled.

- MANUAL: any action is performed manually. The host controller has the responsibility to force any state transition in the FSM. Then based on the measures performed automatically by the ADC on several parameters, the host controller can decide to

classify the channel and afterwards to issue the power on command. The STE12PS controller can also automatically disconnect a channel in fault condition (if not enabled, the STE12PS will notify automatically only a short circuit condition or an AC disconnection event. Overload or DC disconnection is responsibility of the host controller.) The host controller can also power on a channel skipping detection and/or classification procedures.

• POWER DOWN: the controller is put in power down state. No actions are performed until the power down mode is removed.

For all operating modes, except power-down and stand-by, the power ON/OFF condition of each channel can also be managed, directly, by the host processor or controller via a dedicated command.

Moreover, the power removal procedure is performed automatically (also in MANUAL mode) when a fault event has been detected (AC/DC disconnection, overload or overcurrent); this behavior can be changed configuring appropriately some dedicated enable/disable bits of channels event registers.

With Priority Management in AUTO mode and Smart-power management enabled, it is also possible to set different priorities for different channels. The STE12PS will probe channels starting from those with the highest priority. In case of a shortage of available power, it is also possible to disable powering of newly detected, lower priority ports until the highest detected ones are served.

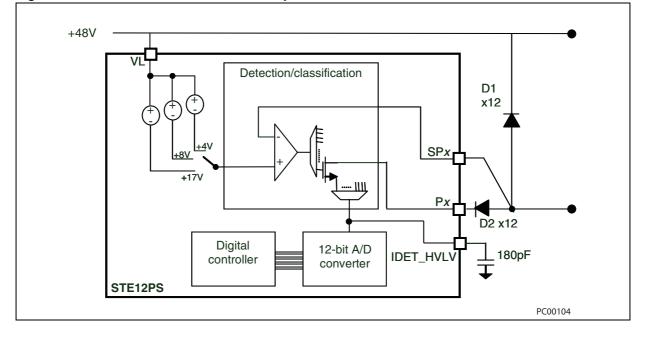

## 3.2 Detection and classification

#### 3.2.1 Detection

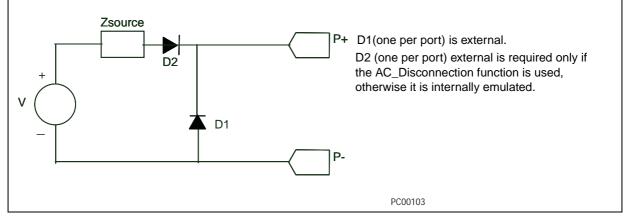

The STE12PS looks for, in turn on the free available ports (according to the priority list if enabled), for a valid PD signature ( $25k\Omega$  slope characteristic) by driving two different voltage levels at the port (4V and 8V), and calculating the slope resistance/ conductance by monitoring the current difference. The equivalent circuit for the IEEE802.3af detection phase is shown in *Figure 3* below.

Figure 3. IEEE802.3af detection circuit

As detection is performed by multiplexing a common voltage generator. If more than one port is connected to several PDs, an extra delay in the detection start will be introduced. See *Table 10: Electrical characteristics*, parameter Tdetd.

By default, the STE12PS will recognize a valid signature with the following characteristics:

- an inverse slope of the port current vs. voltage (I-V) characteristic measuring between 19 and 26.5 kΩ (Rdl and Rdh),

- a port capacitance of less than 4µF.

If required, the STE12PS can also perform a custom, resistive detection search – modifying the acceptance window. This can be easily performed by changing the Rdh and Rdl limits or by changing Gdl and Gdh via the logic interface.

In Midspan applications, where power is applied via spare wires, when the PSE fails to detect a PD, the port remains in high-impedance (Hi-Z) for at least two seconds. If the signature resistance is greater than  $500 k\Omega$ , then the two second wait is avoided.

Transition rates of the port voltage between the two probing levels can be adjusted with capacitance Cdetslow.

| Class | Usage    | Maximum power level at<br>PSE output (Pall) | Power level at PD input | I <sub>class</sub>                   |

|-------|----------|---------------------------------------------|-------------------------|--------------------------------------|

| 0     | Default  | 15.4W (programmable)                        | 0.44 to 12.95W          | I <sub>class</sub> < Ithcl0          |

| 1     | Optional | 4W (programmable)                           | 0.44 to 3.84W           | Ithcl0 < I <sub>class</sub> < Ithcl1 |

| 2     | Optional | 7W (programmable)                           | 3.84 to 6.49W           | Ithcl1< I <sub>class</sub> < Ithcl2  |

| 3     | Optional | 15.4W (programmable)                        | 6.49 to 12.95W          | Ithcl2 < I <sub>class</sub> < Ithcl3 |

| 4     | Optional | -                                           | Reserved                | Ithcl3 < I <sub>class</sub> < Ithcl4 |

| 0     | Default  | 15.4W (programmable)                        | 0.44 to 12.95W          | Ithcl4 < I <sub>class</sub>          |

Table 4.PD power classification

#### 3.2.2 Classification

Once a valid signature is detected, the port is probed for classification in order to perform smart-power management (if enabled).

Port probing is performed by forcing a DC voltage in the range of 16V to 18V (one DC generator multiplexed between the channels) and monitoring current  $I_{class}$ . The measurement is repeated and stored in the Channel Monitor Classification registers to ensure a coherent classification. The PD power class is defined as shown in *Table 4* above.

The detected class is then stored in the Channel Status registers.

Note: The power absorbed in a link is calculated considering the actual value of the battery voltage in order to arrive at a true power measurement result.

### 3.2.3 Detection and classification FSM

This FSM manages all operations related to the detection and classification procedures.

For these two procedures, the following assumptions are made:

- 1. A channel is detected ONLY if:

- a) the channel has not yet been detected, *and* Channel Detection has been enabled, *and*

- b) the Backoff Detection timer *and* Subsequent Attempt timer are NOT running (after a corresponding fault detection or failed signature).

- 2. A channel is classified ONLY if:

- a) Channel Classification is enabled, and

- b) the previous related detection procedure has reported an Rgood/Ggood value (Auto and SemiAuto modes).

Three general macro operations can be performed:

- STARTUP: the following operations are related to the startup procedure:

- RESET: reset and initialize all digital aspects of the STE12PS,

- WAIT\_POWER\_UP: wait 100ms for completion of the power-up procedure. During this period, the I<sup>2</sup>C bus is active - allowing the host to initialize registers while the detection procedure is waiting to start.

- DETECTION START: all setting-up needed to start operations is performed in this state. The first battery voltage sample is latched in a dedicated register.

- DETECTION: the following operations are related to the detection procedure for the channel selected:

- Low Voltage detection command (4V) is issued via registers; detection timer is started to execute the command for a duration of ½Tdet ms.

- Wait for 5ms to acquire a stable measurement.

- Sampled sensing current values are acquired via A/D converter.

- The samples previously acquired are averaged and the resulting value, reported into the Channels Monitor register, is compared against programmed min/max values. If the sensing current is higher than maximum allowed value, the detection procedure is considered as having FAILED: backoff timer is started (Alternative B) and an alarm flag raised according to the Channel Status registers.

- If the sensing current results lower than the minimum allowed value the detection procedure is continued: the alarm flag is raised in the Channel Status registers.

- The described operations are repeated for the High-Voltage detection command (8 V).

- Signature Resistance is calculated:

- If 2µsec < Gmeas < Glow *or* Ghigh < Gmeas, then backoff timer is started (Alternative B) and detection result failure is reported in the Channel Status registers.

- Else, Glow < Gmeas < Ghigh and the result of a successful detection is reported in the Channel Status registers.

- CLASSIFICATION: The following operations are related to the classification procedure for the corresponding channel

- If classification is not enabled, the default Class 0 is assigned.

- High Voltage detection command (17V) is issued via registers; detection timer is started to execute the command for 15ms duration.

- Wait for 5ms to acquire a stable measurement

- Sampled sensing current values are acquired via A/D converter.

- Average the previously acquired samples and report the resulting value in a dedicated register. The power class is identified and the result is reported in the Channel Status registers.

- Channel is ready to be powered: if the smart-power algorithm is enabled (via the MISCELLANEOUS registers) the channel is powered only if the required power is within the remaining power budget; the channel can be powered regardless of the power-check availability via registers.

If the power availability check has a positive result (or it hasn't been performed), the channel is powered. Otherwise, it is rejected, and the alarm flag raised in the Channel Events register. The channel number is registered into a scheduler FIFO so that power will again be available when the channel is ready to be switched-on.

#### Figure 4. Detection and classification equivalent architecture

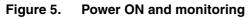

### 3.3 Power ON

After the classification phase the port will be powered.

Once activated, the power-on sequencer manages the channel's activation requests received through the signature detection circuitry. For the incoming channel, activation requests are stored in the power-on sequencer and then serviced, one at a time, only when the previously activated channel leaves the current limiting condition that normally occurs during power on due to the capacitive part of the load. (see also smart-power mode and special issues)

A port is turned-on by ramping-up the voltage and increasing the current limit to its upper limit. After a programmable time ( $T_{inrush}$ ), if the port has reached full voltage and is out of current limitation, it is marked as powered. The related port power bit and the power class bits are set according to the class in the logic interface bit stream.

The active ports are continuously monitored in order to detect a fault condition such as Short Circuit, Disconnection or Excess Power (overload).

#### 3.3.1 Under load (disconnection)

Detection of a disconnection, if enabled (default condition), can be performed via a DC and/or AC method - default is DC  $\oplus$  AC (logical OR):

DC method

If this method is selected via the logic interface and if the port current drops under 7.5mA for more than 10ms, then the STE12PS will detect a DC disconnection. If this condition persist for Tmpdo (*Table 10*), then power is removed and the port is marked as free, enabling a new detection.

AC method

If this method is selected via the logic interface, the STE12PS probes the channels via coupling capacitors and detects when the AC load impedance,  $Z_{ac}$ , exceeds the maximum,  $100k\Omega$  limit for a time longer than 20ms. In this case, the PSE will detect an AC disconnection. If this condition persist for a time Tmpdo (*Table 10*), power is removed and the port is marked as free, enabling a new detection.

Disconnection modes are as following: Disabled, DC method only, AC method only, both AC and DC (combined in OR  $\oplus$  logic or in AND  $\otimes$  logic).

#### 3.3.2 Short circuit, overload and overcurrent

A short circuit is defined when port current reaches 425mA, typ. Moreover, if port voltage drops below 25V, then maximum loop current is decreased, linearly, to limit power dissipation. A short condition is considered as a fault after a period of 65ms, typ. (see *Table 10: Electrical characteristics*, parameter Tshort).

When the above conditions are met, the port is disconnected, and the fault bit set HIGH in the Channel Event registers.

Overload or excess power is defined when port power consumption reaches 15.4W for longer than 65ms, typ. (see *Table 10: Electrical characteristics*, parameter Tovld).

If smart-power management is active, then the overload power limit is set instead - according to the power class.

When the above conditions are met, the port is disconnected, and the fault bit is set HIGH.

#### Monitor overload FSM

This FSM manages all operations related to monitoring an overload event.

All operations described below are related to channels currently powered.

- STARTUP: the following operations are related to a startup procedure:

- START: channel to be monitored is selected.

- POWER MEASUREMENT: the following operations are related to a power measurement procedure

- SAMPLE Imeas: the current measurement is sampled and the next powered channel is prepared for the next monitor procedure.

- MEASURE Power: the power is measured and its value is compared against the required Power class.

- START MONITOR OVERLOAD: if the measured power exceeds the required power class the T<sub>ovld</sub> timer and the averaging process are started.

- COUNTER RESET: T<sub>ovld</sub> timer is reset if the measured power doesn't exceed the required

- POWER REMOVAL: the following operations are related to a power removal procedure:

- COUNTER CHECK: all T<sub>ovld</sub> timers are checked, and those that have expired are identified.

- POWER REMOVAL: all the channels whose timers have expired and whose average power exceeds the maximum are switched OFF through the POWER\_EN(n) pins.

- ALARM SET: for all the channels whose timers have expired, a corresponding alarm flag is raised in the Channel Event registers, and the related Ted timer is started.

#### Monitor overcurrent FSM

This particular FSM manages all operations related to procedures that are able to monitor an overcurrent event.

All operations described below are related to channels currently powered.

- STARTUP:

- START: the channel to be monitored is selected.

- VOLTAGE BATTERY:

- SAMPLE V<sub>bat</sub>: every 12 channels cycle the V<sub>bat</sub> measurement is executed.

- OVERCURRENT CHECK: the following operations are related to an overcurrent check

- I<sub>meas</sub> CHECK: if I<sub>meas</sub>>I<sub>lim</sub> the I\_LIM\_FLAG is raised and the next powered channel is prepared for the next monitor procedure.

- START MONITOR: the T<sub>lim</sub> counter is started if I\_LIM\_FLAG is found asserted.

- COUNTER RESET: if I\_LIM\_FLAG is found de-asserted T<sub>lim</sub> counter is reset taking into account that glitches of duration less than 10ms are filtered.

- POWER REMOVAL: the following operations are related to a power removal operation:

- COUNTER CHECK: all the T<sub>lim</sub> timers are checked and those expired are identified.

- POWER REMOVAL: all the channels whose timer is expired are switched OFF.

- ALARM SET: for all the channels whose timers are expired a corresponding alarm flag is raised in the FAULT\_EVENT\_CHn register and the related Ted timer is started.

#### 3.3.3 Thermal monitoring

The procedures performed by the digital controller are impacted by the thermal monitoring data indicating the measured temperature.

Its behavior is based on a three-level control system:

- 1. When the chip's internal temperature reaches 110°C, only the channels already powered will be serviced. Possible new ones, will be rejected, redetected and eventually processed when the internal temperature cools down to 100°C. This behavior can be disabled setting the proper bit register.

- 2. A second temperature threshold is set at 130°C. When this value is reached, the channels that are in current limiting or inrush condition are immediately switched OFF, and their reactivation, subject to positive redetection, will only be possible when the chip's internal temperature has cooled down to 100°C. This behavior can be disabled by setting the proper bit register.

- 3. The third temperature threshold is set at 150 °C. When this temperature is reached, all activated channels will be immediately switched OFF, and their reactivation, subject to positive redetection, will only be possible when the chip's internal temperature has decreased to 100 °C. This behavior cannot be disabled.

## 3.4 Internal 3.3V/10V generator

The STE12PS can be configured either as 3.3V and 10V generator or load by means of the S/U control input. In this manner, the need for extra, low-voltage batteries is avoided, greatly simplifying the system design. If S/U is left open, the device will operate as an SMPS controller. With the SMPS configured at 3.3V, the device can be used to power up a "1 Amp" load with high efficiency voltage conversion.

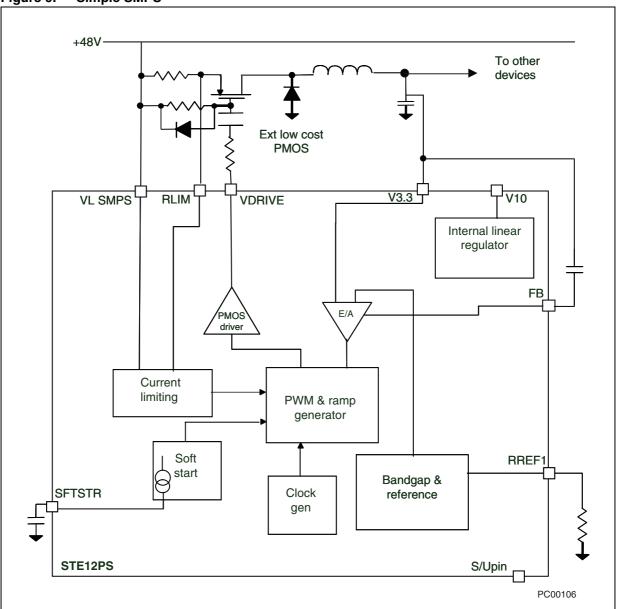

*Figure 6 on page 19* shows a typical DC-DC, buck converter configuration for the 3.3V supply. The 10V supply is generated by means of an internal, linear regulator. The 3.3V supply can source up to 1A.

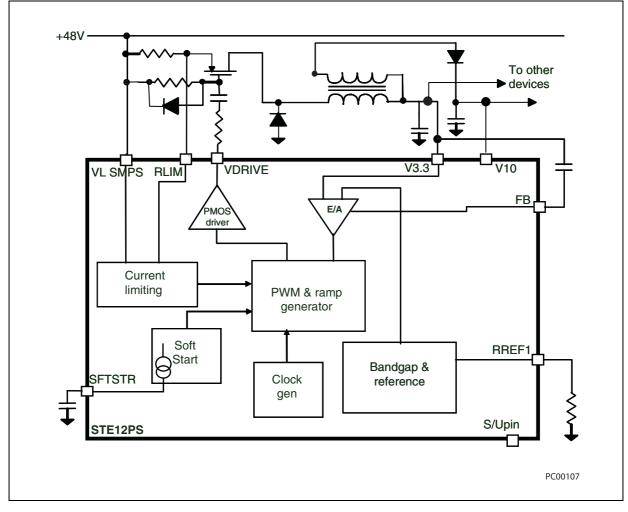

In *Figure 7*, use of a small transformer for the 10V supply can save up to 0.3W for each powered device. Both the 3.3V and 10V supplies can power others devices.

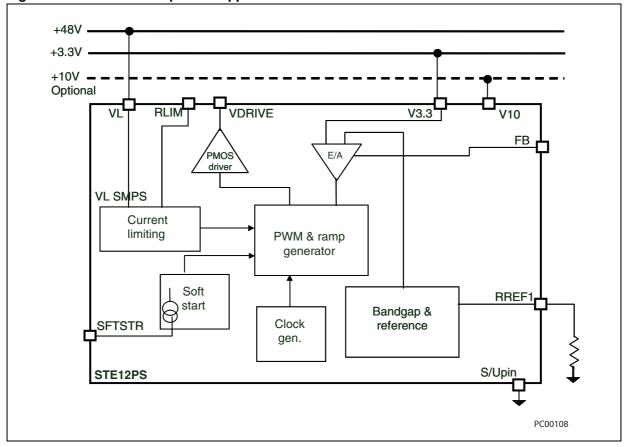

Figure 8 depicts a typical application with an external supply.

## 3.5 Logic interface

The STE12PS can operate autonomously - notifying, externally, ports status via dedicated pins (Parallel Monitor Interface) - or it can be controlled as a slave device via the  $I^2C$  interface by a host processor. In the latter case, the host can perform system configurations, monitor status conditions and assert alarm flags making it possible to drive, manually, different operations for detection, classification and monitoring.

#### Figure 6. Simple SMPS

#### Figure 7. Advanced SMPS

# 3.6 6MHz clock generator

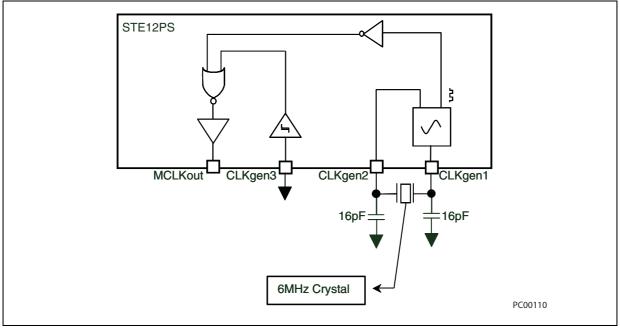

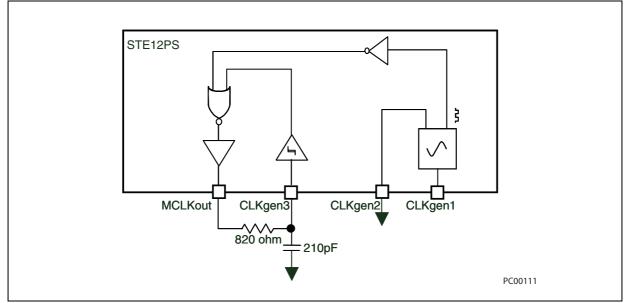

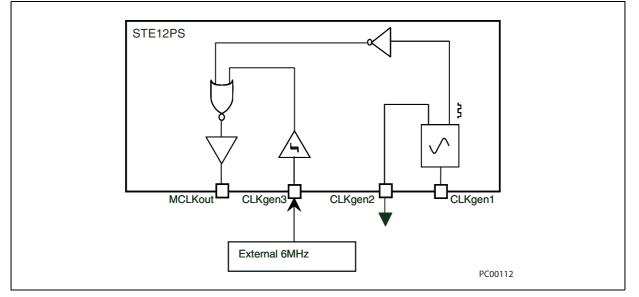

*Figure 10 on page 23*, and *Figure 11* and *Figure 12 on page 24* show the three possible clock generation configurations:

- a) with a 6MHz crystal for a high precision clock,

- b) with an external RC for low-cost applications,

- c) with an external clock.

# 3.7 Smart-power mode

When this mode is enabled, the whole system is set to manage and deliver a limited amount of power to the channel. In Auto Mode, it is actually possible to set a maximum power budget for the device. When a PD is connected to a port, the STE12PS verifies the class and decides to power the line only if there's enough power available. It is also possible to set different priorities for the different channels. The device probes channels starting with those of highest priority. In case of shortage of available power, it is possible to disable the powering of newly detected ports of lower priority until the ones with a higher detected priority are serviced. If a channel exceeds its power class, that channel can be powered-down, and its power made available again. A 12-bit ADC is used to provide high-quality voltage and current measurements during the various phases of port detection,

classification and powering. These measurements can be loaded into dedicated registers via the I<sup>2</sup>C bus and are intended to be averaged over time in order to maximize PSSR and noise rejection as well as minimize 50 to 60Hz interference.

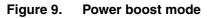

## 3.8 Power boost mode - 30W

When this mode is activated, the device will run the classification extending the IEEE classes with an extra PD\_Class boost as detailed in *Table 4*. If class boost is detected, an equivalent double port (parallel of two channels) is switched-on allowing up to 30W of power to be supplied. All the other IEEE classes behave as a standard port (powering on one channel only). *Table 5* below describes channel parallelism:

Table 5.

Power boost mode: master/slave channel parallelism

| Master Channel (MC) | Slave Channel (SC) |

|---------------------|--------------------|

| 1                   | 5                  |

| 2                   | 6                  |

| 3                   | 7                  |

| 4                   | 8                  |

Channels in boost mode behave as master or slave according to the above table.

Detection and classification are performed only on the master ports. If a class 0 to 4 PD is detected, only MC is powered. Otherwise, if Boost Class is detected, both MC and the related SC are powered. Once powered, any fault condition (short circuit, over current, over power, PD disconnection) occurring either for MC or SC forces the reaction of both channels. All status and measurement information are stored in registers pertaining to the MC. Detection procedure is the same as the standard one while the classification phase is performed with 3 classification impulses (total classification time 70ms).

#### STE12PS

#### Figure 10. Crystal oscillator

#### Figure 11. Low cost RC oscillator

### Figure 12. With external oscillator

# 3.9 Measurement and parameter codings

*Table 6* below lists codifications for the various parameters such as detection conductance or resistances, classification or monitoring currents, port voltages, port powers and power budgets.

| Parameter                     | Description                        | Range      | Step      | Units | Number of steps |  |

|-------------------------------|------------------------------------|------------|-----------|-------|-----------------|--|

| Idet                          | Detection current                  | 0 to 1023  | 1         | μA    | 1024            |  |

| Gdet, Gdl, Gdh                | Detection conductances             | 0 to 256   | 0.250     | μS    | 1024            |  |

| Rdet, Rdl, Rdh <sup>(1)</sup> | Detection residences               | 8 to 48.96 | 0.01      | KΩ    | 4096            |  |

| Iclass                        | Current classification             | 0 to 70    | 0.065064  | mA    | 1024            |  |

| Imon                          | Channel current during<br>powering | 0 to 1024  | 0.0312662 | mA    | 32768           |  |

| Vport                         | Battery voltage                    | 0 to 70    | 0.27451   | V     | 256             |  |

| Pmeas                         | Channel power usage                | 0 to 35000 | 35.149    | mW    | 1024            |  |

Table 6. Measurement and parameter codings

1. Rdet, Rdl and Rdh are the alternative to Gdet, Gdl and Gdh which are the default. If Rdet measures more than 500 kohms, the "open-circuit" flag is raised, that is set HIGH.

# 4 I2C interface

The STE12PS has an I2C interface to allow the access to the internal device registers. The external controller can be fully isolated from the Ethernet port thanks to an integrated 3.3V SMPS power source and using optocouplers on I2C bus.(*Figure 13*).

# 5 I<sup>2</sup>C slave protocol overview

The interface is capable of recognizing its own address (7 bit).

Data and addresses are transferred as 8-bit bytes, MSB first. The first byte following the start condition contains the device address.

A 9th clock pulse follows the 8 clock cycles of a byte transfer during which the receiver must pull LOW the SDA line to acknowledge the transfer.

The speed of the  $I^2C$  interface is fixed at Fast  $I^2C$ , that is, 100 to 400kHz.

# 5.1 Functional description

As soon as a start condition is detected, the address is received from the SDA line and sent to a shift register; then it is compared with the internal address that is composed by the five pins for the five LSB and by a hardwired value equal to "01" for the other two bits.

In case of address mismatch the interface ignores it and waits for another Start condition.

If address is matched the interface generates an acknowledge pulse.

Following the address reception, POE digital controller receives bytes from the SDA line into the data register via an internal shift register or sends bytes from the data register to the SDA line through the internal shift register. After each byte reception an acknowledge pulse is generated by the controller.

A Stop condition generated by the host processor, after the last data byte is transferred, closes the communication.

### 5.2 Error cases

An error state is generated when Stop or Start conditions are detected during a byte transfer. If it is a Stop then the interface discards the data, releases the lines and waits for another Start condition. If it is a Start then the interface discards the data and waits for the next slave address on the bus.

## 5.3 Interrupts

*Irq* register bits indicate which signals can generate an interrupt. The register is read only and to clear the interrupt bits the corresponding source event has to be cleared. The logic OR condition of the interrupt bits causes the INTN pin assertion. The INTN assertion can be masked via the interrupt mask register *Irq\_mask*.

# 5.4 I<sup>2</sup>C device address

The device is required to have an  $I^2C$  address of: 01xxxxxb(A6 down to A0).

Pins I2C\_ADDR[4:0] can be used to set the lower I<sup>2</sup>C address bits.

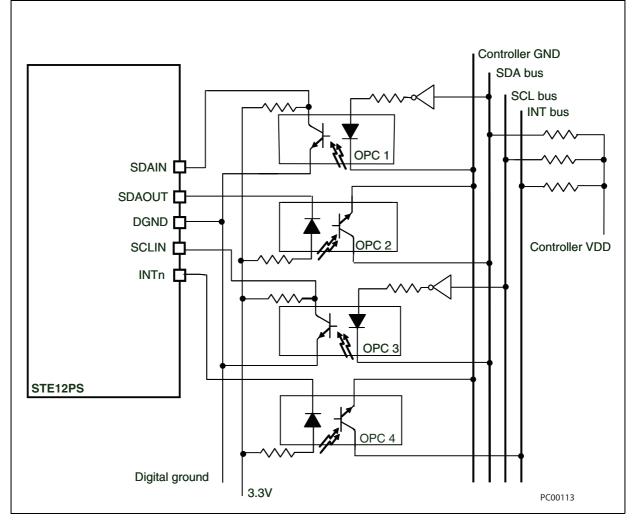

## 5.5 Register addressing: write command format

I<sup>2</sup>C write command format is shown in *Figure 14*.

#### Figure 14. Write command

The formatting bits shown in *Figure 14* are defined as follows:

- S I<sup>2</sup>C start condition

- P I<sup>2</sup>C stop condition

- ACK acknowledge

- NACK not acknowledge

- R/W read/write

The device address is the value specified in  $I^2C$  device address. The register address is an eight-bit value that is written into an internal Index Register. Each time a byte of data is written to, or read from the POE controller, the Index Register increments by one.

If the initial value written to the Index Register is K, then the byte immediately following the Register Address byte is written to the register with an address of K. The next byte is written to the register with the address of K+1, and so on.

An I<sup>2</sup>C write command can contain from 0 to 255 write data bytes. Write commands to an unknown register location are ignored by the interface.

As shown in *Figure 14*, bits are ordered with the most significant bit first.

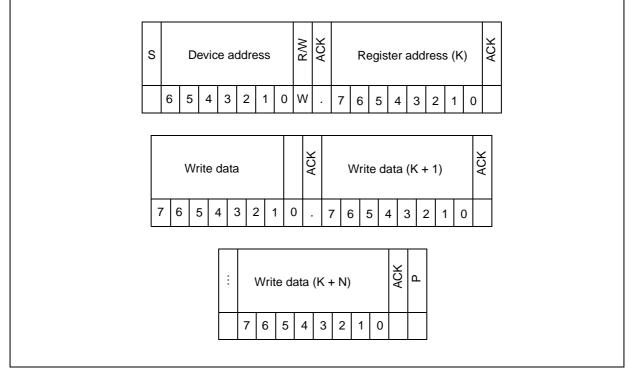

## 5.6 Register addressing: read command format

The general format of the read command is shown in *Figure 15*.

First part of the general read command consists of writing an address to the Index Register of the POE controller. If the Index Register already contains the address of the register to be read, as the result of a previous read or write command, then it is not necessary to write that address to the Index Register again.

After each byte is read from the POE controller, the Index Register is required to increment by one.

A read command can contain from 0 to 255 bytes.

#### Figure 15. Read command

## 5.7 Parallel monitoring interface

In order to monitor the status of the different ports without the I<sup>2</sup>C register addressing, a simple, output status interface has been implemented.

This digital interface is comprised of 9 output pins: CH\_SEL[3:0], POK, OVLD, OVCUR, AC\_DC\_DISCON and DET\_CLASS.

Bits *CH\_SEL[3:0]* indicate the channel status flags (POK,..., DET\_CLASS) that are currently notified, externally. CH\_SEL is incremented every 60MCLK clock cycles.

*POK* stands for Power OK. When HIGH, it indicates that the channel is currently powered-on in normal condition.

*OVLD* stands for OverLoad and indicates a faulty condition due to abnormal power dissipation (more than Pclass) of a powered channel.

*OVCUR* stands for OverCurrent, and it highlights a channel whose current has reached the power-on current limit of 425mA (typ. value).

Bit *AC\_DC\_DISCON* goes HIGH when a powered channel fails in providing a correct MPS (maintain power signature). This typically happens when a PD is disconnected from the line.

*DET\_CLASS* indicates a situation where a channel is not yet powered and whose "signature" is currently being probed.

Status flag notification is enabled by bit STATUS\_FLAG\_EN of the configuration register Global\_cfg2. By default this bit is HIGH, that is, enabled.

This information is particularly useful in simple applications without a microprocessor or for testing purposes. Another use is to easily build-up an LED graphical interface showing runtime status of the various channels.

# 6 Electrical specifications and timings

| Symbol             | Parameter                    | Value | Units |

|--------------------|------------------------------|-------|-------|

| $V_L$ , SMPS $V_L$ | Battery voltage              | 90    | V     |

| Vcc3,Vdd,Vdde      | 3.3V power supply            | 3.6   | V     |

| V10,Vdd10          | 10V power supply             | 12    | V     |

| Тј                 | Maximum junction temperature | 150   | °C    |

#### Table 7. Absolute maximum ratings

#### Table 8.Operating range

| Symbol                                | Parameter                                                 | Value      | Units |

|---------------------------------------|-----------------------------------------------------------|------------|-------|

| T <sub>opt</sub>                      | Operating temperature range                               | -20 to +85 | °C    |

| V <sub>L</sub> , SMPSV <sub>L</sub>   | Battery voltage                                           | 44 to 57   | V     |

| GNDs                                  | Ground separation                                         | -0.3       | V     |

| Vcc3, Vdd, Vdde                       | 3.3V when externally supplied                             | 3 to 3.6   | V     |

| V10, Vdd10                            | 10V when externally supplied                              | 9 to 11    | V     |

| I <sub>V10</sub> , I <sub>Vdd10</sub> | 10V current sink (when externally supplied)               | 6.7 typ.   | mA    |

| I <sub>VI</sub>                       | Battery current sink<br>(when 10V is externally supplied) | 0.4 typ.   | mA    |

| I <sub>VI</sub>                       | Battery current sink<br>(when 10V is self generated)      | 7.4 typ.   | mA    |

| I <sub>v3.3</sub>                     | 3.3V current sink (AUTO mode)                             | 20 typ.    | mA    |

#### Table 9. Thermal data

| Symbol                | Parameter                                                   | Value | Units |

|-----------------------|-------------------------------------------------------------|-------|-------|

| R <sub>th j-amb</sub> | Thermal resistance junction-to-ambient (natural convection) | 25    | ° C/W |

| Table 10.   | 0. Electrical characteristics                                            |      |      |      |       |                                                                                                                                          |

|-------------|--------------------------------------------------------------------------|------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol      | Parameter                                                                | Min. | Тур. | Max. | Units | Notes                                                                                                                                    |

| Detection   |                                                                          |      |      |      | •     |                                                                                                                                          |

| VdI         | Detection voltage LOW level                                              | 3.7  | 4    | 4.3  | V     | Between port terminals                                                                                                                   |

| Vdh         | Detection voltage HIGH level                                             | 7.4  | 8    | 8.6  | V     | Between port terminals                                                                                                                   |

| Tds         | Transient time between VdI and Vdh                                       | 300  |      |      | μs    | Adjustable with external capacitor Cdetslow                                                                                              |

| Gdl         | Conductance signature, lower<br>limit<br>(Software programmable)         | 25   |      | 50   | µmhos | Software programmable)                                                                                                                   |

| Gdh         | Conductance signature, upper<br>limit<br>(Software programmable)         | 41   |      | 82   | µmhos | Software programmable                                                                                                                    |

| Rdl         | Resistance signature, lower limit<br>(Software programmable)             | 12   |      | 24   | kΩ    | Software programmable,<br>to be used as an<br>alternative to Gdh                                                                         |

| Rdh         | Resistance signature, upper limit<br>(Software programmable)             | 20   |      | 40   | kΩ    | Software programmable,<br>to be used as an<br>alternative to Gdl                                                                         |

| Idlim       | Current limit during detection                                           |      |      | 1.1  | mA    |                                                                                                                                          |

| Tdet        | Detection time                                                           |      | 50   |      | ms    | 12-port configuration, one channel at a time                                                                                             |

| Tdetd       | Detection delay time<br>(from PD insertion to end of<br>detection phase) |      |      | 852  | ms    | Maximum delay for 12-<br>port configuration                                                                                              |

| Tdbo        | Back-off time (midspan mode)                                             | 2    |      |      | sec.  | Back off time in case of failed PD detection, avoided if Rdet > $500 k\Omega$ or Gdet < $2 \mu$ mhos                                     |

| Ted         | Error delay time                                                         | 750  |      |      | ms    |                                                                                                                                          |

| Classificat | ion                                                                      |      |      |      |       |                                                                                                                                          |

| Vcl         | Classification probing voltage                                           | 15.9 | 17   | 18.1 | V     | Between port terminals                                                                                                                   |

| Icllim      | Current limit during classification                                      | 55   |      | 70   | mA    |                                                                                                                                          |

| Tcl         | Classification time                                                      |      | 15   |      | ms    | One channel at a time,<br>classification<br>measurement has to be<br>considered as sampled<br>and integrated over this<br>time interval. |

| Ithcl0      | Class0-1 current threshold                                               | 5.5  | 6.5  | 7.5  | mA    |                                                                                                                                          |

| Ithcl1      | Class1-2 current threshold                                               | 13.5 | 14.5 | 15.5 | mA    |                                                                                                                                          |

| Ithcl2      | Class2-3 current threshold                                               | 21.8 | 23   | 24.2 | mA    |                                                                                                                                          |

| Ithcl3      | Class3-4 current threshold                                               | 31.5 | 33   | 34.5 | mA    |                                                                                                                                          |

### Table 10. Electrical characteristics

| Symbol           | Parameter                                                                      | Min.       | Тур. | Max. | Units           | Notes                                                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------|------------|------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ithcl4           | Class4-0 current threshold                                                     | 45.5       | 46.5 | 47.5 | mA              |                                                                                                                                                                                                                                                                  |

| Powering         |                                                                                |            |      | •    | 1               | 1                                                                                                                                                                                                                                                                |

| Pall             | Maximum power per channel                                                      |            |      | 15.4 | W               | See also classification<br>paragraph<br>(doubled in case of Boost<br>configuration)                                                                                                                                                                              |

| linrush          | Output current startup mode                                                    | 400        |      | 450  | mA              | Inrush current soft start                                                                                                                                                                                                                                        |

| Imin             | Power off current                                                              | 5          |      | 10   | mA              | Disconnect for t ><br>TPMDO (DC<br>disconnection method)                                                                                                                                                                                                         |

| Acfre            | AC disconnection sinusoidal generator                                          |            | 50   |      | Hz              | Frequency spread related to clock stability                                                                                                                                                                                                                      |

| Vacd             | AC generator open line voltage                                                 |            | 2.5  |      | V <sub>pp</sub> |                                                                                                                                                                                                                                                                  |

| Zac              | AC impedance needed to maintain power                                          |            | 100  |      | kΩ              |                                                                                                                                                                                                                                                                  |

| Tmpdo            | PD power maintenance request<br>drop out time limit<br>(Software programmable) | 300        |      | 400  | ms              | The STE12PS will not<br>remove power if the PD<br>maintenance signal is<br>absent for less than<br>300ms duration. If an<br>absence of power<br>maintenance signal has<br>been detected, the<br>STE12PS shall remove<br>power within 400ms<br>max <sup>(1)</sup> |

| lcut             | Over load current                                                              | Pall/Vport |      | 400  | mA              | After time duration of<br>Tovld the STE12PS will<br>disconnect the power<br>from the port.                                                                                                                                                                       |

| Tovld            | Over load time limit<br>(Software programmable)                                | 50         | 65   | 75   | ms              | In fault condition for<br>Tovld, the STE12PS will<br>disconnect the port. <sup>(1)</sup>                                                                                                                                                                         |

| Tshort           | Short-circuit/inrush time limit<br>(Software programmable)                     | 50         | 65   | 75   | ms              | In fault condition for<br>Tshort, the STE12PS will<br>disconnect the port. <sup>(1)</sup>                                                                                                                                                                        |

| I <sub>lim</sub> | Output load current under short -<br>circuit condition                         | 400        |      | 450  | mA              | Max. value of port current<br>during short circuit<br>condition. Power will be<br>disconnected from the<br>port within Tshort                                                                                                                                    |

| Tinrush          | Rise time of Vport time limit                                                  |            |      | 75   | ms              | Expired Tinrush if the<br>channel is still in limiting<br>condition it is considered<br>in fault                                                                                                                                                                 |

\_\_\_\_

Table 10.

Electrical characteristics (continued)

| Parameter                                | Min.                                                                                                                                                                                                                      | Тур.                                                                                                                                                                                                                                                                                                      | Max.                                                                                                                                                                                                                                                                                                                                                                                     | Units                                                                                                                                                                                                                                            | Notes                                                                                                                                                                                                                             |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Turn off time                            |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                           | 100                                                                                                                                                                                                                                                                                                                                                                                      | ms                                                                                                                                                                                                                                               | From VPort to 2.8V DC                                                                                                                                                                                                             |

| Internal MOSFET resistance in<br>ON mode |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                        | ohms                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                   |