# 82C814 Docking Station Controller Preliminary Data Book

Revision: 2.0 912-2000-016 October 31, 1996

#### Copyright

Copyright © 1996, OPTi Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of OPTi Incorporated, 888 Tasman Drive, Milpitas, CA 95035.

#### **Disclaimer**

OPTi Inc. makes no representations or warranties with respect to the design and documentation herein described and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, OPTi Inc. reserves the right to revise the design and associated documentation and to make changes from time to time in the content without obligation of OPTi Inc. to notify any person of such revisions or changes.

Note: Before designing contact OPTi for latest Product Alerts, Applications Notes, and Errata for this product line.

#### **Trademarks**

OPTi and OPTi Inc. are registered trademarks of OPTi Inc. All other trademarks and copyrights are the property of their respective holders.

#### **OPTi Inc.**

888 Tasman Drive Milpitas, CA 95035 Tel: (408) 486-8000 Fax: (408) 486-8001

Fax: (408) 486-8001 WWW: http://www.opti.com/

# **Table of Contents**

| 1.0 | Features   |          |                                                                    |    |  |

|-----|------------|----------|--------------------------------------------------------------------|----|--|

| 2.0 | ) Overview |          |                                                                    |    |  |

|     |            |          |                                                                    | _  |  |

| 3.0 | Sigi       | nal Defi | initions                                                           | 2  |  |

|     | 3.1        | Termin   | nology/Nomenclature Conventions                                    | 2  |  |

|     | 3.2        | Signal   | Descriptions                                                       | €  |  |

|     |            | 3.2.1    | Host Interface PCI Signals                                         |    |  |

|     |            | 3.2.2    | Docking Control and Sense Signals                                  |    |  |

|     |            | 3.2.3    | PCI Docking Interface Pins                                         | 7  |  |

|     |            | 3.2.4    | Interrupt Interface Pins                                           | 8  |  |

|     | 3.3        | Strap-9  | Selected Interface Options                                         |    |  |

|     |            | 3.2.5    | Power, Ground and No Connect Pins                                  |    |  |

|     | 3.4        | Interna  | al Resistors                                                       | 1( |  |

|     | 0.4        | mtorrie  |                                                                    |    |  |

| 4.0 | Fun        | ctional  | Description                                                        | 11 |  |

|     | 4.1        | OPTi D   | Oocking Station Controller Chipset                                 | 11 |  |

|     | 4.2        | Chipse   | et Compatibility                                                   | 11 |  |

|     | 4.3        | Interfa  | ce Overview                                                        | 11 |  |

|     | 4.4        | Device   | Type Detection Logic                                               | 12 |  |

|     | 4.5        | Primar   | y PCI Bus                                                          | 13 |  |

|     | 4.6        | PCI-to-  | -CardBus Bridge                                                    | 13 |  |

|     |            | 4.6.1    | Configuration Cycle                                                |    |  |

|     |            |          | 4.6.1.1 Translation Between Type 0 and Type 1 Configuration Cycles | 13 |  |

|     |            | 4.6.2    | Cycle from Host to Docking Interface                               | 14 |  |

|     |            | 4.6.3    | Master Cycle from Docking Interface                                | 14 |  |

|     |            | 4.6.4    | Inability to Complete a Posted Write                               | 14 |  |

|     |            | 4.6.5    | Cycle Termination by Target                                        |    |  |

|     |            |          | 4.6.5.1 Posted Write Termination                                   |    |  |

|     |            |          | 4.6.5.2 Non-Posted Write Termination                               |    |  |

|     |            |          | 4.6.5.3 Read (Prefetched or Non-Prefetched) Termination            | 14 |  |

# *Preliminary* **82C814**

## Table of Contents (cont.)

| 4.7 | PCI Do                          | ocking Station Operation                                                                                                                                                                   | 15                                 |

|-----|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|     | 4.7.1                           | Introduction                                                                                                                                                                               | 15                                 |

|     | 4.7.2                           | Procedure                                                                                                                                                                                  | 15                                 |

|     | 4.7.3                           | Initial Setup                                                                                                                                                                              | 15                                 |

|     | 4.7.4                           | Action Upon Attachment of Dock                                                                                                                                                             | 16                                 |

| 4.8 | Status                          | s Change Service Routine                                                                                                                                                                   | 17                                 |

|     | 4.8.1                           | Docking Event                                                                                                                                                                              | 17                                 |

|     | 4.8.2                           | Undocking Event                                                                                                                                                                            | 17                                 |

|     | 4.8.3                           | Notes on Undocking                                                                                                                                                                         | 17                                 |

|     | 4.8.4                           | Retest                                                                                                                                                                                     | 17                                 |

|     | 4.8.5                           | PCI Clock Buffering                                                                                                                                                                        | 18                                 |

| 4.9 | Interru                         | upt Support                                                                                                                                                                                | 18                                 |

|     | 4.9.1                           | PCI INTx# Implementation                                                                                                                                                                   | 18                                 |

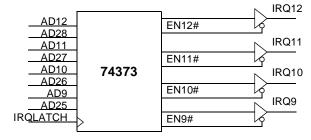

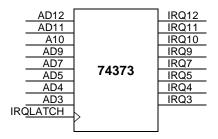

|     | 4.9.2                           | IRQ Driveback Logic                                                                                                                                                                        | 18                                 |

|     |                                 | 4.9.2.1 Interrupt Status Return Latency                                                                                                                                                    | 19                                 |

|     |                                 | , ,                                                                                                                                                                                        |                                    |

|     |                                 | •                                                                                                                                                                                          |                                    |

|     | 4.9.3                           | ·                                                                                                                                                                                          |                                    |

|     | 404                             | ·                                                                                                                                                                                          |                                    |

|     | 4.9.4                           | • •                                                                                                                                                                                        |                                    |

|     |                                 | 4.9.4.1 Operation                                                                                                                                                                          | 22                                 |

| 82C | 814 Re                          | egister Set                                                                                                                                                                                | 23                                 |

| 5.1 | Regist                          | ter State on Device Removal                                                                                                                                                                | 23                                 |

| 5.2 | Base I                          | Register Group                                                                                                                                                                             | 23                                 |

| 5.3 | 82C81                           | 4-Specific Register Group                                                                                                                                                                  | 31                                 |

|     | 5.3.1                           | IRQLATCH                                                                                                                                                                                   | 31                                 |

|     | 5.3.2                           | CLKRUN#                                                                                                                                                                                    | 31                                 |

|     | 5.3.3                           | Slot Buffer Enable, Slew Rate, and Threshold Control                                                                                                                                       | 31                                 |

|     | 5.3.4                           | Dual ISA Buses                                                                                                                                                                             | 31                                 |

| 5.4 | CardB                           | Bus Register Group                                                                                                                                                                         | 34                                 |

|     | 5.4.1                           | Power Control                                                                                                                                                                              | 34                                 |

|     | 4.8<br>4.9<br>5.1<br>5.2<br>5.3 | 4.7.1 4.7.2 4.7.3 4.7.4  4.8  4.8.1 4.8.2 4.8.3 4.8.4 4.8.5  4.9  Interreduction 4.9.1 4.9.2  4.9.3 4.9.4  82C814 Reference 5.1 Register 5.2 Base 5.3 5.3.1 5.3.2 5.3.3 5.3.4  5.4 Cardian | 4.7.1 Introduction 4.7.2 Procedure |

## Table of Contents (cont.)

|     | 5.5  | Dockir  | ng Station | Window Selection Group                          | 37 |

|-----|------|---------|------------|-------------------------------------------------|----|

|     |      | 5.5.1   | Warning    | g on Using Docking Station Windows              | 37 |

|     |      | 5.5.2   | Docking    | Station Window Registers                        | 37 |

|     |      |         | 5.5.2.1    | Cycle Decoding                                  |    |

|     |      |         | 5.5.2.2    | Cycle Trapping                                  | 38 |

|     |      |         | 5.5.2.3    | ISA Window Selection                            | 38 |

|     | 5.6  | Regist  | er Summ    | ary                                             | 45 |

| 6.0 | Elec | ctrical | Ratings    |                                                 | 48 |

|     | 6.1  | Absolu  | ute Maxim  | num Ratings                                     | 48 |

|     | 6.2  | DC Ch   | aracterist | tics: VCC = 3.3V or 5.0V ±5%, TA = 0°C to +70°C | 48 |

|     | 6.3  | AC Ch   | aracterist | tics                                            | 49 |

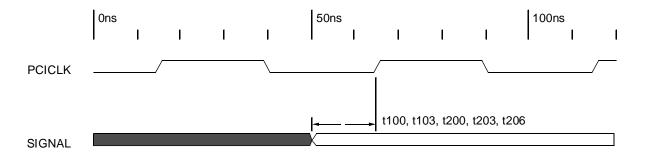

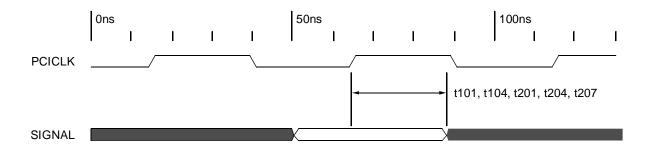

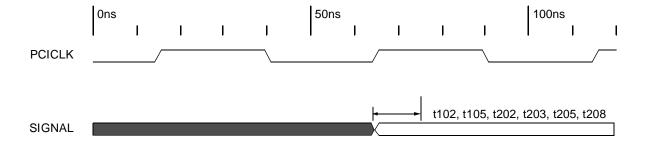

|     | 6.4  | AC Tir  | ning Diag  | rams                                            | 50 |

| 7.0 | Med  | hnical  | Packag     | e Outline                                       | 51 |

| Арр | endi | x A II  | RQ Drive   | eback Protocol                                  | 53 |

|     | A.1  | Driveb  | ack Cycle  | e Format                                        | 53 |

|     | A.2  | Edge v  | vs Level N | flode, IRQ Polarity                             | 54 |

|     | A.3  | Host F  | landling o | of IRQ Driveback Information                    | 54 |

|     | Δ 4  | Fytern  | al Imnlem  | nentation                                       | 54 |

# *Preliminary* **82C814**

Page vi 912-2000-016

Revision: 2.0

# **List of Figures**

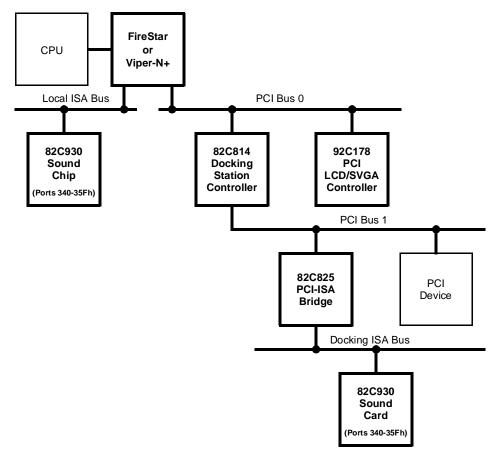

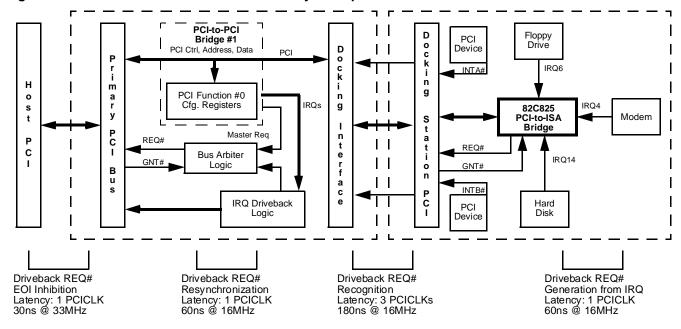

| Figure 2-1 | Multiple ISA Bus Support                  | 1  |

|------------|-------------------------------------------|----|

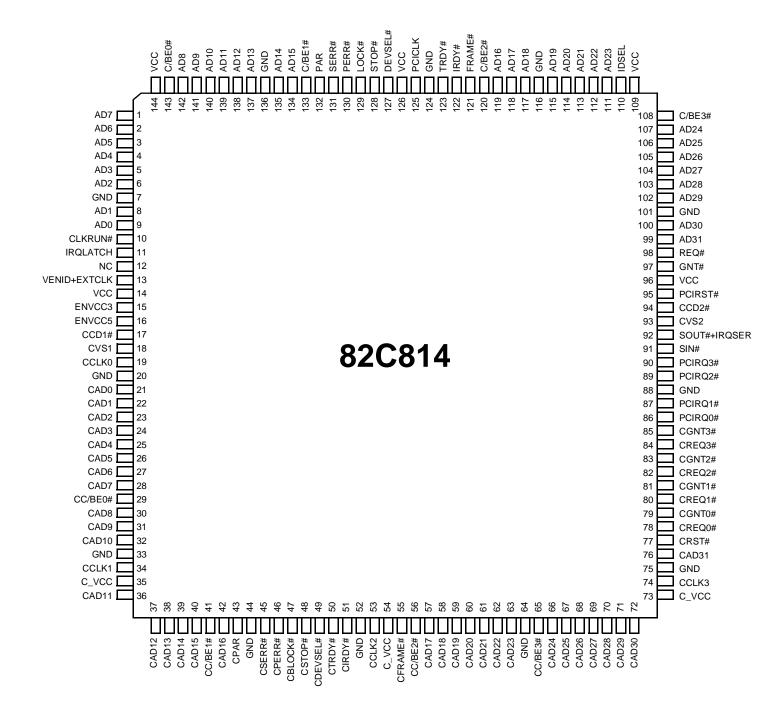

| Figure 3-1 | Pin Diagram                               | 3  |

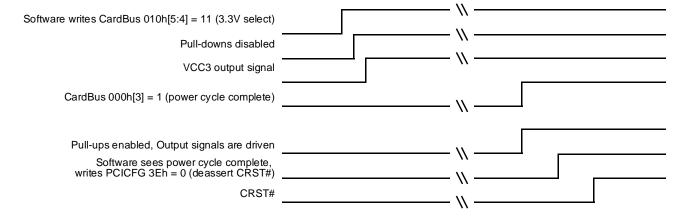

| Figure 3-2 | Power-Up Timing                           | 10 |

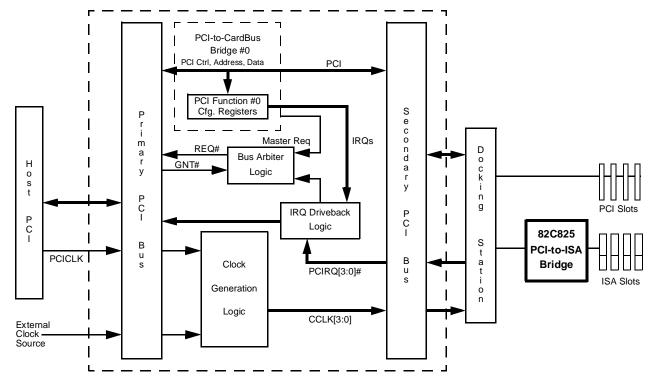

| Figure 4-1 | 82C814 Organization                       |    |

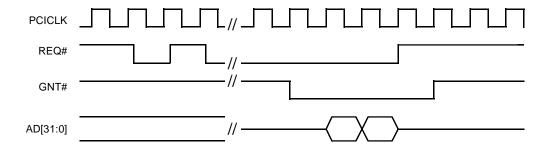

| Figure 4-2 | Worst Case IRQ Driveback Latency Example  | 19 |

| Figure 6-1 | Setup Timing Waveform                     | 50 |

| Figure 6-2 | Hold Timing Waveform                      | 50 |

| Figure 6-3 | Output Delay Timing Waveform              | 50 |

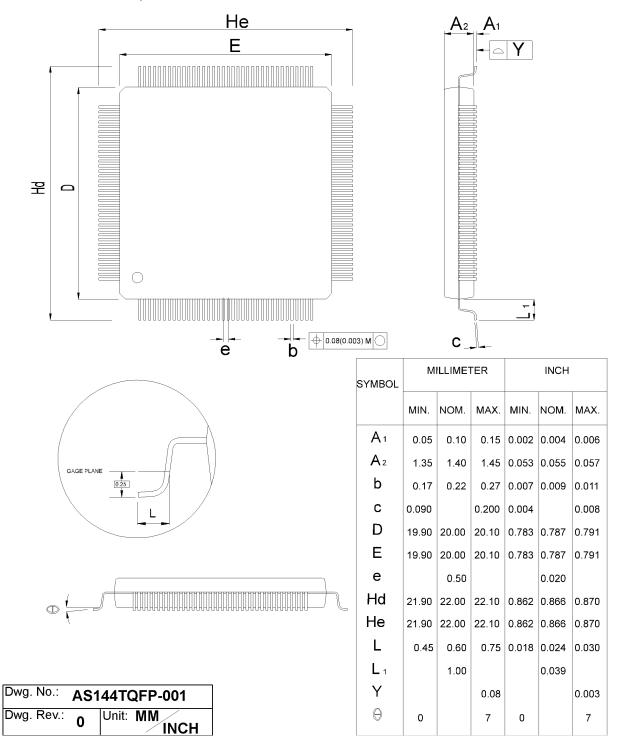

| Figure 7-1 | 144-Pin TQFP, Thin Quad Flat Pack         | 51 |

| Figure A-1 | IRQ Driveback Cycle High-Priority Request | 53 |

| Figure A-2 | Dynamic Resourcing                        | 55 |

| Figure A-3 | Static Resourcing                         | 55 |

# *Preliminary* **82C814**

Page viii 912-200

# **List of Tables**

| Table 3-1 | Signal Definitions Legend                                                  | 2  |

|-----------|----------------------------------------------------------------------------|----|

| Table 3-2 | Numerical Pin Cross-Reference List                                         |    |

| Table 3-3 | Alphabetical Pin Cross-Reference List                                      | 5  |

| Table 3-4 | Strap Options for 82C814 Configurations                                    |    |

| Table 3-5 | Internal Keeper Resistor Scheme                                            | 10 |

| Table 4-1 | Device Detection (CardBus Rules)                                           | 12 |

| Table 4-2 | CLKRUN# Control Bits                                                       | 13 |

| Table 4-3 | Translation Feature Configuration Bit                                      | 13 |

| Table 4-4 | Write Posting Associated Registers                                         | 14 |

| Table 4-5 | Summary of Typical Settings (using IRQ5 for SMI)                           | 16 |

| Table 4-6 | Register used to Delay Internal PCICLK to Compensate for Trace Delays      | 18 |

| Table 4-7 | EOI Delay Setting                                                          | 20 |

| Table 4-8 | Intel SIRQ Control Bit                                                     | 21 |

| Table 4-9 | Compaq SIRQ Control Bits                                                   | 22 |

| Table 5-1 | Base Register Group - PCICFG 00h-4Fh                                       | 23 |

| Table 5-2 | Specific Register Group - PCICFG 50h-5Fh                                   | 31 |

| Table 5-3 | CardBus Register Set in System Memory                                      | 34 |

| Table 5-4 | CardBus Register Group - PCICFG 60h-74h / MEMOFST 00h-7Fh                  | 34 |

| Table 5-5 | Docking Station Access Windows                                             | 37 |

| Table 5-6 | Power-on Reset, Card Removal Defaults for Docking Station Window Registers | 37 |

| Table 5-7 | Docking Station Window Registers - PCICFG 80h-FFh                          | 38 |

| Table 5-8 | 82C814 Register Summary                                                    | 45 |

| Table A-1 | Information Provided on a Driveback Cycle                                  | 53 |

| Table A-2 | Information Provided on a Optional Data Phase 2 of IRQ Driveback Cycle     | 54 |

# *Preliminary* **82C814**

Page x 912-200

## **Docking Station Controller**

#### 1.0 Features

- · Provides true hot docking and undocking

- Supports 3.3V or 5.0V PCI dock

- Host PCI bus can be 3.3V or 5.0V

- Works in conjunction with 82C825 PCI-to-ISA bridge to provide reliable ISA support on the dock

- Provides eight windows, selectable for memory or I/O

- · Offers additional fixed window for VGA

- Supports INTA#, INTB#, INTC#, INTD#

- · Supports four bus masters

- · Generates PCI clocks for four devices

- Bridge solution increases primary PCI bus bandwidth by off-loading transactions into buffers

- · Packaged in 144-pin TQFP (Thin Quad Flat Pack)

#### 2.0 Overview

This document describes the OPTi 82C814 Docking Station Controller, a true bridge docking solution that allows software to treat the docking station like a dynamically insertable/removable CardBus card.

The PCI software interface conforms to the CardBus header layout, instead of the PCI-to-PCI bridge header layout, to overcome the limitations of PCI-to-PCI bridges.

The docking controller implements a true PCI-PCI bridge with full buffering and synchronous or asynchronous operation.

Figure 2-1 Multiple ISA Bus Support

#### 3.0 Signal Definitions

The 82C814 chip provides a primary interface which is PCI-based. It also provides an independent attachment interface, which can be switched on and off dynamically.

# 3.1 Terminology/Nomenclature Conventions

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms "assertion" and "negation" are used extensively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term "assert", or "assertion" indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term "negate", or "negation" indicates that a signal is inactive.

The 82C814 has some pins that have multiple functions (denoted by "+" in the pin name). These functions are either:

- cycle-multiplexed (always enabled and available when a particular cycle is in progress),

- a strap option (configured at reset),

- · or selected via register programming.

The tables in this section use several common abbreviations. Table 3-1 lists the mnemonics and their meanings.

Table 3-1 Signal Definitions Legend

|          | <b>5</b>                                          |

|----------|---------------------------------------------------|

| Mnemonic | Description                                       |

| CMOS     | CMOS-level compatible                             |

| Dcdr     | Decoder                                           |

| Ext      | External                                          |

| G        | Ground                                            |

| I        | Input                                             |

| I/O      | Input/Output                                      |

| Int      | Internal                                          |

| Mux      | Multiplexer                                       |

| 0        | Output                                            |

| OD       | Open drain (open-collector) CMOS-level compatible |

| Р        | Power                                             |

| PD       | Pull-down resistor                                |

| PU       | Pull-up resistor                                  |

| S        | Schmitt-trigger TTL-level compatible              |

| TTL      | TTL-level compatible                              |

Page 2 912-2000-016

Figure 3-1 Pin Diagram

Table 3-2 Numerical Pin Cross-Reference List

| Pin<br>No. | Pin Name | Pin<br>Type |  |

|------------|----------|-------------|--|

| 1          | AD7      | I/O         |  |

| 2          | AD6      | I/O         |  |

| 3          | AD5      | I/O         |  |

| 4          | AD4      | I/O         |  |

| 5          | AD3      | I/O         |  |

| 6          | AD2      | I/O         |  |

| 7          | GND      | G           |  |

| 8          | AD1      | I/O         |  |

| 9          | AD0      | I/O         |  |

| 10         | CLKRUN#  | I/O         |  |

| 11         | IRQLATCH | I/O         |  |

| 12         | NC       |             |  |

| 13         | VENID    | 0           |  |

|            | EXTCLK   | I           |  |

| 14         | VCC      | Р           |  |

| 15         | ENVCC3   | 0           |  |

| 16         | ENVCC5   | 0           |  |

| 17         | CCD1#    | I           |  |

| 18         | CVS1     | I           |  |

| 19         | CCLK0    | 0           |  |

| 20         | GND      | G           |  |

| 21         | CAD0     | I/O         |  |

| 22         | CAD1     | I/O         |  |

| 23         | CAD2     | I/O         |  |

| 24         | CAD3     | I/O         |  |

| 25         | CAD4     | I/O         |  |

| 26         | CAD5     | I/O         |  |

| 27         | CAD6     | I/O         |  |

| 28         | CAD7     | I/O         |  |

| 29         | CC/BE0#  | 0           |  |

| 30         | CAD8     | I/O         |  |

| 31         | CAD9     | I/O         |  |

| 32         | CAD10    | I/O         |  |

| 33         | GND      | G           |  |

| 34         | CCLK1    | 0           |  |

| 35         | C_VCC    | Р           |  |

| 36         | CAD11    | I/O         |  |

| Cross-Reference List |          |             |  |  |

|----------------------|----------|-------------|--|--|

| Pin<br>No.           | Pin Name | Pin<br>Type |  |  |

| 37                   | CAD12    | I/O         |  |  |

| 38                   | CAD13    | I/O         |  |  |

| 39                   | CAD14    | I/O         |  |  |

| 40                   | CAD15    | I/O         |  |  |

| 41                   | CC/BE1#  | 0           |  |  |

| 42                   | CAD16    | I/O         |  |  |

| 43                   | CPAR     | I/O         |  |  |

| 44                   | GND      | G           |  |  |

| 45                   | CSERR#   | I           |  |  |

| 46                   | CPERR#   | I           |  |  |

| 47                   | CBLOCK#  | 0           |  |  |

| 48                   | CSTOP#   | I           |  |  |

| 49                   | CDEVSEL# | I           |  |  |

| 50                   | CTRDY#   | I           |  |  |

| 51                   | CIRDY#   | 0           |  |  |

| 52                   | GND      | G           |  |  |

| 53                   | CCLK2    | 0           |  |  |

| 54                   | C_VCC    | Р           |  |  |

| 55                   | CFRAME#  | 0           |  |  |

| 56                   | CC/BE2#  | 0           |  |  |

| 57                   | CAD17    | I/O         |  |  |

| 58                   | CAD18    | I/O         |  |  |

| 59                   | CAD19    | I/O         |  |  |

| 60                   | CAD20    | I/O         |  |  |

| 61                   | CAD21    | I/O         |  |  |

| 62                   | CAD22    | I/O         |  |  |

| 63                   | CAD23    | I/O         |  |  |

| 64                   | GND      | G           |  |  |

| 65                   | CC/BE3#  | 0           |  |  |

| 66                   | CAD24    | I/O         |  |  |

| 67                   | CAD25    | I/O         |  |  |

| 68                   | CAD26    | I/O         |  |  |

| 69                   | CAD27    | I/O         |  |  |

| 70                   | CAD28    | I/O         |  |  |

| 71                   | CAD29    | I/O         |  |  |

| 72                   | CAD30    | I/O         |  |  |

|                      |          |             |  |  |

| Pin<br>No. | Pin Name | Pin<br>Type |

|------------|----------|-------------|

| 74         | CCLK3    | 0           |

| 75         | GND      | G           |

| 76         | CAD31    | I/O         |

| 77         | CRST#    | 0           |

| 78         | CREQ0#   | I           |

| 79         | CGNT0#   | 0           |

| 80         | CREQ1#   | I           |

| 81         | CGNT1#   | 0           |

| 82         | CREQ2#   | I           |

| 83         | CGNT2#   | 0           |

| 84         | CREQ3#   | I           |

| 85         | CGNT3#   | 0           |

| 86         | PCIRQ0#  | I           |

| 87         | PCIRQ1#  | I           |

| 88         | GND      | G           |

| 89         | PCIRQ2#  | I           |

| 90         | PCIRQ3#  | I           |

| 91         | SIN#     | I           |

| 92         | SOUT#    | 0           |

|            | IRQSER   | I/O         |

| 93         | CVS2     | I           |

| 94         | CCD2#    | I           |

| 95         | PCIRST#  | I           |

| 96         | VCC      | Р           |

| 97         | GNT#     | I           |

| 98         | REQ#     | 0           |

| 99         | AD31     | I/O         |

| 100        | AD30     | I/O         |

| 101        | GND      | G           |

| 102        | AD29     | I/O         |

| 103        | AD28     | I/O         |

| 104        | AD27     | I/O         |

| 105        | AD26     | I/O         |

| 106        | AD25     | I/O         |

| 107        | AD24     | I/O         |

| 108        | C/BE3#   | I           |

| 109        | VCC      | Р           |

| Pin<br>No. | Pin Name | Pin<br>Type |

|------------|----------|-------------|

| 110        | IDSEL    | I           |

| 111        | AD23     | I/O         |

| 112        | AD22     | I/O         |

| 113        | AD21     | I/O         |

| 114        | AD20     | I/O         |

| 115        | AD19     | I/O         |

| 116        | GND      | G           |

| 117        | AD18     | I/O         |

| 118        | AD17     | I/O         |

| 119        | AD16     | I/O         |

| 120        | C/BE2#   | - 1         |

| 121        | FRAME#   | - 1         |

| 122        | IRDY#    | 1           |

| 123        | TRDY#    | 0           |

| 124        | GND      | G           |

| 125        | PCICLK   | 1           |

| 126        | VCC      | Р           |

| 127        | DEVSEL#  | 0           |

| 128        | STOP#    | 0           |

| 129        | LOCK#    | 1           |

| 130        | PERR#    | 0           |

| 131        | SERR#    | O/OD        |

| 132        | PAR      | I/O         |

| 133        | C/BE1#   | I           |

| 134        | AD15     | I/O         |

| 135        | AD14     | I/O         |

| 136        | GND      | G           |

| 137        | AD13     | I/O         |

| 138        | AD12     | I/O         |

| 139        | AD11     | I/O         |

| 140        | AD10     | I/O         |

| 141        | AD9      | I/O         |

| 142        | AD8      | I/O         |

| 143        | C/BE0#   | I           |

| 144        | VCC      | Р           |

Page 4

Table 3-3 Alphabetical Pin Cross-Reference List

| Pin<br>No. | Pin Name | Pin<br>Type |

|------------|----------|-------------|

| 9          | AD0      | I/O         |

| 8          | AD1      | I/O         |

| 6          | AD2      | I/O         |

| 5          | AD3      | I/O         |

| 4          | AD4      | I/O         |

| 3          | AD5      | I/O         |

| 2          | AD6      | I/O         |

| 1          | AD7      | I/O         |

| 142        | AD8      | I/O         |

| 141        | AD9      | I/O         |

| 140        | AD10     | I/O         |

| 139        | AD11     | I/O         |

| 138        | AD12     | I/O         |

| 137        | AD13     | I/O         |

| 135        | AD14     | I/O         |

| 134        | AD15     | I/O         |

| 119        | AD16     | I/O         |

| 118        | AD17     | I/O         |

| 117        | AD18     | I/O         |

| 115        | AD19     | I/O         |

| 114        | AD20     | I/O         |

| 113        | AD21     | I/O         |

| 112        | AD22     | I/O         |

| 111        | AD23     | I/O         |

| 107        | AD24     | I/O         |

| 106        | AD25     | I/O         |

| 105        | AD26     | I/O         |

| 104        | AD27     | I/O         |

| 103        | AD28     | I/O         |

| 102        | AD29     | I/O         |

| 100        | AD30     | I/O         |

| 99         | AD31     | I/O         |

| 21         | CAD0     | I/O         |

| 22         | CAD1     | I/O         |

| 23         | CAD2     | I/O         |

| 24         | CAD3     | I/O         |

| 25         | CAD4     | I/O         |

| Pin Cross-Reference List |                                                                                                                                                                                                                                                                                          |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                 | Pin<br>Type                                                                                                                                                                                                                                                                              |  |  |  |

| CAD5                     | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD6                     | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD7                     | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD8                     | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD9                     | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD10                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD11                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD12                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD13                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD14                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD15                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD16                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD17                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD18                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD19                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD20                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD21                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD22                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD23                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD24                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD25                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD26                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD27                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD28                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD29                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD30                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| CAD31                    | I/O                                                                                                                                                                                                                                                                                      |  |  |  |

| C/BE0#                   | 1                                                                                                                                                                                                                                                                                        |  |  |  |

| C/BE1#                   | I                                                                                                                                                                                                                                                                                        |  |  |  |

| C/BE2#                   | I                                                                                                                                                                                                                                                                                        |  |  |  |

| C/BE3#                   | I                                                                                                                                                                                                                                                                                        |  |  |  |

| CBLOCK#                  | 0                                                                                                                                                                                                                                                                                        |  |  |  |

| CC/BE0#                  | 0                                                                                                                                                                                                                                                                                        |  |  |  |

| CC/BE1#                  | 0                                                                                                                                                                                                                                                                                        |  |  |  |

| CC/BE2#                  | 0                                                                                                                                                                                                                                                                                        |  |  |  |

| CC/BE3#                  | 0                                                                                                                                                                                                                                                                                        |  |  |  |

|                          | Pin Name  CAD5  CAD6  CAD7  CAD8  CAD9  CAD10  CAD11  CAD12  CAD13  CAD14  CAD15  CAD16  CAD17  CAD18  CAD17  CAD20  CAD21  CAD21  CAD22  CAD23  CAD24  CAD25  CAD25  CAD26  CAD27  CAD28  CAD27  CAD28  CAD29  CAD30  CAD31  C/BE0#  C/BE1#  C/BE2#  CC/BE1#  CC/BE1#  CC/BE1#  CC/BE2# |  |  |  |

17 CCD1#

I

| Pin<br>No. | Pin Name | Pin<br>Type |

|------------|----------|-------------|

| 94         | CCD2#    | I           |

| 19         | CCLK0    | 0           |

| 34         | CCLK1    | 0           |

| 53         | CCLK2    | 0           |

| 74         | CCLK3    | 0           |

| 49         | CDEVSEL# | 1           |

| 55         | CFRAME#  | 0           |

| 79         | CGNT0#   | 0           |

| 81         | CGNT1#   | 0           |

| 83         | CGNT2#   | 0           |

| 85         | CGNT3#   | 0           |

| 10         | CLKRUN#  | I/O         |

| 51         | CIRDY#   | 0           |

| 43         | CPAR     | I/O         |

| 46         | CPERR#   | I           |

| 78         | CREQ0#   | 1           |

| 80         | CREQ1#   | 1           |

| 82         | CREQ2#   | 1           |

| 84         | CREQ3#   | 1           |

| 77         | CRST#    | 0           |

| 45         | CSERR#   | 1           |

| 48         | CSTOP#   | I           |

| 50         | CTRDY#   | Ι           |

| 35         | C_VCC    | Р           |

| 54         | C_VCC    | Р           |

| 73         | C_VCC    | Р           |

| 18         | CVS1     | I           |

| 93         | CVS2     | I           |

| 127        | DEVSEL#  | 0           |

| 15         | ENVCC3   | 0           |

| 16         | ENVCC5   | 0           |

| 121        | FRAME#   | I           |

| 7          | GND      | G           |

| 20         | GND      | G           |

| 33         | GND      | G           |

| 44         | GND      | G           |

| 52         | GND      | G           |

| Pin<br>No. | Pin Name         | Pin<br>Type |

|------------|------------------|-------------|

| 64         | GND              | G           |

| 75         | GND              | G           |

| 88         | GND              | G           |

| 101        | GND              | G           |

| 116        | GND              | G           |

| 124        | GND              | G           |

| 136        | GND              | G           |

| 97         | GNT#             |             |

| 110        | IDSEL            | I           |

| 122        | IRDY#            | I           |

| 11         | IRQLATCH         | I/O         |

| 129        | LOCK#            | I           |

| 12         | NC               |             |

| 132        | PAR              | I/O         |

| 125        | PCICLK           |             |

| 86         | PCIRQ0#          |             |

| 87         | PCIRQ1#          | I           |

| 89         | PCIRQ2#          |             |

| 90         | PCIRQ3#          |             |

| 95         | PCIRST#          | I           |

| 130        | PERR#            | 0           |

| 98         | REQ#             | 0           |

| 131        | SERR#            | O/OD        |

| 91         | SIN#             | I           |

| 92         | SOUT#+<br>IRQSER | I/O         |

| 128        | STOP#            | 0           |

| 123        | TRDY#            | 0           |

| 14         | VCC              | Р           |

| 96         | VCC              | Р           |

| 109        | VCC              | Р           |

| 126        | VCC              | Р           |

| 144        | VCC              | Р           |

| 13         | VENID+<br>EXTCLK | I/O         |

912-2000-016 Revision: 2.0

### 3.2 Signal Descriptions

#### 3.2.1 Host Interface PCI Signals

| Signal Name | Pin<br>No.                                                                         | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]    | 99, 100,<br>102:107,<br>111:115,<br>117:119,<br>134, 135,<br>137:142,<br>1:6, 8, 9 | I/O            | Address and Data Lines 31 through 0: This bus carries the address during the address phase and the data during the data phase of a PCI cycle. During the address phase these pins are inputs only and during the data phase they are I/Os.                                                                                                                            |

| C/BE[3:0]#  | 108,<br>120,<br>133, 143                                                           | I              | <b>Bus Command and Byte Enables 3 through 0:</b> These inputs provide the command type information during the address phase and carry the byte enable information during the data phase.                                                                                                                                                                              |

| PAR         | 132                                                                                | I/O            | Parity: This bit carries parity information for both the address and data phases of PCI cycles. During the address or data write phase of a PCI cycle this pin is an input only. During the data read phase it acts as an output only.                                                                                                                                |

| PCICLK      | 125                                                                                | I              | PCI Clock: Provides timing for all transactions on the host PCI bus; normally 33MHz. This same clock can be used for timing the slot interfaces, or can be divided. The slot interfaces can also run from the alternative EXTCLK input.                                                                                                                               |

| VENID#      | 13                                                                                 | 0              | <b>Drive Vendor ID:</b> This pin can be used to enable an external tristate buffer to drive vendor ID bits onto the PCI bus. This feature allows system card designers to drive a unique PCI card ID for identification by software.                                                                                                                                  |

| EXTCLK      |                                                                                    | I              | External Clock: Provides alternative clock source for transactions on the slot interface PCI bus. The frequency can be any value but is usually 20MHz or 25MHz. It should be tied low if not used. This pin is automatically sensed just after reset time to determine whether an external clock frequency is being applied. If not, the function defaults to VENID#. |

| CLKRUN#     | 10                                                                                 | I/O            | Clock Run: Pulled low by any device needing to use the PCI bus. If no devices pull this pin low, the host PCI bus controller is allowed to stop the PCICLK signal. The interrupt logic of the 82C814 uses this signal to request a restart of PCICLK in order to send an interrupt request.                                                                           |

| IRQLATCH    | 11                                                                                 | I/O            | Interrupt Latch: For use on chipsets without IRQ driveback capability, the 82C814 logic can drive this line low to drive ISA IRQ lines using an external latch. This pin is also a strap option, refer to Section 5.3                                                                                                                                                 |

| FRAME#      | 121                                                                                | I              | <b>Cycle Frame:</b> Driven by PCI bus masters to indicate the beginning and duration of an access.                                                                                                                                                                                                                                                                    |

| IRDY#       | 122                                                                                | I              | Initiator Ready: Asserted by the PCI bus master to indicate that it is ready to complete the current data phase of the transaction.                                                                                                                                                                                                                                   |

| TRDY#       | 123                                                                                | 0              | <b>Target Ready:</b> Asserted by the PCI bus target (when the 82C814 is a slave) to indicate that it is ready to complete the current data phase of the transaction. PCI-type devices on the slot interfaces return CTRDY# to the 82C814, which in turn drives TRDY# to the host. The 82C814 logic drives TRDY# directly for 82C814 configuration register accesses.  |

| STOP#       | 128                                                                                | 0              | <b>Stop:</b> Used by the target to request that the master stop the current transaction and retry it later. The 82C814 logic uses this mechanism to back-off from a claimed cycle and generate an SMI through the IRQ driveback cycle, for example.                                                                                                                   |

Page 6 912-2000-016

#### 3.2.1 Host Interface PCI Signals (cont.)

| Signal Name | Pin<br>No. | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                      |  |

|-------------|------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LOCK#       | 129        | I              | <b>Lock</b> : Indicates an atomic operation that may require multiple transactions to complete. The signal can be asserted to the 82C814 by any host bus PCI master, and is driven by the 82C814 logic in response to the current slot interface bus master driving its CBLOCK# signal. |  |

| DEVSEL#     | 127        | 0              | <b>Device Select:</b> Driven by the 82C814 logic when it decodes its address as the target of the current access via either positive or subtractive decoding.                                                                                                                           |  |

| PERR#       | 130        | 0              | <b>Parity Error:</b> All devices use this signal to report data parity errors during any PCI transaction except a Special Cycle.                                                                                                                                                        |  |

| SERR#       | 131        | O/OD           | System Error: The 82C814 logic uses this line to report address parity errors, data parity errors on the Special Cycle command, or any other system error where the result will be catastrophic. This pin has an open drain output.                                                     |  |

| REQ#        | 98         | 0              | <b>Bus Request:</b> The 82C814 logic uses this signal to gain control of the PCI bus. The logic also uses this pin to generate an interrupt driveback request.                                                                                                                          |  |

| GNT#        | 97         | I              | Bus Grant: The system grants the bus to the 82C814 chip using this signal.                                                                                                                                                                                                              |  |

| IDSEL       | 110        | I              | <b>ID Select:</b> This signal is the "chip select" for the controller. This input simply connects to one of the upper address lines to select the controller for configuration cycles.                                                                                                  |  |

| PCIRST#     | 95         | I              | Reset: Main chip reset input.                                                                                                                                                                                                                                                           |  |

#### 3.2.2 Docking Control and Sense Signals

| Signal Name | Pin<br>No. | Signal<br>Type | Signal Description                                                     |  |

|-------------|------------|----------------|------------------------------------------------------------------------|--|

| CCD1#       | 17         | I              | Connection Detect 1 and 2, Voltage Sense 1 and 2: CCD1-2# and CVS1-2   |  |

| CCD2#       | 94         | I              | are used to determine proper dock attachment and to sense its voltage. |  |

| CVS1        | 18         | I              |                                                                        |  |

| CVS2        | 93         | I              |                                                                        |  |

| ENVCC5      | 16         | 0              | 5.0V VCC Enable: Used to turn on power to 5.0V dock.                   |  |

| ENVCC3      | 15         | 0              | 3.3V VCC Enable: Used to turn on power to 3.3V dock.                   |  |

#### 3.2.3 PCI Docking Interface Pins

| Signal Name | Pin<br>No.                                            | Signal<br>Type | Signal Description                                                                                                                                                                                                                                                                                                     |

|-------------|-------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAD[31:0]   | 76, 72:66,<br>63:57, 42,<br>40:36,<br>32:30,<br>28:21 | I/O            | Multiplexed Address and Data Lines 31 through 0: These pins are the multiplexed PCI address and data lines. During the address phase, these pins are outputs for PCI slave cycles and inputs for PCI master cycles. During the data phase, these pins are outputs during PCI write cycles and inputs during PCI reads. |

| CRST#       | 77                                                    | 0              | Reset: Used to reset the docking station PCI bus. This signal defaults to "asserted" until specifically programmed to go high.                                                                                                                                                                                         |

#### 3.2.3 PCI Docking Interface Pins (cont.)

| Signal Name | Pin<br>No.        | Signal<br>Type | Signal Description                                                                                                                                                                                                          |

|-------------|-------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CC/BE[3:0]# | 65, 56, 41,<br>29 | 0              | <b>Bus Command and Byte Enables 3 through 0:</b> These pins are the multiplexed PCI command and byte enable lines. Normally outputs, these pins are inputs during master cycles.                                            |

| CPAR        | 43                | I/O            | <b>Parity:</b> This signal is an input either during PCI slave cycles for address and write data phases or during PCI master cycle for read data phase; otherwise it is an output.                                          |

| CCLK[3:0]   | 74, 53, 34,<br>19 | 0              | Clock 3 through 0: These pins generate individual clocks to each PCI device on the dock.                                                                                                                                    |

| CFRAME#     | 55                | 0              | <b>Cycle Frame:</b> The 82C814 drives this signal to indicate the beginning and duration of an access.                                                                                                                      |

| CIRDY#      | 51                | 0              | <b>Initiator Ready:</b> The 82C814 drives this signal to indicate its ability to complete the current data phase of the transaction.                                                                                        |

| CTRDY#      | 50                | I              | <b>Target Ready:</b> The 82C814 monitors this input from the slot interface slave device to determine when it can complete the cycle. PCI devices on the slots return CTRDY# to the 82C814 which in turn drives host TRDY#. |

| CSTOP#      | 48                | I              | <b>Stop:</b> This signal is used by the target to request the master to stop the current transaction. The 82C814 will back-off the current cycle and retry it later.                                                        |

| CBLOCK#     | 47                | 0              | <b>Bus Lock:</b> The 82C814 uses this signal to indicate an atomic operation that may require multiple transactions to complete.                                                                                            |

| CDEVSEL#    | 49                | I              | <b>Device Select:</b> This signal is normally an input from the slot interface device claiming the cycle. The 82C814 claims the cycle ahead of time on the host side.                                                       |

| CPERR#      | 46                | I              | Parity Error: All slot interface devices use this signal to report data parity errors, during any PCI transaction except a Special Cycle.                                                                                   |

| CSERR#      | 45                | I              | <b>System Error:</b> All slot interface devices use this signal to report address parity errors, data parity errors on the Special Cycle command, or any other system error where the result will be catastrophic.          |

| CREQ[3:0]#  | 84, 82, 80,<br>78 | I              | Bus Master Request Lines 3 through 0: Request/grant signal pairs are provided to accommodate up to four PCI bus masters on the docking station.                                                                             |

| CGNT[3:0]#  | 85, 83, 81,<br>79 | 0              | Bus Grant Lines 3 through 0: Request/grant signal pairs are provided to accommodate up to four PCI bus masters on the docking station.                                                                                      |

#### 3.2.4 Interrupt Interface Pins

| Signal Name | Pin No. | Signal<br>Type | Signal Description                    |  |

|-------------|---------|----------------|---------------------------------------|--|

| PCIRQ0#     | 86      | I              | PCI Interrupt 0: From docking station |  |

| PCIRQ1#     | 87      | I              | PCI Interrupt 1: From docking station |  |

| PCIRQ2#     | 89      | I              | PCI Interrupt 2: From docking station |  |

| PCIRQ3#     | 90      | I              | PCI Interrupt 3: From docking station |  |

Page 8 912-2000-016

#### 3.2.4 Interrupt Interface Pins (cont.)

| Signal Name | Pin No. | Signal<br>Type | Signal Description                                                                 |

|-------------|---------|----------------|------------------------------------------------------------------------------------|

| SOUT#       | 92      | 0              | Serial Out: Intel Serial IRQs output for docking station devices using serial IRQs |

| IRQSER      |         | I/O            | IRQ Serial: Compaq Serial IRQs for docking station devices using serial IRQs       |

| SIN#        | 91      | I              | Serial In: Intel Serial IRQs input for docking station devices using serial IRQs   |

#### 3.2.5 Power, Ground and No Connect Pins

| Signal Name | Pin No.                                                      | Signal<br>Type | Signal Description                               |

|-------------|--------------------------------------------------------------|----------------|--------------------------------------------------|

| GND         | 7, 20, 33,<br>44, 52,<br>64,75, 88,<br>101, 116,<br>124, 136 | G              | Ground Connection                                |

| VCC         | 14, 96,<br>109, 126,<br>144                                  | Р              | Power Connection: For Host Interface             |

| C_VCC       | 35, 54, 73                                                   | Р              | Power Connection: For Docking Interface          |

| NC          | 12                                                           |                | No Connection: This pin should not be connected. |

#### 3.3 Strap-Selected Interface Options

The 82C814 CardBus Controller can be strapped to operate in one of several different modes depending on its implementation in the system.

Strap options are registered at chip reset time. The selection straps are normally 10k ohm resistors engaged full-time. Dur-

ing actual use the resistors consume power only while programming voltage is selected to the cards, at which time the additional current draw would be 5.0V/10k ohm = 0.5mA.

The strapping possibilities are listed in Table 3-4.

#### Table 3-4 Strap Options for 82C814 Configurations

| Strap Selection | Feature             | No Strap                         | Pulled down by 10k ohm<br>Resistor at Reset |

|-----------------|---------------------|----------------------------------|---------------------------------------------|

| IRQLATCH        | Core Voltage Select | 3.3V Core and PCI host interface | 5.0V Core and PCI host interface            |

#### 3.4 **Internal Resistors**

The 82C814 slot interfaces are provided with pull-up and pulldown resistors internal to the chip. The resistors are active at the times indicated in Table 3-5.

Table 3-5 refers to the chip state with no card inserted, a powered-down card inserted, or a docking station attached.

Figure 3-2 shows the functional timing relationships of software power-up and reset commands to the signals output by the power cycle state machine.

Table 3-5 **Internal Keeper Resistor Scheme**

| Signal Group        |                                              | 82C814 Action with<br>No Attachment                  | 82C814 Action after<br>Detecting Docking Station |  |

|---------------------|----------------------------------------------|------------------------------------------------------|--------------------------------------------------|--|

| Dock Detect:        | CCD1-2#                                      | Pull up to core VCC to detect dock insertion/removal | Pull up to core VCC                              |  |

| Address/Data:       | CAD[31:0]<br>CC/BE[3:0]#<br>CPAR             | Pull down                                            | Pull down until interface is powered up          |  |

| Reset:              | CRST#                                        | Driven low                                           | Driven according to PCICFG 3Eh[6]                |  |

| Frame:              | CFRAME#                                      | Pull down                                            | None                                             |  |

| PCI Control/Status: | CIRDY# CTRDY# CDEVSEL# CSTOP# CPERR# CBLOCK# | Pull down                                            | None                                             |  |

| Clock:              | CCLK[3:0]                                    | Pull down                                            | Disable pull-down (clock input is always driven) |  |

| Request:            | CREQ[3:0]#                                   | Pull up to card VCC                                  | None                                             |  |

| Open Drain:         | CSERR#                                       | Pull up to card VCC                                  | None                                             |  |

Figure 3-2 **Power-Up Timing**

Page 10 912-2000-016 Revision: 2.0

#### 4.0 Functional Description

# 4.1 OPTi Docking Station Controller Chipset

The OPTi Docking Station solution is comprised of two devices. The minimum configuration requires one chip, the 82C814 part.

- The 144-pin 82C814 Docking Controller handles the signal transfer for a complete PCI bus, including interrupts and clock generation.

- The 82C825 PCI/ISA Bridge converts PCI signals back into ISA signals. No 82C825 device is required in the system, but one can be added as an option to support ISA peripherals in an attached docking station that connects through the PCI bus interface. The 82C825 is discussed in a separate document.

The multiple interface arrangement offers the maximum in system design flexibility.

#### 4.2 Chipset Compatibility

Because the OPTi Docking Station Controller Chipset is based on a PCI host interface, it can be used with any PCI-

compliant system. DMA may require special software support on non-OPTi systems. Interrupts may require external TTL support.

#### 4.3 Interface Overview

The OPTi 82C814 Docking Station Controller Chipset uses two independent external interfaces. The terms *host interface* and *docking interface* are used throughout this document to describe these interfaces.

- The host interface provides industry standard PCI signals to the host system. The interface also can be programmed to operate in a special (non PCI-standard) mode to allow driveback of interrupt requests from the docking interfaces.

- The **docking interface** duplicates the primary PCI signal set. It is completely isolated from the primary PCI bus.

The interface signal groups used to integrate the OPTi Docking Station Controller Chipset into the standard system are described in the following sections. Figure 4-1 illustrates the interaction of the components of the OPTi Docking Station Controller Chipset.

Figure 4-1 82C814 Organization

912-2000-016 Revision: 2.0

# Preliminary 82C814

The logic implements several functional blocks that interact as indicated. The functional blocks shown in the diagram are briefly described below.

- The 82C814 takes its control, address, and data information from its primary PCI bus, which is usually controlled by the host PCI interface but can also be controlled by a master on the docking interface.

- The 82C814 logic implements a PCI-to-PCI (Card Bus) bridge controlled by PCI Configuration Registers. These configuration registers are accessed from the primary PCI bus. Any bus master, including a master on the docking interface, can program these registers. The PCI Configuration Registers consist of standard CardBus registers at indexes 00h-47h and OPTi 82C814 architecture-specific registers at indexes 48h-FFh. Settings in these registers control host interface operations, select architecture-specific settings such as interrupt routing to the host, and provide PCI status to the host on request. The register set is accessed as PCI Function 0 of the 82C814 device.

- The PCI-to-PCI bridge serves to connect the primary PCI bus to an independent secondary PCI bus. It is this secondary bus that interfaces externally to a docking station. If no dock is attached, software can still access the configuration registers for the bridge.

- The bus arbiter logic takes master requests for bus ownership for the purposes of: 1) Driving back IRQs; 2) Giving PCI master control to one of the secondary PCI buses.

Driving back IRQ status always has highest priority.

- Devices connected to the docking interface can transmit interrupts to the host system through the IRQ driveback logic. Docking station PCI devices can generate INTA#, INTB#, INTC#, and INTD# which the 82C814 logic converts to an interrupt. If the host system chipset does not provide the proper logic for recognition of this driveback cycle, IRQ information can be latched externally to generate discrete signals.

- Clock generation logic is provided to use either the primary PCICLK input for synchronous operation, or an external clock input for asynchronous operation. Four separate output clocks are provided, and can be skew-compensated to adjust for varying board trace lengths.

The logic subsystems of the 82C814 Docking Station Controller are described in detail in the following sections.

#### 4.4 Device Type Detection Logic

The 82C814 logic includes attachment detection logic and a power control state machine to determine what type of dock has been attached to the docking interface.

The power control state machine follows the algorithm provided by the CardBus specification, with a slight modification for docking station detection. Table 4-1 lists the device determination rules. Although the state machine follows the rules for CardBus device detection, only docking stations are considered valid attachments.

Table 4-1 Device Detection (CardBus Rules)

| CCD2#         | CCD1#         | CVS2           | CVS1           | Key  | Card Type            |

|---------------|---------------|----------------|----------------|------|----------------------|

| GND           | Short to CVS1 | Open           | Short to CCD1# | LV   | 3.3V CardBus         |

| Short to CVS2 | GND           | Short to CCD2# | GND            | LV   | 3.3/x.xV CardBus     |

| Short to CVS1 | GND           | GND            | Short to CCD2# | LV   | 3.3/x.x/y.yV CardBus |

| Short to CVS2 | GND           | Short to CCD2# | Open           | LV   | x.xV CardBus         |

| GND           | Short to CVS2 | Short to CCD1# | Open           | LV   | x.x/y.yV CardBus     |

| Short to CVS1 | GND           | Open           | Short to CCD2# | LV   | y.yV CardBus         |

| GND           | Short to CVS1 | GND            | Short to CCD1# |      | 3.3V Docking Station |

| GND           | Short to CVS2 | Short to CCD1# | GND            |      | 5.0V Docking Station |

| GND           | GND           | Open           | Open           | 5.0V | 5.0V PCMCIA          |

| GND           | GND           | Open           | GND            | LV   | 3.3V PCMCIA          |

| GND           | GND           | Open           | GND            | 5.0V | 3.3/5.0V PCMCIA      |

| GND           | GND           | GND            | Open           | LV   | x.xV PCMCIA          |

| GND           | GND           | GND            | GND            | LV   | x.x/3.3V PCMCIA      |