# Am8152A/Am8152B

Video System Controller (VSC)

#### **FINAL**

#### DISTINCTIVE CHARACTERISTICS

- Am8152A with Video Dot Clock Rate up to 80 MHz Am8152B with Video Dot Clock Rate up to 40 MHz

- Four-level current driven (75Ω) differential video output

- Digital Video output

- On-board crystal driven oscillator

- Proportional Spacing Support (2-17 dots)

- 9-bit dot data parallel input, with expansion capability to seventeen bits

- Trailing blanks (0-3 dots)

- Double Width Characters

- Attribute Support: Character Blink, Underline, Overstrike, Reverse, and Highlight

- Buffered and Synchronized Character Clock Outputs

- Background color selection

- Buffered and Synchronized Vertical and Horizontal Sync Outputs

#### **GENERAL DESCRIPTION**

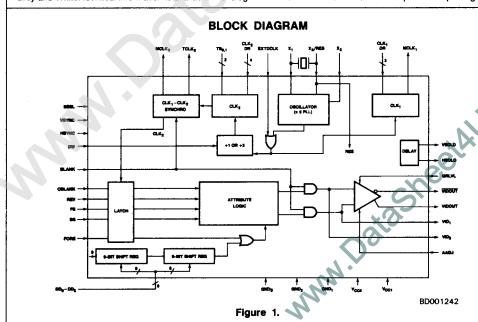

The Am8152A/Am8152B Video System Controller (VSC) provides the interface between a CRT controller and a CRT monitor. The basic chip functions are:

- Support proportional and non-proportional character display

- Correctly synchronize and mix character attributes with video signals

- Output the video information in a four-level analog or digital format

- Serialize parallel video data

The VSC consists of a parallel-to-serial converter which provides a video bit stream to on-chip attribute logic. This logic, under control of the attribute inputs, operates on the bit stream to generate grey scale video. Video outputs from the VSC are of two forms — analog and digital. The digitally encoded outputs implement four video levels: Blank, Black, Grey and White. Identical information is available in analog

form via differential outputs (current driven) into a nominal  $75\Omega$  impedance.

The Am8152A/Am8152B also supports proportional spacing using a bit width programmable character clock. Character ROM pixel information is selectable from two to seventeen pixels per character. Up to three blank pixels can be appended to the character ROM input thereby facilitating right justification of text.

The difference between the Am8152A and the Am8152B is that the Am8152A operates up to 80 MHz, while the Am8152B operates up to 40 MHz. When using the PLL, the lower operating frequency limit is 20 MHz.

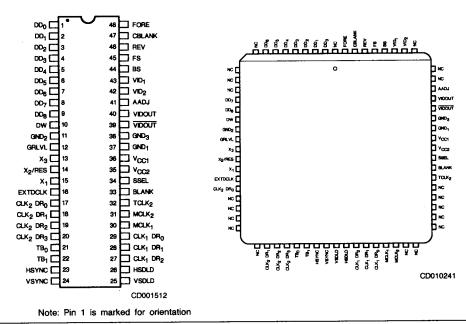

The Am8152A/Am8152B is fabricated using AMD's advanced bipolar process with internal ECL logic. The device is available in conventional 48-pin dual in-line package as well as the surface mounted 68-pin PLCC package.

# CONNECTION DIAGRAM Top View

### METALLIZATION AND PAD LAYOUT

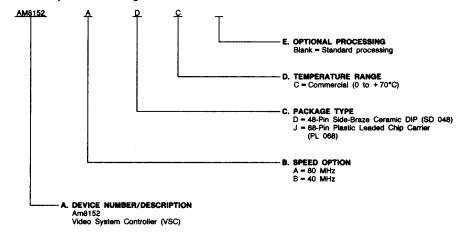

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. Optional Processing

#### **Valid Combinations**

| Valid Combinations |        |  |  |  |  |  |

|--------------------|--------|--|--|--|--|--|

| AM8152A<br>AM8152B | DC, JC |  |  |  |  |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

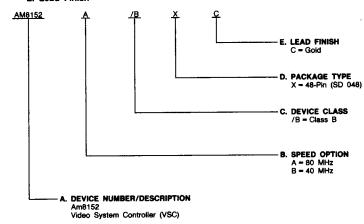

#### ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

#### **Valid Combinations**

| Valid Combinations list configurations planned to be       |

|------------------------------------------------------------|

| supported in volume for this device. Consult the local AMD |

| sales office to confirm availability of specific valid     |

| combinations or to check for newly released valid          |

| combinations.                                              |

#### **Group A Tests**

Group A tests consists of Subgroups: 1, 2, 3, 7, 8, 9, 10, 11

# Valid Combinations AM8152A /BXC AM8152B /BXC

#### PIN DESCRIPTION

#### MCLK<sub>1</sub> Clock<sub>1</sub> (non-TTL compatible) (Output)

MCLK<sub>1</sub> is a system clock. It is intended to drive the Am8052 CLK<sub>1</sub>, MCLK<sub>1</sub> output is nominally a square wave divided down from the internal dot clock frequency according to the CLK<sub>1</sub> DR DR<sub>0-2</sub> (CLK<sub>1</sub> Divide Ratio) inputs.

#### CLK<sub>1</sub> DR Clock<sub>1</sub> Divide Ratio (Input)

CLK<sub>1</sub> DR DR<sub>0-2</sub> are three inputs which control the MCLK<sub>1</sub> divide ratio. The three inputs may be programmed to divide the MCLK<sub>1</sub> signal by two, four, six, . . . ., sixteen. (See Table 1)

#### MCLK<sub>2</sub> Clock<sub>2</sub> (non-TTL compatibe) (Output)

MCLK<sub>2</sub> is the character clock. Its function is to drive the Am8052 CLK<sub>2</sub>. MCLK<sub>2</sub> output is a nominal square wave divided down from the internal dot clock frequency according to the sum of the CLK<sub>2</sub>, DR<sub>0-3</sub> and TB<sub>0-1</sub> inputs.

#### CLK<sub>2</sub> DR Clock<sub>2</sub> Divide Ratio (Input)

CLK<sub>2</sub> DR DR<sub>0-3</sub> are four inputs which control an internal divider to divide the dot clock frequency by a value from two to seventeen. The TB inputs are added. (See Table 2)

#### TCLK<sub>2</sub> TTL Clock<sub>2</sub> (Output)

TCLK2 is a TTL-compatible version of MCLK2.

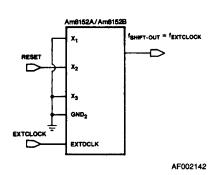

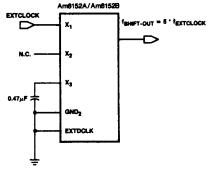

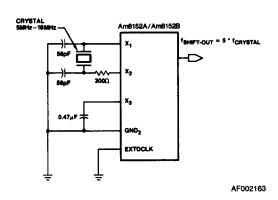

# X<sub>1</sub>, X<sub>2</sub>/RES X<sub>1</sub>, X<sub>2</sub>/RESET (X<sub>2</sub> is non-TTL compatible, reset is TTL compatible) (input)

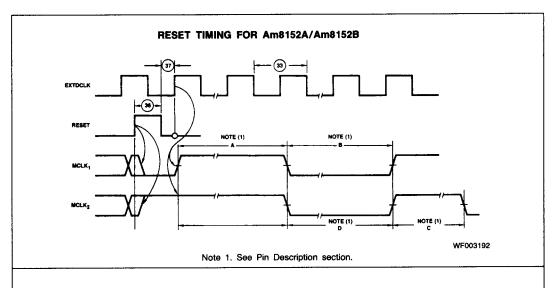

$X_1$ ,  $X_2$ /RES are the external crystal inputs when the on-chip oscillator of the VSC is being used. The external crystal frequency is multiplied by five to produce the on-chip dot clock. If the external dot clock flow-through mode is used, the  $X_1$  should be tied Low and  $X_2$ /RES may be used as a reset input to synchronize multiple VSCs. Note that the reset signal must be synchronous to the external dot clock.

#### X<sub>3</sub> X<sub>3</sub> (non-TTL compatible) (input)

X<sub>3</sub> is used as an input to the on-chip voltage-controlled oscillator. When the on-chip oscillator of VSR is being used, X<sub>3</sub> should be connected to ground by an appropriate capacitor. If the external dot clock flow-through mode is used, X<sub>3</sub> and X<sub>1</sub> should be tied to ground.

#### VSYNC Vertical Sync (Input)

VSYNC is an input that must be synchronous to either MCLK<sub>1</sub> or MCLK<sub>2</sub>, dependent on the SSEL input. If SSEL is High, VSYNC must be synchronous to MCLK<sub>1</sub>.

#### VSDLD Vertical Sync Delayed (Output)

VSDLD is the delayed output of VSYNC, synchronous to MCLK<sub>1</sub> or MCLK<sub>2</sub>, depending on the setting of SSEL.

#### **HSYNC** Horizontal Sync (Input)

HSYNC is an input that must be synchronous to either MCLK<sub>1</sub> or MCLK<sub>2</sub>, dependent upon the SSEL input. If SSEL is Low, HSYNC must be synchronous to MCLK<sub>2</sub>; if SSEL is High, HSYNC must be synchronous to MCLK<sub>1</sub>.

#### **HSDLD** Horizontal Sync Delayed (Output)

HSDLD is the delayed output of HSYNC, synchronous to MCLK<sub>1</sub> or MCLK<sub>2</sub>, depending upon the setting of SSEL.

#### SSEL Sync Select (Input)

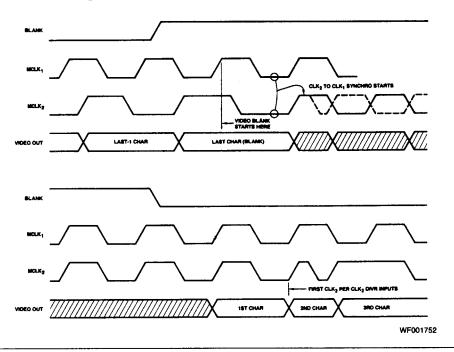

The SSEL line determines if the VSYNC, HSYNC and BLANK are going to be synchronized to the  $MCLK_1$  or  $MCLK_2$  signals. A High on SSEL also will resynchronize  $MCLK_2$  and  $MCLK_1$  during blanking. SSEL is kept LOW for applications which do not involve proportional spacing and HIGH for proportional spacing.

#### **BLANK** Blank (Input)

BLANK is an input normally synchronous to MCLK<sub>1</sub>, although it may be synchronous to MCLK<sub>2</sub> in non-proportional spacing applications. The active pulse width of

BLANK will usually overlap the active portions of HSYNC and VSYNC. While BLANK is active, TCLK2/MCLK2 may be forced to synchronize to the MCLK1 clock. When BLANK goes inactive, the rising edges of MCLK1 and TCLK2/MCLK2 will be synchronized in order to prevent "dot walk" in proportional spacing applications. BLANK active also forces the video output level to "blank" regardless of DD, FORE or other inputs.

#### CBLANK Character Blank (Input)

CBLANK forces video output levels (VID1, VID2, VIDOUT and VIDOUT) to switch to the background color level.

#### FORE Foreground Video (Input)

The FORE video input is "OR'ed" with the dot data output by the parallel-to-serial shift register to switch to the foreground color level (e.g., to implement underlines). FORE is latched with CLK<sub>2</sub> and cannot be used to insert serial data

#### REV Reverse (Input)

The REV input causes the foreground color levels to be transposed with the background color level for the total character period (including any trailing blanks).

#### FS Foreground Shift (Input)

The FS input causes the shift in the video output levels to produce a highlight effect. (See Table 3.)

#### TB<sub>0</sub>, TB<sub>1</sub> Trailing Blanks (Input)

The TB inputs are added to the  $CLK_2$ ,  $DR_{0-3}$  inputs to calculate the total period (in DOT Clock periods) of  $MCLK_2$ . If the total period is greater than 17, then zeroes will be shifted out of the shift register. If the total period is less than 17 dot clocks, the user must insure that the shift register is filled with zeroes. The maximum  $CLK_2$  period is 19 dot clock periods; therefore, the combination of  $CLK_2$  DR = 17 and TB = 3 is not allowed. The first character after video blanking must be four or more pixels, trailing blanks included, or an extra pixel will be outputted.

#### DD<sub>0</sub> - DD<sub>8</sub> Dot Data (Inputs)

The DD inputs accept parallel character dot matrix information for serial conversion for video output. DD<sub>0</sub> is shifted out first.

#### BS Background Select (Input)

The BS input specifies the color level of the background video. This input can be overridden by BLANK active.

VIDOUT, VIDOUT Video Output (non-TTL compatible)

VIDOUT and VIDOUT outputs in a differential mode the

composite blank and video dot levels to a nominal 75Ω load

impedance from switched current sources.

#### VID<sub>1</sub>, VID<sub>2</sub> Video Digital (Output)

VID<sub>1</sub> and VID<sub>2</sub> are digitally encoded outputs of the video out. VID<sub>1</sub> is the least significant bit. Encoding is as follows:

|             | VID <sub>2</sub> (VIDEO) | VID1 (HIGHLIGHT) |

|-------------|--------------------------|------------------|

| Blank Level | 0                        | 0                |

| Black       | 0                        | 1                |

| Grey        | 1                        | 0                |

| White       | 1                        | 1                |

#### GRLVL Grey Level (input)

The GRLVL input adjusts the current level output, via the VIDOUT and VIDOUT outputs, of the grey video level. There are two pre-selected grey levels: for GRLVL HIGH, grey is brighter; for GRLVL LOW, grey is darker. GRLVL is not latched with MCLK, but is sampled on a pixel-by-pixel basis.

#### DW Double Width (Input)

The DW input, when active HIGH, causes the dot clock supplied to the TCLK<sub>2</sub>/MCLK<sub>2</sub> clock divide circuitry and the video shift register to be divided by two. This function is used to facilitate doubling the width of a character cell matrix in the horizontal direction. The trailing blank information is also widened during a double width character.

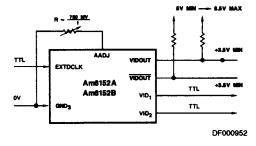

#### EXTDCLK External Dot Clock (Input)

EXTDCLK is an external, TTL-compatible dot clock input for use in multiple Am8152A/Am8152B configurations. This

signal replaces the internal oscillator function. To enable EXTDCLK, both  $X_1$  and  $X_3$  must be grounded.

# AADJ Analog Outputs Current Adjust (non-TTL compatible) (Inputs)

Analog output current adjust is used for setting the analog video output current to 13.3 mA. This is done by connecting AADJ to GND<sub>3</sub> via an applicable 1% resistor.

#### VCC1, VCC2

V<sub>CC</sub> should be connected to +5 V.

#### GND<sub>1</sub>, GND<sub>2</sub>, GND<sub>3</sub>

GND<sub>1-3</sub> should be connected to Ground.

CLK<sub>2</sub> Period

|   | CLK <sub>1</sub> DR |   |   |   |

|---|---------------------|---|---|---|

| 2 | 1                   | 0 | Α | В |

| L | L                   | L | 1 | 1 |

| L | L                   | Н | 2 | 2 |

| L | н                   | L | 3 | 3 |

| L | Н                   | Н | 4 | 4 |

| Н | L                   | L | 5 | 5 |

| Н | L                   | Н | 6 | 6 |

| Н | Н                   | L | 7 | 7 |

| Н | Н                   | н | 8 | 8 |

Table 1

Note: A, B are measured in EXTDCLK periods.

| (CLK <sub>2</sub> DR <sub>0-3</sub> + TB <sub>0-1</sub> ) + 2 | С   | D  |

|---------------------------------------------------------------|-----|----|

| 2                                                             | 1   | 1  |

| 3                                                             | 1 1 | 2  |

| 4                                                             | 2   | 2  |

| 5                                                             | 2   | 3  |

| 6                                                             | 3   | 3  |

| 7                                                             | 3   | 4  |

| 8                                                             | 4   | 4  |

| 9                                                             | 4   | 5  |

| 10                                                            | 5   | 5  |

| 11                                                            | 5   | 6  |

| 12                                                            | 6   | 6  |

| 13                                                            | 6   | 7  |

| 14                                                            | 7   | 7  |

| 15                                                            | 7   | 8  |

| 16                                                            | 8   | 8  |

| 17                                                            | 8   | 9  |

| 18                                                            | 9   | 9  |

| 19                                                            | 9   | 10 |

Note: C and D are measured in EXTDCLK periods.

#### Table 2

$CLK_2$ ,  $DR_{0-3}$  and  $TB_{0-1}$  are a 4-bit and 2-bit binary number respectively. For A, B, C, D refer to the Reset Timing Diagram.

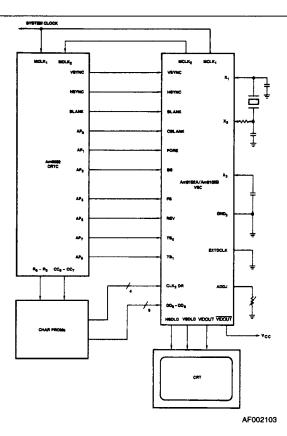

Figure 2. Am8152A/Am8152B Application with Am8052 CRT Controller

#### **FUNCTIONAL DESCRIPTION**

The Am8152A Video System Controller (VSC) supports both black and white and color video applications for CPUs, CRT controllers, and terminals. The essential functions of the VSC are to support proportional and non-proportional character display, to synchronize and mix character attributes with video, and to output the video in a four level analog or 2-bit digital serial format.

#### PARALLEL PIXEL LOADING

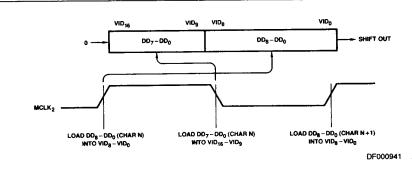

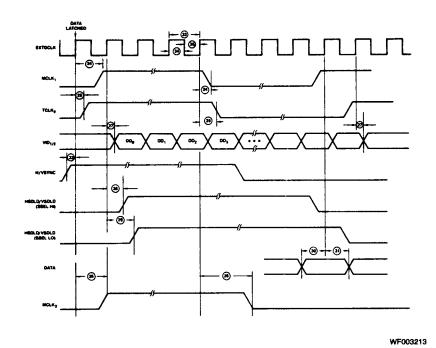

Pixel information that must be serialized for video transmission is loaded into the serial shift register via inputs  $\mathrm{D}_0-\mathrm{D}_8.$  Information is loaded on both edges of the MCLK2 character clock, as shown in Figure 3. The information set up on DD(0:7) prior to the falling edge of MCLK2 is loaded into positions VID9 – VID16. Note that DD8 information is ignored. Information set up on DD(0:8) prior to the rising edge of MCLK2 is loaded into positions VID0 – VID8. Thus, up to 17 bits of pixel information can be loaded into the shift register. Note that if the character width is nine pixels or less the information captured on the falling edge of the MCLK2 is not used.

CLK<sub>2</sub>DR (0:3) and TB (0:1) determine the divide ratio for the character clock. The sum of both values specifies the charac-

ter clock period in dot clocks. During the trailing blank, the VSC shifts out what was loaded into the shift register. Therefore, it is the responsibility of the user to insure that the pixels output during the trailing blank dot period are set to the blank level. If the total is greater than 17, this occurs automatically.

#### **VIDEO OPERATION**

Parallel video data is obtained from the character ROM inputs; bits are shifted out serially and mixed with attribute information such as underline, shifted underline, and any other video sources. Video is internally encoded into one of four levels: White, Grey, Black and Blank. White is the highest analog current level, and Blank is the lowest. This information is then output through two ports. (See Figure 5). One port provides a differential current source output into a 75 $\Omega$  impedance, and the second port outputs encoded TTL video on two pins.

There are two distinct blank inputs to the Am8152A/Am8152B. BLANK is the CRTC's horizontal and vertical retrace period input which causes a blank output level to the display. CBLANK is an attribute input to selectively blank a character cell by forcing the video information for the particular character cell period to switch to the selected background color level. (See Table 3).

Figure 3. Shift Register Loading

#### CRYSTAL SPECIFICATION

The crystal used with the VSC may have the following specifications:

AT cut Series Resonant Shunt Capacitance: 7 pf maximum

#### VIDEO INPUTS/OUTPUTS

Video information may be input in a number of different ways. Table 3 depicts all the combinations of video outputs achievable with each of the various inputs. The background color is determined by a separate pin input allowing either a black or white background. Using the REVERSE VIDEO (REV) input, a grey background can also be selected. The foreground then becomes black or white according to the signal on the foreground SHIFT line. Foreground and video sums can be modified depending on the combination of background, foreground shift, and reverse inputs. The user may apply any of his video inputs to the foreground to obtain a desired effect.

TABLE 3. Am8152A/Am8152B VIDEO ATTRIBUTES

| BS | FS | REV | INPUTS<br>CBLANK (DD (0 : 8) + FORE) | Am8152A/Am8152B VIDEO<br>ATTRIBUTES |

|----|----|-----|--------------------------------------|-------------------------------------|

| 0  | 0  | 0   | 0                                    |                                     |

| 0  | 0  | 0   | 1                                    | "                                   |

| 0  | 0  | 1   | 0                                    | V////                               |

| 0  | 0  | 1   | 1                                    | V.                                  |

| -0 | 1  | 0   | 0                                    |                                     |

| 0  | 1  | 0   | 1                                    |                                     |

| 0  | 1  | 1   | 0                                    |                                     |

| 0  | 1  | 1   | 1                                    | •                                   |

| 1  | 0  | 0   | 0                                    |                                     |

| 1  | 0  | 0   | 1                                    | Ø                                   |

| 1  | 0  | 1   | 0                                    | l <i>\forall \tau</i>               |

| 1  | 0  | 1   | 1                                    | 1 1/6/1                             |

| 1  | 1  | 0   | 0                                    | <del>1""</del>                      |

| 1  | 1  | 0   | 1                                    | •                                   |

| 1  | 1  | 1   | 0                                    |                                     |

| 1  | 1  | 1   | 1                                    | <b>1</b>                            |

|    |    |     |                                      | TB4                                 |

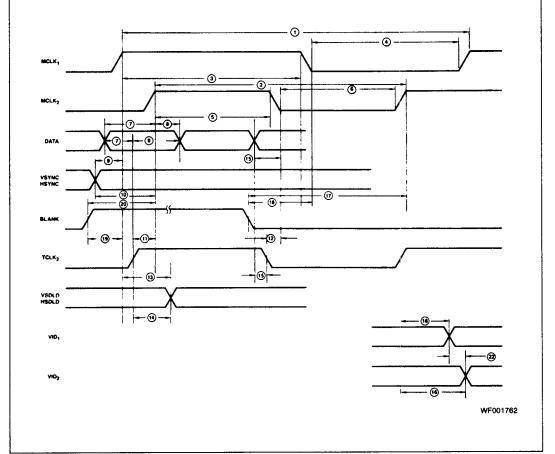

#### SYSTEM TIMING

The CPU clock (MCLK<sub>1</sub>) output is derived from an on-board oscillator by an externally programmable divide ratio. The internal oscillator is capable of operating at a frequency of up to 80 MHz in the Am8152A and 40 MHz in the Am8152B. In crystal oscillator multiplier mode, the crystal should be an AT cut operating in series resonant mode using the fundamental frequency.

The character clock (MCLK<sub>2</sub>) output to the CRTC is frequency modulated according to the chosen number of dots per character cell. The duty cycle of MCLK<sub>2</sub> is 50% (±1 dot clock period) and is derived from the internal dot clock whose divide ratio is set by the width of the character ROM plus the number of trailing blanks. A double width input further modifies MCLK<sub>2</sub> doubling the character width. During an active BLANK input, MCLK<sub>2</sub> is internally resynchronized to MCLK<sub>1</sub> if SSEL is HIGH. This action aligns character cells at the left-end side of the display, thereby eliminating "Dot Walk." The Vertical and Horizontal Sync (VSYNC, HSYNC) inputs from the CRT controller are buffered and delayed by one MCLK<sub>1</sub> or MCLK<sub>2</sub> clock period.

#### DOT CLOCK GENERATION WITH PLL

When using the internal oscillator of the VSC, care should be used in laying out the grounds and supplies for the part in order to minimize the jitter of the PLL. Under optimal conditions this jitter is less than 1 ns. If the jitter does occur it is normally less than 4 ns and can, over the operating range, be reduced to less than 1 ns by varying the duty cycle on X<sub>1</sub>. The following table shows the worst-case jitter observed on typical parts over the operating range and the percentage Dot Clock at various Dot Clock frequencies.

| Dot Clock Frequency<br>(MHz) | Worst Case Jitter<br>Observed (ns) | % Dot Clock |

|------------------------------|------------------------------------|-------------|

| 25                           | 3.9                                | 10          |

| 40                           | 7.4                                | 30          |

| 60                           | 4.4                                | 26          |

| 80                           | 6.7                                | 54          |

#### PROPORTIONAL/VARIABLE SPACING

Proportional spacing is achieved by programming, on a character-by-character basis, a number from two to nineteen dot clock periods per character. The character ROM pixel information is selectable from two to seventeen per character. Up to three trailing blank pixels can be concatenated to the character ROM input, making it easier to provide a straight right margin for right justification of text.

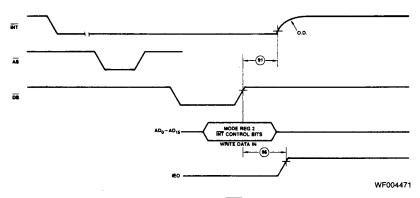

### SWITCHING CHARACTERISTICS (Cont'd.) Am8052 Non-Vectored INT Timing

|     | Parameter Parameter |                                | 4 MHz |      | 6 MHz |      | 8 MHz* |      |         |

|-----|---------------------|--------------------------------|-------|------|-------|------|--------|------|---------|

| No. | Symbol              | Description                    | Min.  | Max. | Min.  | Max. | Min.   | Max. | Units - |

| 91  | to                  | DS 1 to INT (Write) (Note 1)   |       | 100  |       | 90   |        | 80   | ns      |

| 95  | to                  | DS 1 to IEO 1 (Write) (Note 2) |       | 100  |       | 90   |        | 80   | ns      |

Notes: 1. This parameter describes the termination of an interrupt request via a write to the appropriate bit in Mode Register 2:

IUSS \_\_ 1 | IUSV \_\_ 1

IES \_\_ 0 | IEV \_\_ 0

IPS \_\_ 0 | IPV \_\_ 0

2. This is the release of IEO LOW due to the slave mode reset of the IUS bit in Mode Register 2.

\*Commercial products only.

Am8052 Non-Vectored INT Timing

#### **DOTCLOCK GENERATION MODE**

# EXTERNAL DOT CLOCK FLOW THROUGH MODE

### EXTERNAL CLOCK MULTIPLIER MODE

AF002152

### CRYSTAL OSCILLATOR MULTIPLIER MODE

3-49

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                | 65 to +150°C   |

|------------------------------------|----------------|

| Supply Voltage to Ground Potential |                |

| Continuous                         | 0.5 to +7.0V   |

| DC Voltage Applied to Outputs for  |                |

| High Output State                  | 0.5V to +Vcc   |

| DC Input Voltage                   | 0.5 to +5.5V   |

| DC Output Current into Outputs (Se | e Note 2) 30mA |

| DC Input Current                   | 30 to +5.0mA   |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices            |              |

|-----------------------------------|--------------|

| Temperature (T <sub>A</sub> )     | 0 to +70°C   |

| Supply Voltage (V <sub>CC</sub> ) | +5.0 V ±5%   |

| Military (M) Devices              |              |

| Temperature (T <sub>C</sub> )     | 55 to +125°C |

| Supply Voltage (V <sub>CC</sub> ) | +5.0 V ±10%  |

Operating ranges define those limits over which the functionality of the device is guaranteed.

#### Am8152A/Am8152B

DC CHARACTERISTICS over operating range unless otherwise specified; Included in Group A, Subgroup 1, 2, 3 tests unless otherwise noted.

COM'L  $T_A = 0$  to +70°C,  $V_{CC} = 5.0 \text{ V } \pm 5\%$ MIL  $T_C = -55$  to +125°C,  $V_{CC} = 5.0$  V  $\pm 10$ %

| Parameters       | Description                                |                                                  | Test                                                                                                 | Conditions                            | Min   | Max   | Units |

|------------------|--------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-------|-------|

|                  |                                            |                                                  | MCLK <sub>1</sub><br>MCLK <sub>2</sub>                                                               | I <sub>OH</sub> = -0.1 mA             | 4.0   |       | Volts |

| VOH              | Output HIGH Voltage                        | V <sub>CC</sub> = Min                            | TTL                                                                                                  | I <sub>OH</sub> = -1.0 mA MiL         | 2.4   |       | Volts |

|                  |                                            | 1                                                | Output                                                                                               | I <sub>OH</sub> = -2.6 mA COM         | L 2.4 |       | 1013  |

|                  | G 4: 4   GW 1/2   1                        | ).4 . b.di:                                      | MCLK <sub>1</sub><br>MCLK <sub>2</sub>                                                               | I <sub>OL</sub> = 0.1 mA              |       | 0.3   | Volts |

| VOL              | Output LOW Voltage                         | V <sub>CC</sub> = Min                            | TTL<br>Output                                                                                        | I <sub>OL</sub> = 16 mA               |       | 0.5   | Volts |

| ViH              | Input HIGH Level                           | Guaranteed I                                     | Guaranteed Input HIGH Voltage                                                                        |                                       |       |       | Volts |

| VIL              | Input LOW Level                            | Guaranteed I                                     | Guaranteed Input LOW Voltage                                                                         |                                       |       |       | Volts |

| VI               | Input Clamp Voltage                        | V <sub>CC</sub> = Min, I                         | N = -18 mA                                                                                           |                                       |       | -1.2  | Volts |

| I <sub>I</sub> L | Input LOW Current                          | V <sub>CC</sub> = Max                            | V <sub>CC</sub> = Max<br>V <sub>IN</sub> = 0.4 V All Inputs<br>(Except RES, EXTDCLK)<br>RES, EXTDCLK |                                       |       | -0.4  | mA    |

| -1L              |                                            | VIN = 0.4 V                                      |                                                                                                      |                                       |       | -1.0  | mA    |

|                  |                                            | V <sub>CC</sub> = Max                            |                                                                                                      | All Inputs (Except RES)               |       | + 50  | μΑ    |

| liH              | Input HIGH Current                         | VIN = 2.7 V                                      |                                                                                                      | RES                                   |       | + 600 | μА    |

| lı               | Input HIGH Current at<br>Max Input Voltage | V <sub>CC</sub> = Max<br>V <sub>IN</sub> = 5.5 V |                                                                                                      |                                       | +1.0  | mA    |       |

|                  | Output Short Current                       |                                                  |                                                                                                      | MCLK <sub>1</sub> , MCLK <sub>2</sub> | -50   | -250  | mA    |

| Isc              | Current (Notes 1, 2)                       | V <sub>CC</sub> = Max                            |                                                                                                      |                                       | -40   | -130  | mA    |

| łoc              | Power Supply Current                       | V <sub>CC1</sub> = Max<br>V <sub>CC2</sub> = Max | V <sub>CC1</sub> = Max<br>V <sub>CC2</sub> = Max                                                     |                                       |       | 415   | mA    |

#### ANALOG ELECTRICAL CHARACTERISTICS (Notes 2-6)

The following conditions apply unless otherwise specified: COM'L TA = 0 to +70°C VCC = 5.0V ±5% MIL  $T_C = -55$  to +125°C,  $V_{CC} = 5.0 \text{ V } \pm 10\%$

| _                |                  |                  |                                                | VIDOUT                       |                              | VID.                        | OUT                          |

|------------------|------------------|------------------|------------------------------------------------|------------------------------|------------------------------|-----------------------------|------------------------------|

| Grey<br>Level    | VID <sub>2</sub> | VID <sub>1</sub> |                                                | Min (%)                      | Max (%)                      | Min (%)                     | Max (%)                      |

| х<br>о<br>х<br>х | 000              | -00-0            | lWhite<br>IGrey1<br>IGrey2<br>IBlack<br>IBlank | 0<br>37<br>45<br>89.5<br>100 | 0<br>45.5<br>54<br>93<br>100 | 100<br>54.5<br>46<br>7<br>0 | 100<br>63<br>55<br>10.5<br>0 |

#### Notes:

- 1. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

2. The absolute maximum rating for VIDOUT, VIDOUT and AADJ is 22 mA. Shorting VIDOUT, VIDOUT, or AADJ to ground will destroy the

- oevice.

3. Test condition: Normal l<sub>white</sub> for VIDOUT = 13.3 mA.

4. <u>Positive</u> Current flowing into VIDOUT/VIDOUT.

5. VIDOUT output currents normalized to l<sub>white</sub> VIDOUT output output nerents normalized to l<sub>white</sub> VIDOUT and VIDOUT typically will not drift by more than 2% over the operating conditions.

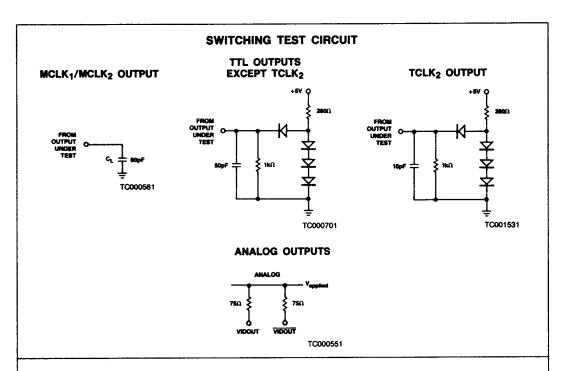

#### Am8152A

SWITCHING CHARACTERISTICS over operating range unless otherwise specified; included in Group A, Subgroup 9, 10, 11 tests unless otherwise noted.

COM'L  $T_A = 0$  to 70°C,  $V_{CC} = 5.0$  V  $\pm 5\%$ MIL  $T_C = -55$  to +125°C,  $V_{CC} = 5.0$  V  $\pm 10\%$

| Number | Description                                                     | Am8152A |                    | Am8152B |                    | ĺ     |

|--------|-----------------------------------------------------------------|---------|--------------------|---------|--------------------|-------|

|        |                                                                 | Min     | Max                | Min     | Max                | Units |

| † 1    | MCLK <sub>1</sub> Period (Note 7)                               | 100     |                    | 165     |                    | ns    |

| † 2    | MCLK <sub>2</sub> Period (Note 7)                               | 70      |                    | 165     |                    | ns    |

| † 3    | MCLK <sub>1</sub> HIGH (See Notes 5, 7) (See Figure 4)          | 38      |                    | 70      |                    | ns    |

| † 4    | MCLK <sub>1</sub> LOW (See Notes 3, 5, 7) (See Figure 4)        | 37.5    |                    | 70      |                    | ns    |

| † 5    | MCLK <sub>2</sub> HIGH (See Notes 6, 7) (See Figure 4)          | 23      |                    | 70      |                    | ns    |

| † 6    | MCLK <sub>2</sub> LOW (See Notes 3, 6, 7) (See Figure 4)        | 20      |                    | 70      |                    | ns    |

| † 7    | Data to MCLK2/TCLK2 RE (See Note 1, 7)                          | 25      |                    | 30      |                    | ns    |

| 8      | MCLK2/TCLK2 to Data Not Valid                                   | 0       |                    | 0       |                    | ns    |

| 9      | VSYNC/HSYNC to MCLK <sub>1</sub> RE Setup (SSEL = HIGH)         | 25      |                    | 30      |                    | ns    |

| † 10   | VSYNC/HSYNC to MCLK <sub>2</sub> RE Setup (SSEL = LOW) (Note 7) | 25      |                    | 30      |                    | ns    |

| 11     | TCLK2 RE to MCLK2 RE Delay                                      |         | 8                  |         | 8                  | ns    |

| 12     | TCLK <sub>2</sub> FE to MCLK <sub>2</sub> FE Delay              |         | 12                 |         | 15                 | ns    |

| 13     | MCLK <sub>1</sub> to VSLD, HSLD (SSEL = HIGH) (See Note 2)      |         | 6+T <sub>D</sub>   |         | 6 + T <sub>D</sub> | ns    |

| 14     | TCLK2 to VSLD, HSLD (SSEL = LOW) (See Note 2)                   |         | 6+T <sub>D</sub>   |         | 6 + T <sub>D</sub> | ns    |

| † 15   | DD(0 - 7) to TCLK <sub>2</sub> FE (See Note 7)                  | 25      |                    | 30      |                    | ns    |

| 16     | TCLK2 RE to VID1 VID2 VAL (See Note 2)                          |         | 6 + T <sub>D</sub> |         | 6 + T <sub>D</sub> | ns    |

| 17     | BLANK FE to MCLK <sub>2</sub> RE Setup (SSEL = LOW)             | 22      |                    | 25      |                    | ns    |

| 18     | BLANK FE to MCLK1 FE Setup (SSEL = HIGH)                        | 20      |                    | 25      |                    | ns    |

| 19     | BLANK RE to MCLK <sub>1</sub> RE Setup (SSEL = HIGH)            | 22      |                    | 25      |                    | ns    |

| 20     | BLANK RE to MCLK2 RE Setup (SSEL = LOW)                         | 22      |                    | 25      |                    | ns    |

| † 22   | VID <sub>1</sub> to VID <sub>2</sub> Skew (See Note 7)          | -5      | +5                 | -7      | +7                 | ns    |

| † 24   | EXTDCLK to MCLK <sub>1</sub> (See Note 7)                       |         | 20                 |         | 25                 | ns    |

| † 25   | EXTDCLK to TCLK2 (See Note 7)                                   |         | 18                 |         | 25                 | ns    |

| 26     | EXTDCLK to MCLK2                                                |         | 23                 |         | 25                 | ns    |

| 27     | EXTDCLK to VID1/VID2                                            |         | 18                 |         | 20                 | ns    |

| 28     | EXTDCLK to HSDLD/VSDLD (SSEL HI)                                |         | 18                 |         | 20                 | ns    |

| 29     | EXTDCLK to HSDLD/VSDLD (SSEL LO)                                |         | 18                 |         | 20                 | ns    |

| † 30   | EXTDCLK to Data in Setup (See Note 7)                           | 12      |                    | 18      |                    | ns    |

| 31     | EXTDCLK to Data Not Valid Hold                                  | 18      |                    | 20      |                    | ns    |

| † 32   | EXTDCLK to H/V SYNC Setup (See Note 7)                          | 14      |                    | 18      |                    | ns    |

| † 33   | EXTDCLK Period (See Note 7)                                     | 12.5    | <u> </u>           | 25      |                    | ns    |

| † 34   | EXTDCLK LOW Cycle (See Note 7)                                  | 5       |                    | 7       |                    | ns    |

| † 35   | EXTDCLK HIGH Cycle (See Note 7)                                 | 5       |                    | 7       |                    | ns    |

| † 36   | Reset Pulse Width (High) (See Note 7)                           | 15      |                    | 20      |                    | ns    |

| † 37   | Reset Low to EXTDCLK Setup                                      | 8.0     |                    | 10      |                    | ns    |

| † 38   | EXTDCLK Period in PLL Mode (See Note 7)                         | 12.5    | 50                 | 25      | 50                 | ns    |

Notes: 1. Data includes CBLANK, FORE, REV, FS, DD0-DD8, TB0, TB1, BS, CLK1DR, CLK2DR, DW.

- 2. First Pixel of character. TD is the dot clock period.

- 3. Max undershoot on these outputs is guaranteed to be -0.3V.

- T<sub>D</sub> is the dot clock period.

Guaranteed to 100ns MCLK<sub>1</sub> cycle time.

- 6. Guaranteed to 70ns MCLK2 cycle time (even divide ratio only).

- 7. These parameters are guaranteed by device characterization or tested using bench top equipment.

<sup>† =</sup> Not included in Group A tests.

## SWITCHING TIMING DIAGRAM - MCLK1/MCLK2

## VSC CLK2 SYNCHRONIZATION (ONLY OCCURS IF SSEL IS HIGH)

Figure 5. Analog Video Outputs and Digital Video Outputs for Am8152A/Am8152B