## PM7390

## S/UNI-MACH48

# MULTI-SERVICE ACCESS DEVICE FOR CHANNELIZED INTERFACES

## **Data Sheet**

Proprietary and Confidential Production Issue 4: December 2001

## Legal Information

## Copyright

© 2001 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, you cannot reproduce any part of this document, in any form, without the express written consent of PMC-Sierra, Inc.

PMC-1990823 (R4)

#### Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### Trademarks

S/UNI is a registered trademark of PMC-Sierra, Inc. SPECTRA-2488, SPECTRA-622, SPECTRA-4x155, TSE, POS-PHY Level 3, and PMC-Sierra are trademark of PMC-Sierra, Inc.

#### Patents

The technology discussed is protected by one or more of the following Patents:

U.S. Patent No. 5,640,398 and 5,835,602 and Canadian Patent No. 2,161,921.

Relevant patent applications and other patents may also exist.

#### **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: +1(604) 415-6000 Fax: +1(604) 415-6200

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com Web Site: <u>http://www.pmc-sierra.com</u>

## **Revision History**

| lssue<br>No. | Issue Date    | Details of Change                                                                                                                                                                                                  |

|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4            | December 2001 | Created data sheet from issue 5 of the eng doc and information provided by Travis Karr.                                                                                                                            |

|              |               | MONx_SYNCV bit polarity reversed as required.                                                                                                                                                                      |

|              |               | Upper and lower bounds on MAXPL specified                                                                                                                                                                          |

|              |               | Clarified CENTER, RSXPAUSE, TSx_REI, TSx_RMODE, FLUSH, SYNCV,<br>SYNCI, LCDC, RDIPRIHI, RDIPRIMID, ICMPDLY, OCMPDLY, DLBEN,<br>IPI, XOFF, INBANDADDR, BIT_ABRTE, DLCV, PTRCDIS, TSIN,<br>POS_SEL, bit descriptions |

|              |               | Fixed power/dc/ac specifications                                                                                                                                                                                   |

|              |               | Added cross reference text to DT and BURST_SIZE descriptions                                                                                                                                                       |

|              |               | Added glitch recovery section                                                                                                                                                                                      |

|              |               | Fixed VDDI pin list                                                                                                                                                                                                |

|              |               | Documented TCFP, RCFP, RXSDQ and TXSDQ counter behaviors.                                                                                                                                                          |

|              |               | Clarified MINPL behavior for RCFP and RTDP                                                                                                                                                                         |

|              |               | Registers DS3+0x30 and DS3+0X40 were removed                                                                                                                                                                       |

|              |               | Update time for all PLCP counters changed to 95 DS3 clock cycles from 67                                                                                                                                           |

|              |               | Indirect read/write behaviors clarified.                                                                                                                                                                           |

|              |               | IJ0J1 pin description modified to name IJ0J1[1] as the master , requiring it not to glitch, and the others to be aligned to it                                                                                     |

|              |               | Clock activity monitor order fixed                                                                                                                                                                                 |

|              |               | Updated actual behavior of TSOC                                                                                                                                                                                    |

|              |               | Clarified SDQ configuration in section 14.13                                                                                                                                                                       |

|              |               | All descriptions of IPAIS now mention that RHPP takes over when it is enabled.                                                                                                                                     |

|              |               | Revealed PERDIV[2:0] bits in RHPP Ind Reg 2, and RHPP Ind reg 7                                                                                                                                                    |

|              |               | Section 14.33 added                                                                                                                                                                                                |

|              |               | Added R8TD Analog Control #3 register.                                                                                                                                                                             |

|              |               | Revealed DLL ERROR, ERRORE, and ERRORI bits.                                                                                                                                                                       |

|              |               | Fixed some erroneous designations of Read and Read/Write register bits.                                                                                                                                            |

|              |               | Removed statement in Operations section that stated SER_PRT_SEL switches on transport frame boundaries.                                                                                                            |

|              |               | Fixed up some typos.                                                                                                                                                                                               |

| 3            | November 2000 | Created document from latest revision of eng. doc.                                                                                                                                                                 |

| 2            | January 2000  | Created document from latest revision of eng. doc.                                                                                                                                                                 |

| 1            | May 1999      | Document created as Preview version.                                                                                                                                                                               |

| -            | •             |                                                                                                                                                                                                                    |

## **Table of Contents**

| Leg  | gal Info | ormation                                             | 2  |

|------|----------|------------------------------------------------------|----|

|      |          | Copyright                                            | 2  |

|      |          | Disclaimer                                           | 2  |

|      |          | Trademarks                                           | 2  |

|      |          | Patents 2                                            |    |

|      |          | Contacting PMC-Sierra                                | 2  |

| Tab  | le of (  | Contents                                             | 5  |

| List | t of Re  | egisters                                             | 11 |

| List | t of Fig | gures                                                | 21 |

| List | t of Ta  | bles                                                 | 23 |

| 1    | Defi     | nitions                                              |    |

| 2    | Feat     | tures                                                | 27 |

|      | 2.1      | General                                              | 27 |

|      | 2.2      | Line Side Interface                                  | 27 |

|      | 2.3      | DS3 Demapper/Receiver                                |    |

|      | 2.4      | DS3 Mapper/Transmitter                               |    |

|      | 2.5      | The Receive ATM Processor                            |    |

|      | 2.6      | The Receive POS Processor                            |    |

|      | 2.7      | The Transmit ATM Processor                           |    |

|      | 2.8      | The Transmit POS Processor                           |    |

| 3    | App      | lications                                            |    |

| 4    | Refe     | erences                                              | 33 |

| 5    | App      | lication Examples                                    |    |

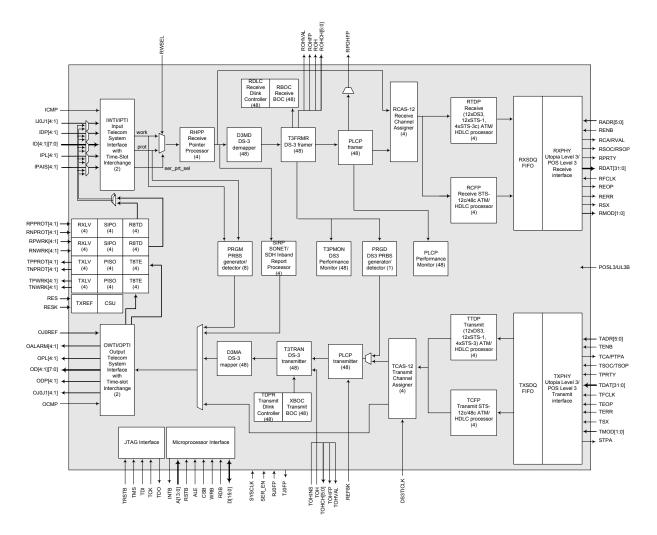

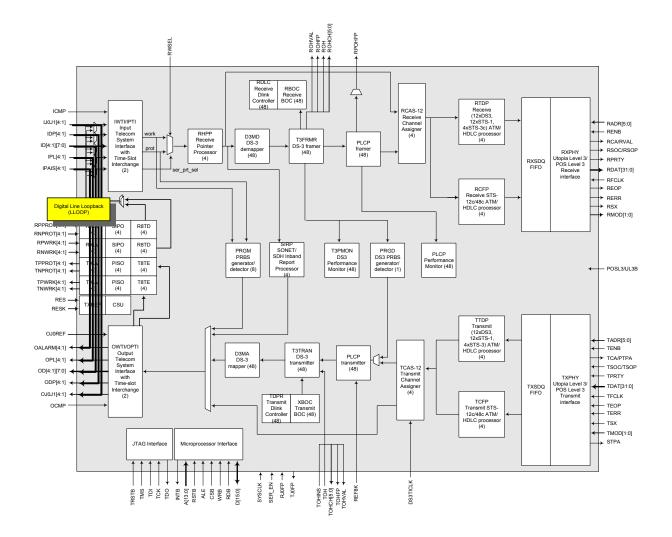

| 6    | Bloc     | k Diagram                                            |    |

| 7    | Loop     | pback Configurations                                 |    |

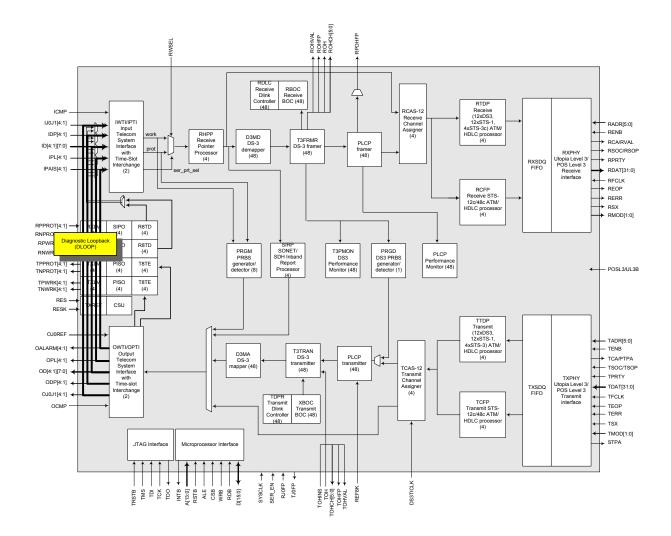

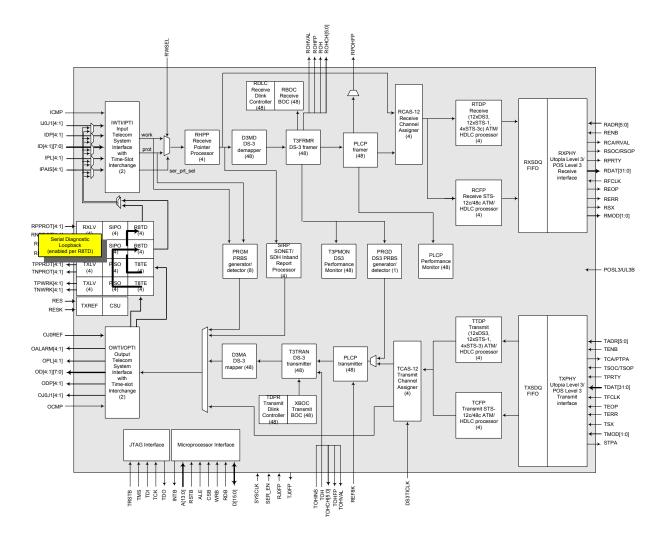

|      | 7.1      | Parallel TelecomBus Diagnostic Loopback              |    |

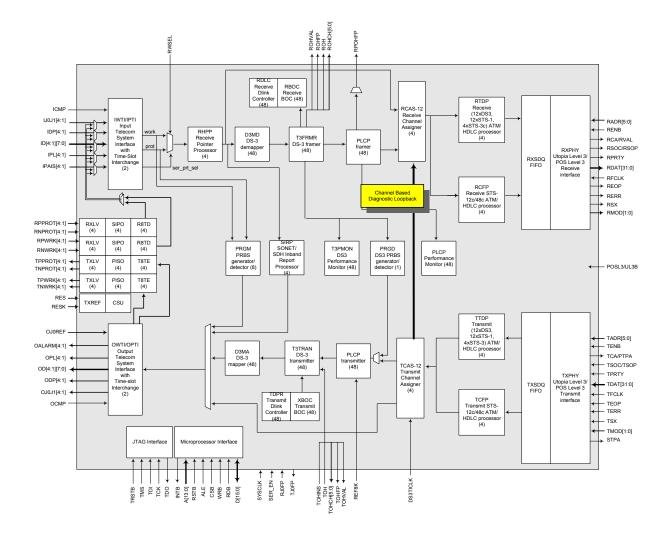

|      | 7.2      | Channel-Based Diagnostic Loopback (Sub STS-48c Only) |    |

|      | 7.3      | Parallel TelecomBus Line Loopback                    |    |

|      | 7.4      | Serial TelecomBus Diagnostic Loopback                |    |

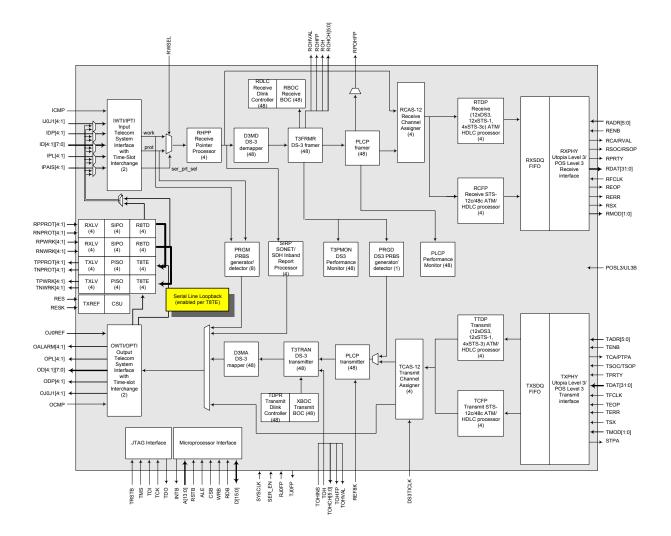

|      | 7.5      | Serial TelecomBus Line Loopback                      | 41 |

| 8    | Des      | cription                                             |    |

|      | 8.1      | Receive Direction                                    |    |

|      | 8.2      | Transmit Direction                                   | 43 |

|    | 8.3   | General                                              | 45 |

|----|-------|------------------------------------------------------|----|

| 9  | Pin D | Diagram                                              | 46 |

| 10 | Pin D | Description                                          | 51 |

| 11 | Func  | tional Description                                   | 77 |

|    | 11.1  | Input Parallel TelecomBus Interface                  | 77 |

|    | 11.2  | Input Serial TelecomBus Interface                    | 77 |

|    | 11.3  | Receive High Order Pointer Processor (RHPP)          | 77 |

|    | 11.4  | DS3 Demapper (D3MD)                                  | 77 |

|    | 11.5  | DS3 Framer (DS3-FRMR)                                | 79 |

|    | 11.6  | DS3 PMON Performance Monitor Accumulator (DS3-PMON)  | 82 |

|    | 11.7  | DS3 Bit-Oriented Code Detector (RBOC)                | 82 |

|    | 11.8  | DS3 Facility Data Link Receiver (RDLC)               | 83 |

|    | 11.9  | SMDS PLCP Layer Receiver (SPLR)                      | 83 |

|    | 11.10 | PLCP Performance Monitor (PLCP PMON)                 | 84 |

|    | 11.11 | DS3 Pseudo-Random Sequence Generator/Detector (PRGD) | 84 |

|    | 11.12 | SONET/SDH PRBS Generator and Monitor (PRGM)          | 85 |

|    | 11.13 | Receive Channel Assigner (RCAS-12)                   | 85 |

|    | 11.14 | Receive Time-sliced Datacom Processor (RTDP)         | 86 |

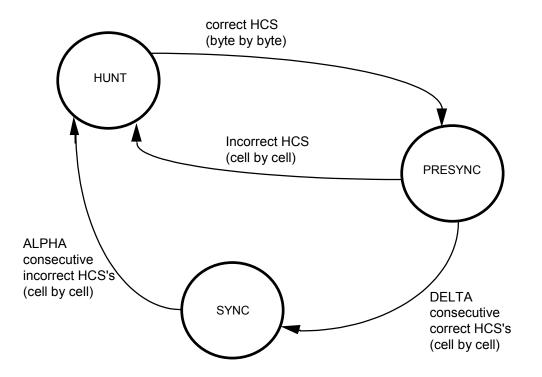

|    |       | 11.14.1 RTDP ATM Processor                           | 86 |

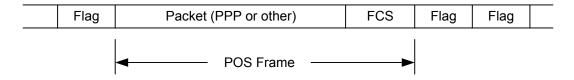

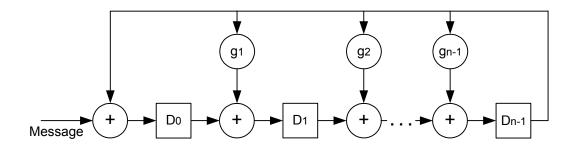

|    |       | 11.14.2 RTDP Packet Processor                        | 88 |

|    | 11.15 | Receive Cell and Frame Processor (RCFP)              | 91 |

|    | 11.16 | PHY-to-Layer Decoupling FIFO (RXSDQ)                 | 91 |

|    | 11.17 | Output Parallel TelecomBus Interface                 | 92 |

|    | 11.18 | Output Serial TelecomBus Interface                   | 92 |

|    | 11.19 | DS3 Mapper (D3MA)                                    | 92 |

|    | 11.20 | DS3 Transmitter (DS3-TRAN)                           | 93 |

|    | 11.21 | DS3 Bit Oriented Code Generator (XBOC)               | 94 |

|    | 11.22 | DS3 Facility Data Link Transmitter (TDPR)            | 94 |

|    | 11.23 | SMDS PLCP Layer Transmitter (SPLT)                   | 95 |

|    | 11.24 | Transmit Channel Assigner (TCAS-12)                  | 96 |

|    | 11.25 | Transmit Time-sliced Datacom Processor (TTDP)        | 96 |

|    |       | 11.25.1 TTDP ATM Processor                           | 96 |

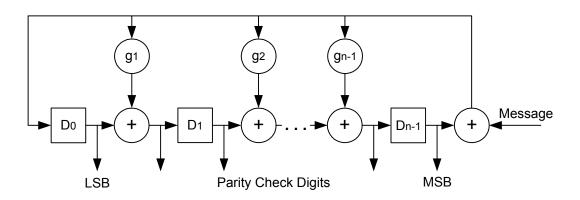

|    |       | 11.25.2 TTDP Packet Processor                        | 97 |

|    | 11.26 | Transmit Cell and Frame Processor (TCFP)             | 99 |

|    | 11.27 | Layer-to-PHY Decoupling FIFO (TXSDQ)                 | 99 |

|    | 11.28 | 3 ATM UTOPIA and Packet Over SONET POS-PHY System Interfaces (RX<br>TXPHY) |     |

|----|-------|----------------------------------------------------------------------------|-----|

|    | 11.29 | SONET/SDH Inband Error Report Processor (SIRP)                             | 102 |

|    | 11.30 | ) Timeslot Interchange (STSI)                                              | 102 |

|    | 11.31 | Receive 8B/10B TelecomBus Decoder (R8TD)                                   | 102 |

|    | 11.32 | 2 Transmit 8B/10B TelecomBus Encoder (T8TE)                                | 103 |

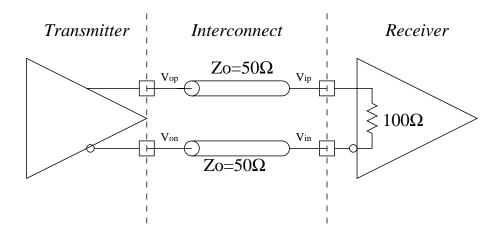

|    | 11.33 | 3 LVDS Overview                                                            | 104 |

|    |       | 11.33.1 LVDS Receiver (RXLV)                                               | 105 |

|    |       | 11.33.2 LVDS Transmitter (TXLV)                                            | 105 |

|    |       | 11.33.3 LVDS Transmit Reference (TXREF)                                    | 105 |

|    |       | 11.33.4 Data Recovery Unit (DRU)                                           | 106 |

|    |       | 11.33.5 Parallel to Serial Converter (PISO)                                | 106 |

|    |       | 11.33.6 Clock Synthesis Unit (CSU)                                         | 106 |

|    | 11.34 | I JTAG Test Access Port                                                    | 106 |

|    | 11.35 | 5 Microprocessor Interface                                                 | 106 |

| 12 | Norr  | nal Mode Register Description                                              | 120 |

|    | 12.1  | RCFP Register Summary                                                      | 249 |

|    | 12.2  | TCFP Register Summary                                                      | 271 |

|    | 12.3  | RTDP Register Summary                                                      | 287 |

|    | 12.4  | TTDP Register Summary                                                      | 314 |

|    | 12.5  | RCAS12 Register Summary                                                    | 335 |

|    | 12.6  | TCAS12 Register Summary                                                    | 340 |

|    | 12.7  | DS3 Register Summary                                                       | 346 |

|    | 12.8  | SIRP Register Summary                                                      | 422 |

|    | 12.9  | PRGM Register Summary                                                      | 443 |

|    | 12.10 | RHPP Register Summary                                                      | 473 |

|    | 12.11 | STSI (IWTI, IPTI, OWTI, OPTI) Register Summary                             | 495 |

|    | 12.12 | 2 R8TD Register Summary                                                    | 504 |

|    | 12.13 | 3 T8TE Register Summary                                                    | 516 |

|    | 12.14 | DLL Register Summary                                                       | 526 |

|    | 12.15 | 5 Dropped Cell/Packet Counter Summary                                      | 535 |

| 13 | Test  | Features Description                                                       | 543 |

|    | 13.1  | Master Test and Test Configuration Registers                               | 543 |

|    | 13.2  | JTAG Test Port                                                             | 549 |

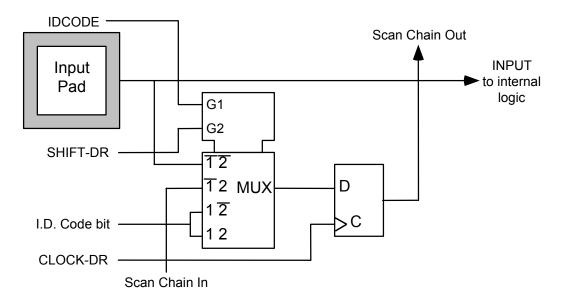

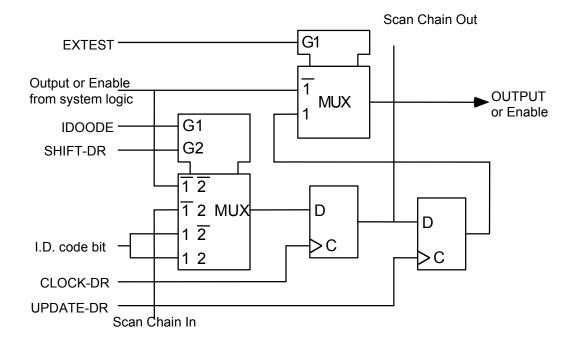

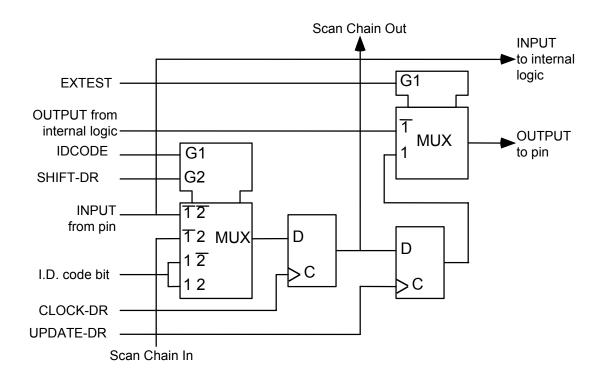

|    |       | 13.2.1 Boundary Scan Cells                                                 | 555 |

| 14 | Oper  | ration   |                                                                       | 558         |

|----|-------|----------|-----------------------------------------------------------------------|-------------|

|    | 14.1  | S/UNI-   | MACH48 Conceptual Regions                                             | 558         |

|    | 14.2  | Serial 7 | FelecomBus (LVDS) Operation                                           | 559         |

|    |       | 14.2.1   | Character Alignment                                                   | 559         |

|    |       | 14.2.2   | Frame Alignment                                                       | 560         |

|    |       | 14.2.3   | Character Decode                                                      | 560         |

|    |       | 14.2.4   | Character Encode                                                      | 561         |

|    | 14.3  | Telecor  | mBus MST and HPT Modes                                                | 561         |

|    | 14.4  | DS3 PI   | LCP Frame Format                                                      | 562         |

|    | 14.5  | DS3 Fr   | ame Format                                                            | 565         |

|    | 14.6  | SONE     | Г/SDH Frame Mappings                                                  | 566         |

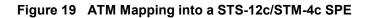

|    |       | 14.6.1   | ATM Mapping                                                           | 566         |

|    |       | 14.6.2   | Packet over SONET Mapping                                             | 567         |

|    |       | 14.6.3   | Transport and Path Overhead Bytes Used by the S/UNI-MACH48            | 567         |

|    | 14.7  | ATM C    | ell Data Structure                                                    | 569         |

|    | 14.8  | POS/H    | DLC Data Structure                                                    | 569         |

|    |       | 14.8.1   | Limitation When Using Externally Generated FCS in STS-48c Mod         | le570       |

|    |       | 14.8.2   | Limitations on Small Packets                                          | 570         |

|    | 14.9  | Setting  | up Timeslot Assignments in the IWTI, IPTI, OWTI, and OPTI             | 571         |

|    |       | 14.9.1   | Standard Line-Side Timeslot Map                                       | 571         |

|    |       | 14.9.2   | Required System-Side Timeslot Map for Sub-STS-48c/STM-16c D 571       | ata Streams |

|    |       | 14.9.3   | Required System-Side Timeslot Map for STS-48c/STM-16c Data S<br>572   | Streams     |

|    |       | 14.9.4   | Custom Timeslot Mappings and Movement of Timeslots Associated Channel |             |

|    |       | 14.9.5   | Active and Standby Pages in the STSI Blocks                           | 574         |

|    | 14.10 | Using F  | RWSEL and SER_PRT_SEL                                                 | 574         |

|    | 14.11 | Setting  | up Channels for Different Link Rates                                  | 575         |

|    |       | 14.11.1  | Example Set-up:                                                       | 576         |

|    | 14.12 | Dynam    | ically Reprovisioning Channels to Different Rates                     | 578         |

|    | 14.13 | RXSDO    | Q and TXSDQ FIFO Size Configuration                                   | 579         |

|    | 14.14 | RXSDO    | Q and TXSDQ Dynamic Reconfiguration                                   | 581         |

|    | 14.15 | TXSDO    | Q Buffer Available Operation                                          | 582         |

|    | 14.16 | RXSDO    | Q and TXSDQ Data Available and Burst-Size Operation                   | 583         |

|    | 14.17 | RXPH     | Y POS-PHY L3 Servicing                                                | 584         |

| 14.17.1 RXPHY POS-PHY L3 Servicing Algorithm                                      | 584 |

|-----------------------------------------------------------------------------------|-----|

| 14.18 Setting ATM Mode of Operation over Utopia L3 or POS-PHY L3                  | 586 |

| 14.18.1 Transmit UL3 Interface Misalignment Recovery                              | 587 |

| 14.18.2 Receive UL3 Interface Misalignment Recovery                               | 587 |

| 14.19 Setting Packet Mode of Operation Over POS-PHY L3                            | 587 |

| 14.20 Setting Transparent Mode of Operation Over POS-PHY L3                       | 588 |

| 14.21 SIRP Configuration Options                                                  | 588 |

| 14.21.1 SIRP Concatenated Channel Configuration                                   | 588 |

| 14.21.2 SIRP Modes of Operation                                                   | 590 |

| 14.22 PRBS Generator and Monitor (PRGM)                                           | 590 |

| 14.22.1 Mixed Payload (STS-12c, STS-3c, and STS-1)                                | 591 |

| 14.22.2 Synchronization                                                           | 591 |

| 14.22.3 Master/Slave Configuration for STS-48c/STM-16c Payloads                   | 592 |

| 14.22.4 Special Note for Use of PRGM in STS-48c/STM-16c mode (TX48C<br>RX48C = 1) |     |

| 14.22.5 Error Detection and Accumulation                                          | 593 |

| 14.22.6 B1/E1 Overwrite and Detection                                             | 593 |

| 14.23 DS3 PRBS and Repetitive Pattern Generation with PRGD                        | 594 |

| 14.23.1 Generating and Detecting Repetitive Patterns                              | 594 |

| 14.23.2 Common Test Patterns                                                      | 595 |

| 14.24 Interrupt Service Routine                                                   | 596 |

| 14.25 Accessing Indirect Registers                                                | 597 |

| 14.26 Using the Performance Monitoring Features                                   | 598 |

| 14.27 Using the Internal DS3 FDL Transmitter                                      | 598 |

| 14.28 Using the Internal DS3 FDL Receiver                                         | 601 |

| 14.29 Transmitting Bit Oriented Codes                                             | 605 |

| 14.30 Loopback Operation                                                          | 605 |

| 14.31 JTAG Support                                                                | 606 |

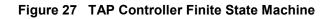

| 14.31.1 TAP Controller                                                            | 608 |

| 14.31.2 States                                                                    | 610 |

| 14.31.3 Boundary Scan Instructions                                                | 611 |

| 14.32 Power Up Sequence                                                           | 611 |

| 14.33 Reset Sequence                                                              | 612 |

| 14.34 Clock Glitch Recovery                                                       | 612 |

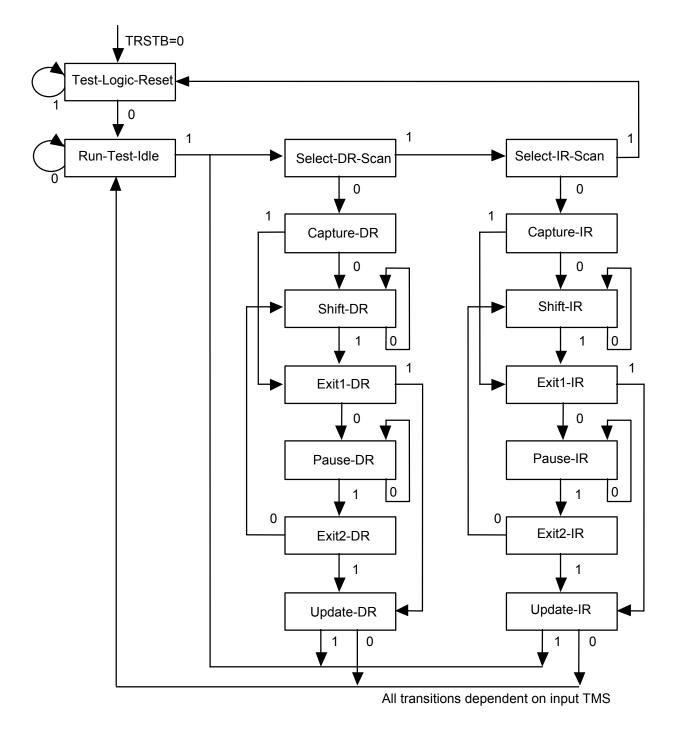

| 14.35 LVDS Analog Power Filtering                                                 | 612 |

| 15             | Fund                                                                 | tional T                                                                                                | ïming                                                                                                                                                                             | 614                                                                       |

|----------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                | 15.1                                                                 | DS3 O                                                                                                   | verhead Extraction                                                                                                                                                                | 614                                                                       |

|                | 15.2                                                                 | DS3 O                                                                                                   | verhead Insertion                                                                                                                                                                 | 615                                                                       |

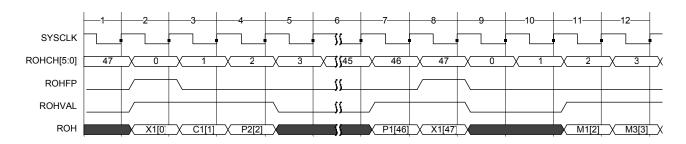

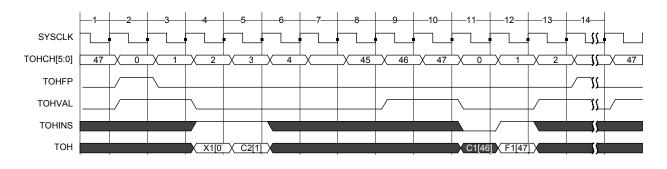

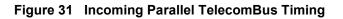

|                | 15.3                                                                 | Incomi                                                                                                  | ng Parallel TelecomBus                                                                                                                                                            | 616                                                                       |

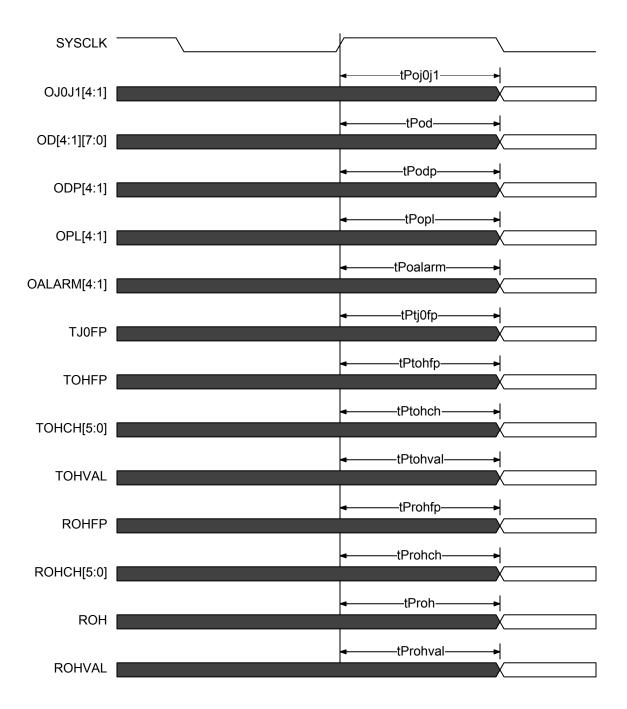

|                | 15.4                                                                 | Outgoi                                                                                                  | ng Parallel TelecomBus                                                                                                                                                            | 618                                                                       |

|                | 15.5                                                                 | Incomi                                                                                                  | ng Serial TelecomBus                                                                                                                                                              | 620                                                                       |

|                | 15.6                                                                 | Outgoi                                                                                                  | ng Serial TelecomBus                                                                                                                                                              | 621                                                                       |

|                | 15.7                                                                 | ATM U                                                                                                   | TOPIA Level 3 System Interface                                                                                                                                                    | 621                                                                       |

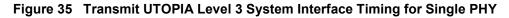

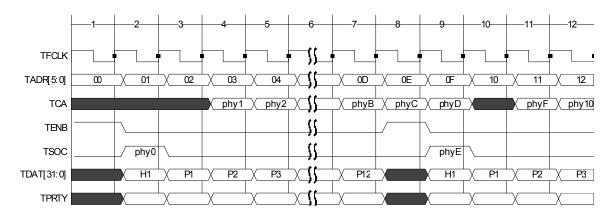

|                |                                                                      | 15.7.1                                                                                                  | Transmit UL3 Interface                                                                                                                                                            | 621                                                                       |

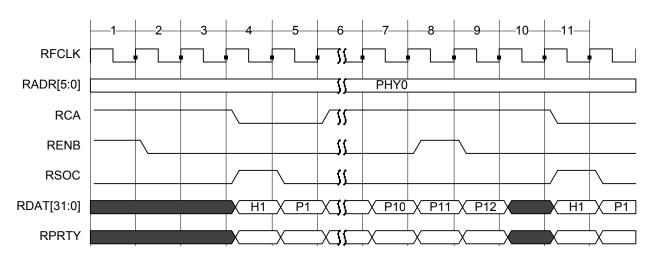

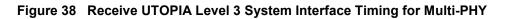

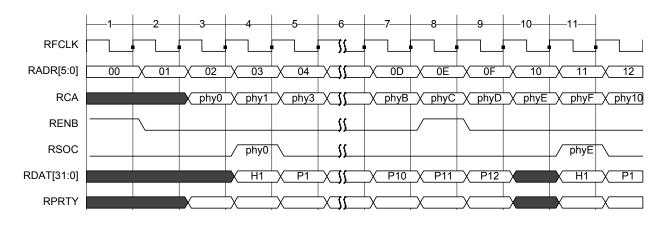

|                |                                                                      | 15.7.2                                                                                                  | Receive UL3 Interface                                                                                                                                                             | 623                                                                       |

|                | 15.8                                                                 | Packet                                                                                                  | over SONET (POS) Level 3 System Interface                                                                                                                                         | 624                                                                       |

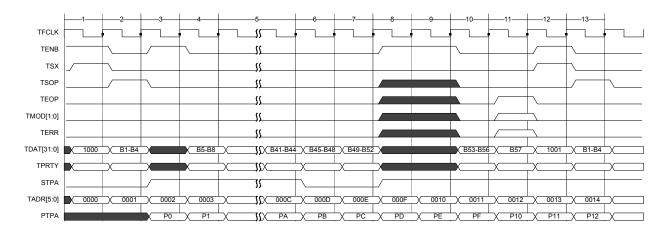

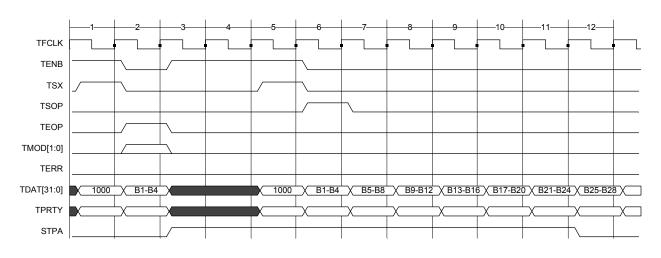

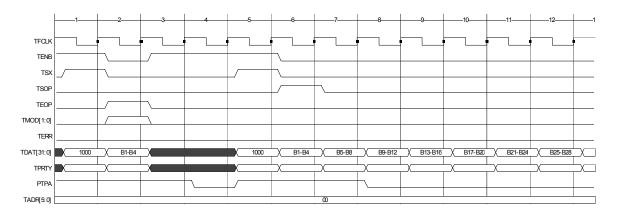

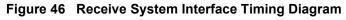

|                |                                                                      | 15.8.1                                                                                                  | Transmit PL3 Interface                                                                                                                                                            | 625                                                                       |

|                |                                                                      | 15.8.2                                                                                                  | Transmit PL3 STPA and PTPA Behavior                                                                                                                                               | 626                                                                       |

|                |                                                                      |                                                                                                         |                                                                                                                                                                                   |                                                                           |

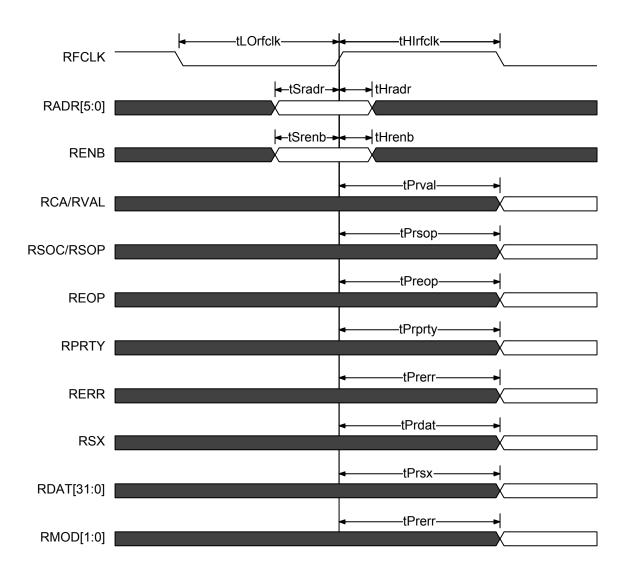

|                |                                                                      | 15.8.3                                                                                                  | Receive PL3 Interface                                                                                                                                                             | 630                                                                       |

| 16             | Abso                                                                 |                                                                                                         | Receive PL3 Interface                                                                                                                                                             |                                                                           |

| 16<br>17       |                                                                      | olute Ma                                                                                                |                                                                                                                                                                                   | 632                                                                       |

| -              | D.C.                                                                 | olute Ma<br>Charac                                                                                      | ximum Ratings                                                                                                                                                                     | 632<br>633                                                                |

| 17             | D.C.<br>Micr                                                         | olute Ma<br>Charac<br>oproces                                                                           | teristics                                                                                                                                                                         | 632<br>633<br>635                                                         |

| 17<br>18       | D.C.<br>Micro<br>A.C.                                                | olute Ma<br>Charac<br>oproces<br>Timing                                                                 | eximum Ratings<br>teristics<br>sor Interface Timing Characteristics                                                                                                               | 632<br>633<br>635<br>638                                                  |

| 17<br>18       | D.C.<br>Micro<br>A.C.<br>19.1                                        | olute Ma<br>Charac<br>oproces<br>Timing<br>System                                                       | iximum Ratings<br>teristics<br>sor Interface Timing Characteristics<br>Characteristics                                                                                            | 632<br>633<br>635<br>638<br>638                                           |

| 17<br>18       | D.C.<br>Micro<br>A.C.<br>19.1<br>19.2                                | olute Ma<br>Charac<br>oproces<br>Timing<br>System<br>System                                             | iximum Ratings<br>teristics<br>sor Interface Timing Characteristics<br>Characteristics<br>n Miscellaneous Timing                                                                  | 632<br>633<br>635<br>638<br>638<br>639                                    |

| 17<br>18       | D.C.<br>Micro<br>A.C.<br>19.1<br>19.2<br>19.3                        | Dute Ma<br>Charac<br>oproces<br>Timing<br>System<br>System<br>Line In                                   | eximum Ratings<br>teristics<br>sor Interface Timing Characteristics<br>Characteristics<br>n Miscellaneous Timing<br>n Interface Timing                                            | 632<br>633<br>635<br>638<br>638<br>639<br>643                             |

| 17<br>18       | D.C.<br>Micro<br>A.C.<br>19.1<br>19.2<br>19.3<br>19.4                | Dute Ma<br>Charac<br>oproces<br>Timing<br>System<br>System<br>Line In<br>Serial                         | eximum Ratings<br>eteristics<br>sor Interface Timing Characteristics<br>Characteristics<br>n Miscellaneous Timing<br>n Interface Timing<br>terface Timing                         | 632<br>633<br>635<br>638<br>638<br>639<br>643<br>647                      |

| 17<br>18       | D.C.<br>Micro<br>A.C.<br>19.1<br>19.2<br>19.3<br>19.4<br>19.5        | olute Ma<br>Charac<br>oproces<br>Timing<br>System<br>System<br>Line Ini<br>Serial T                     | eximum Ratings<br>eteristics<br>sor Interface Timing Characteristics<br>Characteristics<br>n Miscellaneous Timing<br>n Interface Timing<br>terface Timing<br>TelecomBus Interface | 632<br>633<br>635<br>638<br>638<br>639<br>643<br>647<br>648               |

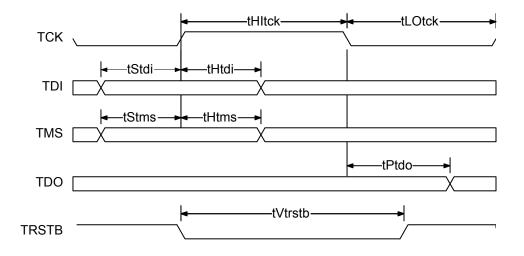

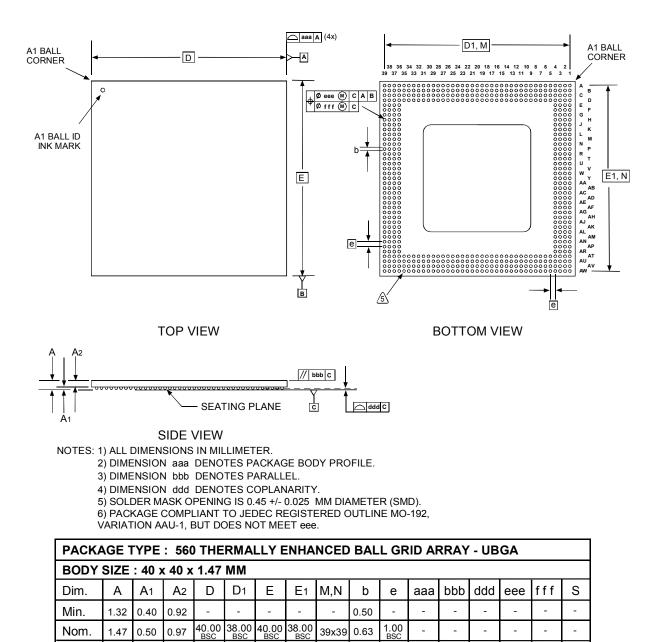

| 17<br>18<br>19 | D.C.<br>Micro<br>A.C.<br>19.1<br>19.2<br>19.3<br>19.4<br>19.5<br>Pow | olute Ma<br>Charac<br>oproces<br>Timing<br>System<br>System<br>Line In<br>Serial T<br>JTAG T<br>er Requ | eximum Ratings                                                                                                                                                                    | 632<br>633<br>635<br>638<br>638<br>639<br>643<br>643<br>647<br>648<br>650 |

## **List of Registers**

| Register 0000H: S/UNI-MACH48 Global Performance Monitor Update                                      | 121 |

|-----------------------------------------------------------------------------------------------------|-----|

| Register 0001H: S/UNI-MACH48 Master Reset, Configuration, and Global Digital                        |     |

| Loopback                                                                                            |     |

| Register 0002H: S/UNI-MACH48 Receive Timeslot Configuration #1                                      |     |

| Register 0003H: S/UNI-MACH48 Receive Timeslot Configuration #2                                      | 128 |

| Register 0004H: S/UNI-MACH48 Receive Timeslot Configuration #3                                      | 129 |

| Register 0005H: S/UNI-MACH48 Receive Timeslot Configuration #4                                      | 130 |

| Register 0006H: S/UNI-MACH48 Receive Timeslot Configuration #5                                      | 131 |

| Register 0007H: S/UNI-MACH48 Receive Timeslot Configuration #6                                      | 132 |

| Register 0008H: S/UNI-MACH48 Transmit Timeslot Configuration #1                                     | 133 |

| Register 0009H: S/UNI-MACH48 Transmit Timeslot Configuration #2                                     | 135 |

| Register 000AH: S/UNI-MACH48 Receive Timeslot Configuration #3                                      | 136 |

| Register 000BH: S/UNI-MACH48 Transmit Timeslot Configuration #4                                     | 137 |

| Register 000CH: S/UNI-MACH48 Transmit Timeslot Configuration #5                                     | 138 |

| Register 000DH: S/UNI-MACH48 Receive Timeslot Configuration #6                                      | 139 |

| Register 000EH: S/UNI-MACH48 DS3 PRBS Assignment                                                    | 140 |

| Register 000FH: S/UNI-MACH48 PLCP Reference and Clock Activity                                      | 141 |

| Register 0010H: S/UNI-MACH48 DS3 Automatic Alarm Reporting, DS3 LOF<br>Selection, TelecomBus Parity | 143 |

| Register 0011H: Receive Serial TelecomBus Synchronization Delay                                     | 147 |

| Register 0012H: Miscellaneous                                                                       | 149 |

| Register 0013H: Transmit TelecomBus Synchronization Delay                                           | 151 |

| Register 0014H: Software General Purpose Register                                                   | 153 |

| Register 0015H: S/UNI-MACH48 Interrupt Block Identifier                                             | 154 |

| Register 0016H: S/UNI-MACH48 IPTI, IWTI, RXPHY, RXSDQ, RTDPs, and RCFPs Interrupt Indication        | 158 |

| Register 0017H: S/UNI-MACH48 OPTI, OWTI, TXPHY, TXSDQ, TTDPs, and TCFPs Interrupt Indication        | 160 |

| Register 0018H: S/UNI-MACH48 SPLR #0-15 Interrupt Indication                                        | 162 |

| Register 0019H: S/UNI-MACH48 SPLR #16-31 Interrupt Indication                                       | 163 |

| Register 001AH: S/UNI-MACH48 SPLR #32-47 Interrupt Indication                                       | 164 |

| Register 001BH: S/UNI-MACH48 DS3 PMON #0-15 Interrupt Indication                                    | 165 |

| Register 001CH: S/UNI-MACH48 DS3 PMON #16-31 Interrupt Indication                                   | 166 |

| Register 001DH: S/UNI-MACH48 DS3 PMON #32-47 Interrupt Indication                                   | 167 |

| Register 001EH: S/UNI-MACH48 D3MA #0-15 Interrupt Indication 168        | 8 |

|-------------------------------------------------------------------------|---|

| Register 001FH: S/UNI-MACH48 D3MA #16-31 Interrupt Indication 169       | 9 |

| Register 0020H: S/UNI-MACH48 D3MA #32-47 Interrupt Indication 170       | C |

| Register 0021H: S/UNI-MACH48 D3MD #0-15 Interrupt Indication 177        | 1 |

| Register 0022H: S/UNI-MACH48 D3MD #16-31 Interrupt Indication 172       | 2 |

| Register 0023H: S/UNI-MACH48 D3MD #32-47 Interrupt Indication 173       | 3 |

| Register 0024H: S/UNI-MACH48 XBOC #0-15 Interrupt Indication 174        | 4 |

| Register 0025H: S/UNI-MACH48 XBOC #16-31 Interrupt Indication 175       | 5 |

| Register 0026H: S/UNI-MACH48 XBOC #32-47 Interrupt Indication 176       | 6 |

| Register 0027H: S/UNI-MACH48 RBOC #0-15 Interrupt Indication 177        | 7 |

| Register 0028H: S/UNI-MACH48 RBOC #16-31 Interrupt Indication           | 8 |

| Register 0029H: S/UNI-MACH48 RBOC #31-47 Interrupt Indication           | 9 |

| Register 002AH: S/UNI-MACH48 TDPR #0-15 Interrupt Indication            | D |

| Register 002BH: S/UNI-MACH48 TDPR #16-31 Interrupt Indication           | 1 |

| Register 002CH: S/UNI-MACH48 TDPR #32-47 Interrupt Indication           | 2 |

| Register 002DH: S/UNI-MACH48 RDLC #0-15 Interrupt Indication            | 3 |

| Register 002EH: S/UNI-MACH48 RDLC #16-31 Interrupt Indication 184       | 4 |

| Register 002FH: S/UNI-MACH48 RDLC #32-47 Interrupt Indication 185       | 5 |

| Register 0030H: S/UNI-MACH48 DS3FRMR #0-15 Interrupt Indication         | 6 |

| Register 0031H: S/UNI-MACH48 DS3FRMR #16-31 Interrupt Indication        | 7 |

| Register 0032H: S/UNI-MACH48 DS3FRMR #32-47 Interrupt Indication        | В |

| Register 0033H: S/UNI-MACH48 DS3 LOF #0-15 Interrupt Indication         | 9 |

| Register 0034H: S/UNI-MACH48 DS3 LOF #16-31 Interrupt Indication 190    | D |

| Register 0035H: S/UNI-MACH48 DS3 LOF #32-47 Interrupt Indication 197    | 1 |

| Register 0036H: S/UNI-MACH48 PLCP PMON #0-15 Interrupt Indication 192   | 2 |

| Register 0037H: S/UNI-MACH48 PLCP PMON #16-31 Interrupt Indication 193  | 3 |

| Register 0038H: S/UNI-MACH48 PLCP PMON #32-47 Interrupt Indication 194  | 4 |

| Register 0039H: S/UNI-MACH48 PRBS and RHPP Interrupt Indication         | 5 |

| Register 003AH: S/UNI-MACH48 8B/10B, CSTR, and DLL Interrupt Indication | 6 |

| Register 003BH: S/UNI-MACH48 DS3 #0-15 LOF Status                       | В |

| Register 003CH: S/UNI-MACH48 DS3 #16-31 LOF Status 199                  | 9 |

| Register 003DH: S/UNI-MACH48 DS3 #32-47 LOF Status                      | 0 |

| Register 003EH: S/UNI-MACH48 Device ID #1                               | 1 |

| Register 003FH: S/UNI-MACH48 Device ID #2                               | 2 |

| Register 0040H: RXPHY Configuration                                     | 3 |

| Register 0041H: RXPHY Interrupt Status                                        | 205 |

|-------------------------------------------------------------------------------|-----|

| Register 0042H: RXPHY Interrupt Enable                                        | 206 |

| Register 0043H: RXPHY Indirect Burst Size                                     | 207 |

| Register 0044H: RXPHY Calendar Length                                         | 209 |

| Register 0045H: RXPHY Calendar Indirect Address Data                          | 210 |

| Register 0046H: RXPHY Data Type Field                                         | 212 |

| Register 0048H: TXPHY Configuration                                           | 213 |

| Register 0049H: TXPHY Interrupt Status                                        | 215 |

| Register 004AH: TXPHY Interrupt Enable                                        | 216 |

| Register 004BH: TXPHY Data Type Field                                         | 217 |

| Register 0050H: RXSDQ FIFO Reset                                              | 218 |

| Register 0051H: RXSDQ FIFO Interrupt Enable                                   | 219 |

| Register 0053H: RXSDQ FIFO Overflow Port and Interrupt Indication             | 220 |

| Register 0054H: RXSDQ FIFO EOP Error Port and Interrupt Indication            | 221 |

| Register 0055H: RXSDQ FIFO SOP Error Port and Interrupt Indication            | 222 |

| Register 0058H: RXSDQ FIFO Indirect Address                                   | 223 |

| Register 0059H: RXSDQ FIFO Indirect Configuration                             | 225 |

| Register 005AH: RXSDQ FIFO Indirect Data Available Threshold                  | 227 |

| Register 005BH: RXSDQ FIFO Indirect Cell and Packet Count                     | 229 |

| Register 005CH: RXSDQ FIFO Cells and Packets Accepted Aggregate Count (LSB)   | 230 |

| Register 005DH: RXSDQ FIFO Cells and Packets Accepted Aggregate Count         | 221 |

| (MSB)<br>Register 005EH: RXSDQ FIFO Cells and Packets Dropped Aggregate Count |     |

| Register 0060H: TXSDQ FIFO Reset                                              |     |

| Register 0061H: TXSDQ FIFO Interrupt Enable                                   |     |

| Register 0063H: TXSDQ FIFO Overflow Port and Interrupt Indication             |     |

| Register 0064H: TXSDQ FIFO EOP Error Port and Interrupt Indication            |     |

| Register 0065H: TXSDQ FIFO SOP Error Port and Interrupt Indication            |     |

| Register 0068H: TXSDQ FIFO Indirect Address                                   |     |

| Register 0069H: TXSDQ FIFO Indirect Configuration                             |     |

| Register 006AH: TXSDQ FIFO Indirect Data and Buffer Available Thresholds      |     |

| Register 006BH: TXSDQ FIFO Indirect Cells and Packets Count                   |     |

| Register 006CH: TXSDQ FIFO Cells and Packets Accepted Aggregate Count         | 240 |

| (LSB)                                                                         | 246 |

| Register 006DH: TXSDQ FIFO Cells and Packets Accepted Aggregate Count (MSB)   | 247 |

|-------------------------------------------------------------------------------|-----|

| Register 006EH: TXSDQ FIFO Cells and Packets Dropped Aggregate Count          | 248 |

| Register RCFP_BASE + 0H: RCFP Configuration                                   | 250 |

| Register RCFP_BASE + 1H: RCFP Interrupt Enable                                | 253 |

| Register RCFP_BASE + 2H: RCFP Interrupt Indication and Status                 | 255 |

| Register RCFP_BASE + 3H: RCFP Minimum Packet Length                           | 257 |

| Register RCFP_BASE + 4H: RCFP Maximum Packet Length                           | 258 |

| Register RCFP_BASE + 5H: RCFP LCD Count Threshold                             | 259 |

| Register RCFP_BASE + 6H: RCFP Idle Cell Header and Mask                       | 260 |

| Register RCFP_BASE + 7H: RCFP Receive Byte/Idle Cell Counter (LSB)            | 262 |

| Register RCFP_BASE + 8H: RCFP Receive Byte/Idle Cell Counter                  | 263 |

| Register RCFP_BASE + 9H: RCFP Receive Byte/Idle Cell Counter (MSB)            | 264 |

| Register RCFP_BASE + AH: RCFP Packet/Cell Counter (LSB)                       | 265 |

| Register RCFP_BASE + BH: RCFP Receive Packet/ATM Cell Counter (MSB)           | 266 |

| Register RCFP_BASE + CH: RCFP Receive Erred FCS/HCS Counter                   | 267 |

| Register RCFP_BASE + DH: RCFP Receive Aborted Packet Counter                  | 268 |

| Register RCFP_BASE + EH: RCFP Receive Minimum Length Packet Error<br>Counter  | 269 |

| Register RCFP_BASE + FH: RCFP Receive Maximum Length Packet Error<br>Counter  | 270 |

| Register TCFP_BASE + 0H: TCFP Configuration                                   | 272 |

| Register TCFP_BASE + 1H: TCFP Interrupt Indication                            | 275 |

| Register TCFP_BASE + 2H: TCFP Idle/Unassigned ATM Cell Header                 | 277 |

| Register TCFP_BASE + 3H: TCFP Diagnostics                                     | 279 |

| Register TCFP_BASE + 4H: TCFP Transmit Cell/Packet Counter (LSB)              | 281 |

| Register TCFP_BASE + 5H: TCFP Transmit Cell/Packet Counter (MSB)              | 282 |

| Register TCFP_BASE + 6H: TCFP Transmit Byte Counter (LSB)                     | 283 |

| Register TCFP_BASE + 7H: TCFP Transmit Byte Counter                           | 284 |

| Register TCFP_BASE + 8H: TCFP Transmit Byte Counter (MSB)                     | 285 |

| Register TCFP_BASE + 9H: TCFP Aborted Packet Counter                          | 286 |

| Register RTDP_BASE + 0H: RTDP Indirect Channel Select                         | 288 |

| Register RTDP_BASE + 1H: RTDP Indirect Configuration                          | 290 |

| Register RTDP_BASE + 2H: RTDP Indirect Minimum Packet Length and Bit<br>Order | 294 |

| Register RTDP_BASE + 3H: RTDP Indirect Maximum Packet Length                  | 296 |

| Register RTDP_BASE + 4H: RTDP Indirect LCD Count Threshold                            | 297 |

|---------------------------------------------------------------------------------------|-----|

| Register RTDP_BASE + 5H: RTDP Indirect Idle Cell Header and Mask                      | 298 |

| Register RTDP_BASE + 6H: RTDP Indirect Receive Byte/Idle Cell Counter (LSB)           | 300 |

| Register RTDP_BASE + 7H: RTDP Indirect Receive Byte/Idle Cell Counter<br>(MSB)        | 301 |

| Register RTDP_BASE + 8H: RTDP Indirect Packet/Cell Counter (LSB)                      | 302 |

| Register RTDP_BASE + 9H: RTDP Indirect Receive Packet/ATM Cell Counter<br>(MSB)       | 303 |

| Register RTDP_BASE + AH: RTDP Indirect Receive Erred FCS/HCS Counter                  | 304 |

| Register RTDP_BASE + BH: RTDP Indirect Receive Aborted Packet Counter                 | 305 |

| Register RTDP_BASE + CH: RTDP Indirect Receive Minimum Length Packet<br>Error Counter | 306 |

| Register RTDP_BASE + DH: RTDP Indirect Receive Maximum Length Packet<br>Error Counter | 307 |

| Register RTDP_BASE + 10H + n: RTDP Interrupt Enable (n = 0 to 5)                      | 308 |

| Register RTDP_BASE + 16H + <i>n</i> : RTDP Interrupt Indication ( <i>n</i> = 0 to 5)  | 310 |

| Register RTDP_BASE + 1CH: RTDP OOF Status                                             | 312 |

| Register RTDP_BASE + 1DH: RTDP LOF Status                                             | 313 |

| Register TTDP_BASE + 0H: TTDP Indirect Channel Select                                 | 315 |

| Register TTDP_BASE + 1H: TTDP Indirect Configuration                                  | 317 |

| Register TTDP_BASE + 2H: TTDP Indirect Idle/Unassigned ATM Cell Header                | 320 |

| Register TTDP_BASE + 3H: TTDP Indirect Diagnostics                                    | 322 |

| Register TTDP_BASE + 4H: TTDP Indirect Transmit Cell/Packet Counter (LSB)             | 324 |

| Register TTDP_BASE + 5H: TTDP Indirect Transmit Cell/Packet Counter (MSB)             | 325 |

| Register TTDP_BASE + 6H: TTDP Indirect Transmit Byte Counter (LSB)                    | 326 |

| Register TTDP_BASE + 7H: TTDP Indirect Transmit Byte Counter (MSB)                    | 327 |

| Register TTDP_BASE + 8H: TTDP Indirect Aborted Packet Counter                         | 328 |

| Register TTDP_BASE + 9H: TTDP CRC Error Mask                                          | 329 |

| Register TTDP_BASE + AH: TTDP Interrupt Enable 1                                      | 330 |

| Register TTDP_BASE + BH: TTDP Interrupt Enable 2                                      | 331 |

| Register TTDP_BASE + CH: TTDP Interrupt 1                                             | 332 |

| Register TTDP_BASE + DH: TTDP Interrupt 2                                             | 333 |

| Register TTDP_BASE + EH: TTDP Transmit Off                                            | 334 |

| Register RCAS12_BASE + 0H: RCAS12 Channel Disable                                     | 336 |

| Register RCAS12_BASE + 1H: RCAS12 Channel Loopback Enable                             | 337 |

| Register RCAS12_BASE + 2H + <i>x</i> : RCAS12 Timeslot <i>x</i> Configuration ( <i>x</i> = 0H to BH) | 220 |

|------------------------------------------------------------------------------------------------------|-----|

| Register TCAS12_BASE + 0H: TCAS12 Channel Configuration                                              |     |

| Register TCAS12_BASE + 1H: TCAS12 OALARM Configuration                                               |     |

| Register TCAS12_BASE + 2 + $x$ : TCAS12 Timeslot $x$ Configuration ( $x = 0$ H to                    | 042 |

| BH)                                                                                                  | 343 |

| Register TCAS12_BASE + EH: TCAS12 Idle Timeslot Fill Data                                            | 345 |

| Register DS3_BASE + 0H: SPLR Configuration                                                           | 348 |

| Register DS3_BASE + 1H: SPLR Interrupt Enable                                                        | 350 |

| Register DS3_BASE + 2H: SPLR Interrupt Status                                                        | 352 |

| Register DS3_BASE + 3H: SPLR Status                                                                  | 354 |

| Register DS3_BASE + 4H: SPLT Configuration                                                           | 356 |

| Register DS3_BASE + 5H: SPLT Control                                                                 | 358 |

| Register DS3_BASE + 6H: SPLT Diagnostics and G1 Octet                                                | 360 |

| Register DS3_BASE + 7H: SPLT F1 Octet                                                                | 362 |

| Register DS3_BASE + 8H: DS3 FRMR Configuration                                                       | 363 |

| Register DS3_BASE + 9H: DS3 FRMR Interrupt Enable (ACE=0)                                            | 365 |

| Register DS3_BASE + 9H: DS3 FRMR Additional Configuration Register                                   | 267 |

| (ACE=1)<br>Register DS3_BASE + AH: DS3 FRMR Interrupt Status                                         |     |

| Register DS3_BASE + BH: DS3 FRMR Status                                                              |     |

| Register DS3_BASE + CH: DS3 TRAN Configuration                                                       |     |

| Register DS3_BASE + DH: DS3 TRAN Diagnostic                                                          |     |

| Register DS3 BASE + 10H: RDLC Configuration                                                          |     |

| Register DS3 BASE + 11H: RDLC Interrupt Control                                                      |     |

| Register DS3_BASE + 12H: RDLC Status                                                                 |     |

| Register DS3_BASE + 13H: RDLC Data                                                                   |     |

| Register DS3_BASE + 14H: RDLC Primary Address Match                                                  |     |

| Register DS3_BASE + 15H: RDLC Secondary Address Match                                                | 385 |

| Register DS3_BASE + 18H: TDPR Configuration                                                          | 386 |

| Register DS3_BASE + 19H: TDPR Upper Transmit Threshold                                               | 388 |

| Register DS3_BASE + 1AH: TDPR Lower Interrupt Threshold                                              | 389 |

| Register DS3_BASE + 1BH: TDPR Interrupt Enable                                                       | 390 |

| Register DS3_BASE + 1CH: TDPR Interrupt Status/UDR Clear                                             | 392 |

| Register DS3_BASE + 1DH: TDPR Transmit Data                                                          | 394 |

| Register DS3_BASE + 20H: RBOC Configuration/Interrupt Enable                                         | 395 |

| Register DS3_BASE + 21H: RBOC Interrupt Status                                  | 396 |

|---------------------------------------------------------------------------------|-----|

| Register DS3_BASE + 24H: XBOC Control                                           | 397 |

| Register DS3_BASE + 25H: XBOC Bit Oriented Code                                 | 399 |

| Register DS3_BASE + 31H: DS3 PMON Interrupt Enable/Status                       | 400 |

| Register DS3_BASE + 36H: DS3 PMON Framing Bit Error Event Count (LSB)           | 401 |

| Register DS3_BASE + 37H: DS3 PMON Framing Bit Error Event Count (MSB)           | 402 |

| Register DS3_BASE + 3AH: DS3 PMON Parity Error Event Count LSB                  | 403 |

| Register DS3_BASE + 3BH: DS3 PMON Parity Error Event Count (MSB)                | 404 |

| Register DS3_BASE + 3CH: DS3 PMON Path Parity Error Event Count LSB             | 405 |

| Register DS3_BASE + 3DH: DS3 PMON Path Parity Error Event Count (MSB)           | 406 |

| Register DS3_BASE + 3EH: DS3 PMON FEBE Event Count (LSB)                        | 407 |

| Register DS3_BASE + 3FH: DS3 PMON FEBE Event Count (MSB)                        | 408 |

| Register DS3_BASE + 41H: PLCP PMON Interrupt Enable/Status                      | 409 |

| Register DS3_BASE + 48H: PLCP PMON FEBE Count (LSB)                             | 410 |

| Register DS3_BASE + 49H: PLCP PMON FEBE Count (MSB)                             | 411 |

| Register DS3_BASE + 4AH: PLCP PMON B1 Error Count LSB                           | 412 |

| Register DS3_BASE + 4BH: PLCP PMON B1 Error Count (MSB)                         | 413 |

| Register DS3_BASE + 4CH: PLCP PMON Framing Error Event Count LSB                | 414 |

| Register DS3_BASE + 4DH: PLCP PMON Framing Error Event Count (MSB)              | 415 |

| Register DS3_BASE + 50H: D3MD Configuration                                     | 416 |

| Register DS3_BASE + 51H: D3MD Interrupt Status                                  | 417 |

| Register DS3_BASE + 52H: D3MD Interrupt Enable                                  | 418 |

| Register DS3_BASE + 54H: D3MA Configuration                                     | 419 |

| Register DS3_BASE + 55H: D3MA Interrupt Status                                  | 420 |

| Register DS3_BASE + 56H: D3MA Interrupt Enable                                  | 421 |

| Register SIRP_BASE + x: SIRP Timeslot x Configuration Register (x = 00H to 0BH) | 423 |

| Register SIRP_BASE + 0CH: SIRP Configuration Register                           | 426 |

| Register 1500H: PRGD Control                                                    | 428 |

| Register 1501H: PRGD Interrupt Enable/Status                                    | 430 |

| Register 1502H: PRGD Length                                                     | 432 |

| Register 1503H: PRGD Tap                                                        | 433 |

| Register 1504H: PRGD Error Insertion Register                                   | 434 |

| Register 1508H: PRGD Pattern Insertion #1                                       | 435 |

| Register 1509H: PRGD Pattern Insertion #2                                       | 436 |

|                                                                                 |     |

| Register 150AH: PRGD Pattern Insertion #34                                | 37  |

|---------------------------------------------------------------------------|-----|

| Register 150BH: PRGD Pattern Insertion #44                                | 138 |

| Register 150CH: PRGD Pattern Detector #14                                 | 39  |

| Register 150DH: PRGD Pattern Detector #24                                 | 40  |

| Register 150EH: PRGD Pattern Detector #34                                 | 41  |

| Register 150FH: PRGD Pattern Detector #4                                  | 42  |

| Register PRGM_BASE + 00H: PRGM Indirect Address4                          | 45  |

| Register PRGM_BASE + 01H : PRGM Indirect Data4                            | 47  |

| PRGM Indirect Register 0H: Monitor Timeslot Configuration Page4           | 48  |

| PRGM Indirect Register 1H: Monitor PRBS[22:7] Accumulator Page 4          | 150 |

| PRGM Indirect Register 2H: Monitor PRBS[6:0] Accumulator Page4            | 51  |

| PRGM Indirect Register 3H: Monitor B1/E1 Value Page4                      | 52  |

| PRGM Indirect Register 4H: Monitor Error Count Page4                      | 153 |

| PRGM Indirect Register 5H: Monitor Received B1/E1 Bytes Page              | 54  |

| PRGM Indirect Register 8H: Generator Timeslot Configuration Page4         | 55  |

| PRGM Indirect Register 9H: Generator PRBS[22:7] Accumulator Page4         | 57  |

| PRGM Indirect Register AH: Generator PRBS[6:0] Accumulator Page4          | 58  |

| PRGM Indirect Register BH: Generator B1/E1 Value Page4                    | 59  |

| Register PRGM_BASE + 02H: PRGM Generator Payload Configuration4           | 60  |

| Register PRGM_BASE + 03H: PRGM Monitor Payload Configuration 4            | 62  |

| Register PRGM_BASE + 04H: PRGM Monitor Byte Error Interrupt Status 4      | 64  |

| Register PRGM_BASE + 05H: PRGM Monitor Byte Error Interrupt Enable 4      | 65  |

| Register PRGM_BASE + 06H: PRGM Monitor B1/E1 Bytes Interrupt Status 4     | 66  |

| Register PRGM_BASE + 07H: Monitor B1/E1 Bytes Interrupt Enable4           | 67  |

| Register PRGM_BASE + 09H: PRGM Monitor Synchronization Interrupt Status 4 | 69  |

| Register PRGM_BASE + 0AH: PRGM Monitor Synchronization Interrupt Enable4  | 70  |

| Register PRGM_BASE + 0BH: PRGM Monitor Synchronization Status 4           | 171 |

| Register PRGM_BASE + 0CH: PRGM Performance Counters Transfer Trigger4     | 72  |

| Register RHPP_BASE + 00H: RHPP Indirect Address                           | 74  |

| Register RHPP_BASE + 01H: RHPP Indirect Data4                             | 76  |

| RHPP Indirect Register 00H: Pointer Interpreter Configuration4            | 77  |

| RHPP Indirect Register 01H: Pointer Interpreter Configuration4            | 179 |

| RHPP Indirect Register 02H: Pointer Value and ERDI4                       | 80  |

| RHPP Indirect Register 05H: Pointer Interpreter status4                   | 81  |

| RHPP Indirect Register 07H: RHPP Path REI Error Counter4                  | 83  |

| Register RHPP_BASE + 02H: RHPP Payload Configuration                                      |     |

|-------------------------------------------------------------------------------------------|-----|

| Register RHPP_BASE + 03H: RHPP Counters update                                            |     |

| Register RHPP_BASE + 04H: RHPP Path Interrupt Status                                      | 487 |

| Register RHPP_BASE + 05H: RHPP Pointer Concatenation Processing Disable                   | 488 |

| Register RHPP_BASE + 08H + 8x: RHPP Pointer Interpreter Status (x = 0 to BH)              | 489 |

| Register RHPP_BASE + 09H + 8x: RHPP Pointer Interpreter Interrupt Enable (x<br>= 0 to BH) | 491 |

| Register RHPP_BASE + 0AH + 8x: RHPP Pointer Interpreter Interrupt Status (x<br>= 0 to BH) | 493 |

| Register STSI_BASE + 00H: STSI Indirect Address                                           | 496 |

| Register STSI_BASE + 01H: STSI Indirect Data                                              | 499 |

| Register STSI_BASE + 02H: STSI Configuration                                              | 501 |

| Register STSI_BASE + 03H: STSI Interrupt Status                                           | 503 |

| Register R8TD_BASE + 00H: R8TD Control and Status                                         | 505 |

| Register R8TD_BASE + 01H: R8TD Interrupt Status                                           | 508 |

| Register R8TD_BASE + 02H: R8TD Line Code Violation Count                                  | 510 |

| Register R8TD_BASE + 03H: R8TD Analog Control 1                                           | 511 |

| Register R8TD_BASE + 04H: R8TD Analog Control 2                                           | 513 |

| Register R8TD_BASE + 05H: R8TD Analog Control 3                                           | 514 |

| Register T8TE_BASE + 00H: T8TE Control and Status                                         | 517 |

| Register T8TE_BASE + 01H: T8TE Interrupt Status                                           | 519 |

| Register T8TE_BASE + 02H: T8TE TelecomBus Mode #1                                         | 520 |

| Register T8TE_BASE + 03H: T8TE TelecomBus Mode #2                                         | 521 |

| Register T8TE_BASE + 04H: T8TE Test Pattern                                               | 522 |

| Register T8TE_BASE + 05H: T8TE Analog Control                                             | 523 |

| Register T8TE_BASE + 06H: T8TE DTB Bus                                                    | 525 |

| Register DLL_BASE + 0H: DLL Configuration                                                 | 527 |

| Register DLL_BASE + 01H: DLL Clock Vernier Control                                        | 528 |

| Register DLL_BASE + 02H: DLL Clock Delay Tap Status                                       | 529 |

| Register DLL_BASE + 03H: DLL Clock Control Status                                         | 530 |

| Register 18ACH: CSTR Control                                                              | 532 |

| Register 18ADH: CSTR Interrupt Enable and CSU Lock Status                                 | 533 |

| Register 18AEH: CSTR CSU Lock Interrupt Indication                                        | 534 |

| Register 1900H + x: S/UNI-MACH48 Channel #x Dropped Cell/Packet Counter                   | 536 |

| Register 1930H: S/UNI-MACH48 Drop Counter Interrupt Enable #1                             | 537 |

|                                                                                           |     |

| Register 1931H: | S/UNI-MACH48 Drop Counter Interrupt Enable #2 | 538 |

|-----------------|-----------------------------------------------|-----|

| Register 1932H: | S/UNI-MACH48 Drop Counter Interrupt Enable #3 | 539 |

| Register 1933H: | S/UNI-MACH48 Drop Counter Interrupt #1        | 540 |

| Register 1934H: | S/UNI-MACH48 Drop Counter Interrupt #2        | 541 |

| Register 1935H: | S/UNI-MACH48 Drop Counter Interrupt #3        | 542 |

| Register 2000H: | S/UNI-MACH48 Master Test                      | 544 |

| Register 2001H: | S/UNI-MACH48 Test Mode Address Force Enable   | 546 |

| Register 2002H: | S/UNI-MACH48 Test Mode Address Force Value    | 547 |

| Register 2003H: | S/UNI-MACH48 Top Level Test Register          | 548 |

## **List of Figures**

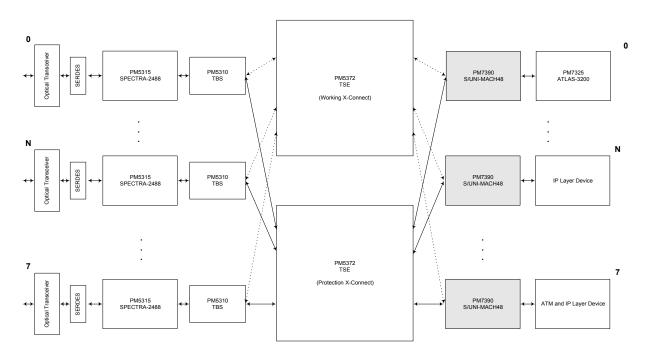

| Figure 1  | Multi-Service ATM/POS Switch Port Application      | 35  |

|-----------|----------------------------------------------------|-----|

| Figure 2  | Pin Diagram – Bottom View                          | 46  |

| Figure 3  | Pin Diagram – Bottom View (Top,Left Quadrant)      | 47  |

| Figure 4  | Pin Diagram – Bottom View (Top, Right Quadrant)    | 48  |

| Figure 5  | Pin Diagram – Bottom View (Bottom, Left Quadrant)  | 49  |

| Figure 6  | Pin Diagram – Bottom View (Bottom, Right Quadrant) | 50  |

| Figure 7  | Cell Delineation State Diagram                     | 87  |

| Figure 8  | PPP/HDLC Over SONET Frame Format                   | 89  |

| Figure 9  | CRC Decoder                                        | 90  |

| Figure 10 | CRC Generator                                      | 98  |

| Figure 11 | Generic LVDS Link Block Diagram                    | 104 |

| Figure 12 | Input Observation Cell (IN_CELL)                   | 555 |

| Figure 13 | Output Cell (OUT_CELL)                             | 556 |

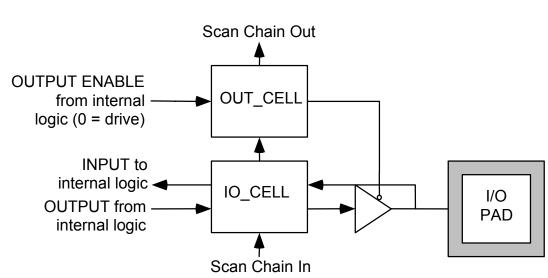

| Figure 14 | Bidirectional Cell (IO_CELL)                       | 556 |

| Figure 15 | Layout of Output Enable and Bidirectional Cells    | 557 |

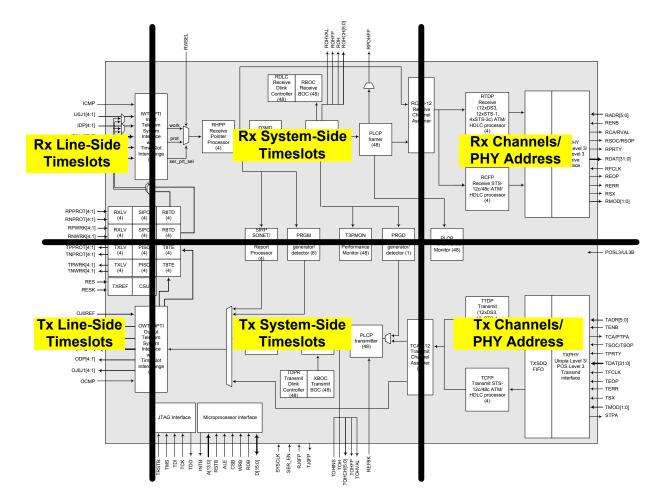

| Figure 16 | S/UNI-MACH48 Conceptual Regions                    | 559 |

| Figure 17 | DS3 PLCP Frame Format                              | 562 |

| Figure 18 | DS3 Frame Structure                                | 565 |

| Figure 19 | ATM Mapping into a STS-12c/STM-4c SPE              | 567 |

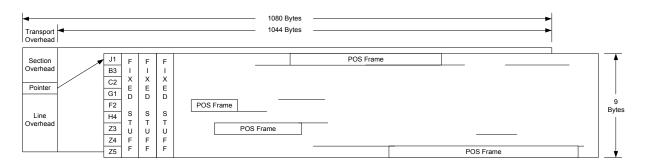

| Figure 20 | POS Mapping into a STS-12c/STM-4c SPE              | 567 |

| Figure 21 | A 52 Byte ATM Data Structure                       | 569 |

| Figure 22 | A 63 Byte Packet Data Structure                    | 570 |

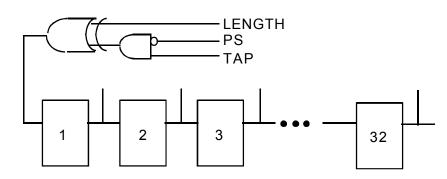

| Figure 23 | PRGD Pattern Generator                             | 594 |

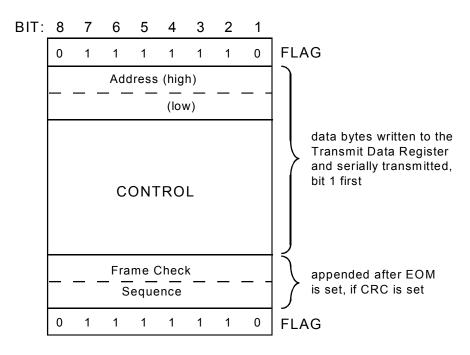

| Figure 24 | Typical DS3 FDL Data Frame                         | 603 |

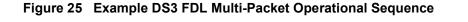

| Figure 25 | Example DS3 FDL Multi-Packet Operational Sequence  | 604 |

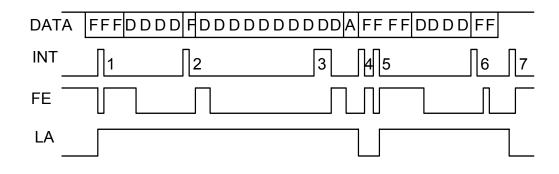

| Figure 26 | Boundary Scan Architecture                         | 607 |

| Figure 27 | TAP Controller Finite State Machine                | 609 |

| Figure 28 | Analog Power Supply Filtering Circuits             | 613 |

| Figure 29 | DS3 Overhead Extraction                            | 614 |

| Figure 30 | DS3 Overhead Insertion                             | 615 |

| Figure 31 | Incoming Parallel TelecomBus Timing                | 617 |

| Figure 32 | Outgoing Parallel TelecomBus                       | 619 |

| Figure 33 | Receive Serial TelecomBus Link Timing              | 620 |

| Figure 34 | Outgoing Serial TelecomBus                                     | 621 |

|-----------|----------------------------------------------------------------|-----|

| Figure 35 | Transmit UTOPIA Level 3 System Interface Timing for Single PHY | 622 |

| Figure 36 | Transmit UTOPIA Level 3 System Interface Timing for Multi-PHY  | 623 |

| Figure 37 | Receive UTOPIA Level 3 System Interface Timing for Single PHY  | 624 |

| Figure 38 | Receive UTOPIA Level 3 System Interface Timing for Multi-PHY   | 624 |

| Figure 39 | Transmit POS Level 3 System Interface Timing                   | 625 |

| Figure 40 | TPAHOLD Set to 0                                               | 627 |

| Figure 41 | TPAHOLD Set to 1                                               | 630 |

| Figure 42 | Receive POS Level 3 System Interface Timing                    | 631 |

| Figure 43 | Intel Microprocessor Interface Read Timing                     | 635 |

| Figure 44 | Intel Microprocessor Interface Write Timing                    | 637 |

| Figure 45 | System Miscellaneous Timing Diagram                            | 638 |

| Figure 46 | Receive System Interface Timing Diagram                        | 640 |

| Figure 47 | Transmit System Interface Timing                               | 642 |

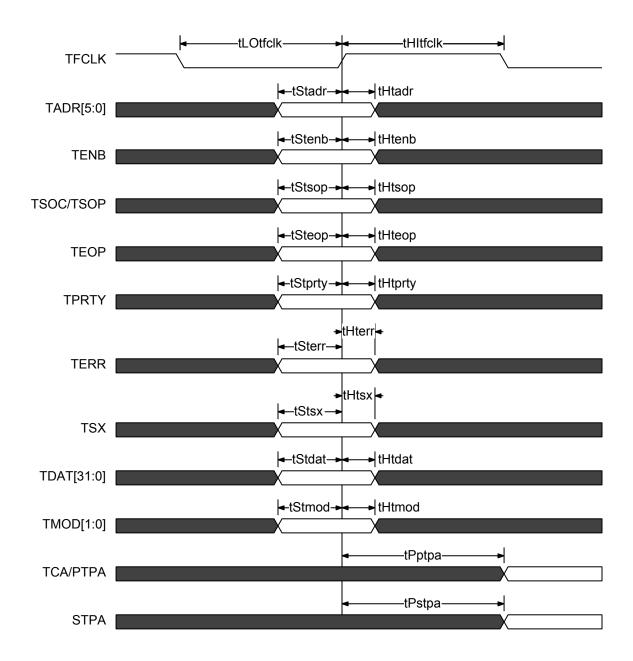

| Figure 48 | SYSCLK Input Timing                                            | 644 |

| Figure 49 | SYSCLK Output Timing                                           | 646 |

| Figure 50 | JTAG Port Interface Timing                                     | 648 |

| Figure 51 | Mechanical Drawing 560 Pin Ultra Ball Grid Array (UBGA)        | 652 |

## **List of Tables**

| Table 1  | Asynchronous DS3 Mapping to STS-1 (STM-0/AU3)               |     |

|----------|-------------------------------------------------------------|-----|

| Table 2  | DS3 AIS Format                                              |     |

| Table 3  | Byte Destuffing                                             |     |

| Table 4  | Byte Stuffing                                               |     |

| Table 5  | Register Memory Map                                         | 107 |

| Table 6  | Receive Timeslot Configuration for Different Traffic Types  | 126 |

| Table 7  | Valid Receive Timeslot Mappings                             | 127 |

| Table 8  | Transmit Timeslot Configuration for Different Traffic Types | 133 |

| Table 9  | Valid Transmit Timeslot Mappings                            | 134 |

| Table 10 | 8 KHz Reference Selection                                   | 142 |

| Table 11 | DS3 LOF Integration Period Configuration                    | 145 |

| Table 12 | Incoming STSI Mapping Modes                                 | 149 |

| Table 13 | Outgoing STSI Mapping Modes                                 | 150 |

| Table 14 | Functionality of the CRC_SEL[1 0] Register Bits             | 251 |

| Table 15 | Average STS-x cell period versus LCD integration period     | 259 |

| Table 16 | Selection of the number of FLAG Bytes                       | 273 |

| Table 17 | CRC Mode Selection                                          | 273 |

| Table 18 | Functionality of the CRC_SEL[1 0] Register Bits             | 291 |

| Table 19 | Selection of the number of Flag Bytes                       | 318 |

| Table 20 | CRC Mode Selection                                          | 319 |

| Table 21 | RCAS12 Timeslot Mode Selection                              | 338 |

| Table 22 | TCAS12 Timeslot Mode Selection                              | 344 |

| Table 23 | DS3 Base Address Assignment                                 | 346 |

| Table 24 | SPLR FORM[1 0] Configurations                               | 349 |

| Table 25 | PLCP LOF Declaration/Removal Times                          | 354 |

| Table 26 | SPLT FORM[1 0] Configurations                               | 357 |

| Table 27 | DS3 FRMR AIS Configurations                                 | 368 |

| Table 28 | RDLC PBS[2 0] Data Status                                   | 381 |

| Table 29 | SIRP RDI and REI Reporting Modes                            | 424 |

| Table 30 | SIRP RDI Settings                                           | 424 |

| Table 31 | SIRP RDI Maintenance                                        | 424 |

| Table 32 | SIRP RDI Priority Schemes                                   | 427 |

| Table 33 | PRGD Pattern Detector Register Configuration                | 429 |

| Table 34 | PRGD Generated Bit Error Rate Configurations             | 434 |

|----------|----------------------------------------------------------|-----|

| Table 35 | PRGM Timeslot Selection                                  | 445 |

| Table 36 | PRGM Monitor RAM Pages                                   | 446 |

| Table 37 | PRGM Generator RAM Pages                                 | 446 |

| Table 38 | PRGM Generator Master/Slave Configuration                | 461 |

| Table 39 | PRGM Monitor Master/Slave Configuration                  | 463 |

| Table 40 | TelecomBus Mode                                          | 521 |

| Table 41 | Test Mode Register Memory Map                            | 543 |

| Table 42 | Instruction Register (Length - 3 bits)                   | 549 |

| Table 43 | Identification Register                                  | 549 |

| Table 44 | Boundary Scan Register                                   | 549 |

| Table 45 | Serial TelecomBus 8B/10B Control Character Decoding      | 560 |

| Table 46 | Serial TelecomBus 8B/10B Control Character Encoding      | 561 |

| Table 47 | PLCP Overhead Processing                                 | 563 |

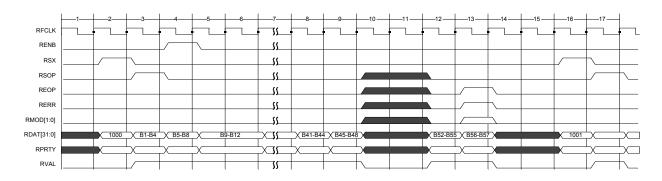

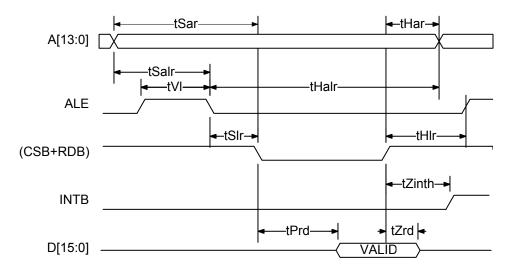

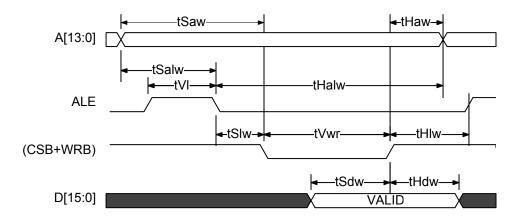

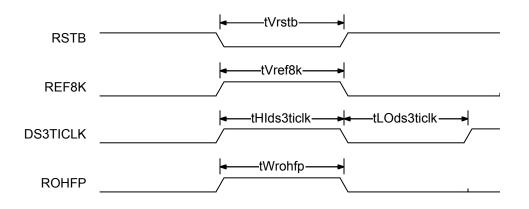

| Table 48 | PLCP Path Overhead Identifier Codes                      | 564 |