# 16-Bit Flow-Through EDAC Error Detection And Correction unit

#### 1. Introduction

The 29C516E TEMIC EDAC is a very low power flow-through 16-bit Error Detection And Correction unit (EDAC) with two user data buses. The EDAC is used in a high integrity system for monitoring and correction of data values coming from the memory space. During a processor write cycle, at each memory location (16-bit width), EDAC calculated checkword (6 or 8-bit width) is added. When performing a read operation from memory, the 29C516E verifies the entire checkword and data combination. It detects and can correct 100% of all the single-bit errors and it detects all double-bit errors. When the 29C516E uses 6-checkbit, it can detect any error on any single 4-bit memory chip. The 8-check-bit option gives the additional capability to detect all errors on any single 8-bit memory chip. All the errors are signaled to the master system (via 2 error Flags) in order to allow the processor to make the required action.

The 29C516E operates in two possible modes: corrected or detected mode. In the corrected mode, the single-bit in error is complemented (corrected). Then, the available entire data is placed on the output port and the Correctable Error Flag is set. In case of double-bit errors (or more),

the corrupted data is placed on the output port and the Uncorrectable Error Flag is set. Note that when there is more than two errors, then some bit patterns may appear as possible correctable errors. Therefore, if the environment produces this type of error, the EDAC must be used in detect and provide no automatic correction. Data and syndrome analysis must be done.

The 29C516E acts as a data buffer for μP-memory interfacing. A flow-through EDAC is placed in the data bus path, between the processor and the memory to be protected. This component is able to serve two different users of one memory space. So, it forms the interface between the 22/24-bit (16+6/16+8) memory data bus and the two 16-bit processor data busses with a high drive capability (-12.8 mA). The two data ports can be used to create a dual port bus in front of memory space. The User-1(2) can transfer data from/to the memory or from/to the User-2(1), by-passing the memory. During read or write memory cycles processed by the User-1(2), the User-2(1) have the possibility to listen the transferred data.

#### 2. Features

- Very Low Power CMOS

- 16–Bit operation with 6 or 8 Check Bits

- Fast Error Detection : 31 ns (max.)

- Fast Error Correction: 32 ns (max.)

- Corrects all Single-Bit Errors

- Detects all Double-Bit Errors

- Detects some Multi-Bit Errors

- Detects Chip Errors (x1, x4 & x8 RAM Format)

- Correctable and Uncorrectable Error Flags

- Two User Data Buses

- User to User Transfer and Listening operation

- High Drive Capability on Buses: -12.8 mA

- TTL Compatible

- Single 5V ±10% Power Supply

- 100 Pin Multilayer Quad Flat Pack (Flat leaded or L leaded).

# 3. Interface

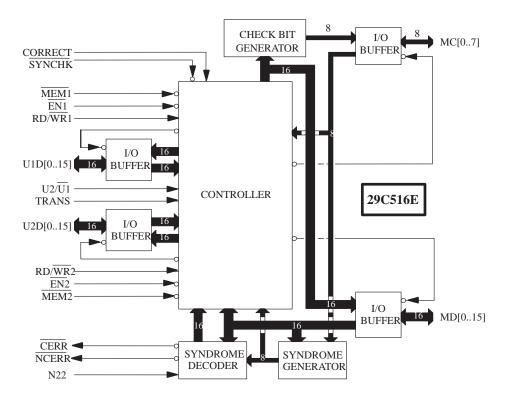

### 3.1. Functional Diagram

Figure 1.Functional Diagram

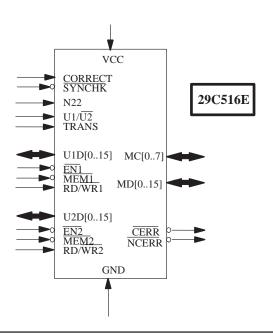

# 3.2. Block Diagram Figure 2.Block Diagram

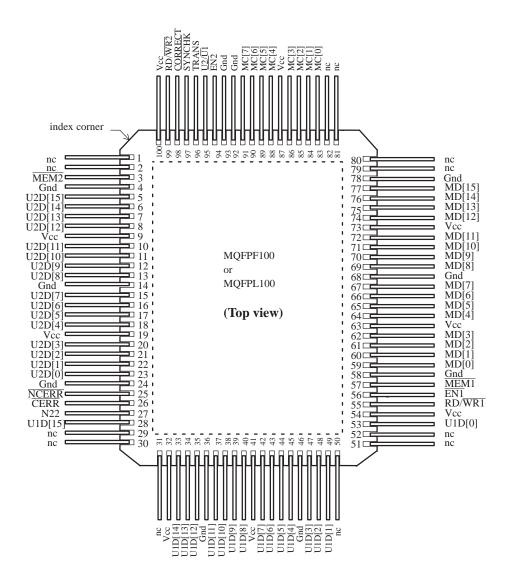

### 3.3. Pin Configuration for multilayer quad Flat-pack (flat or L leaded)

**Figure 3.Pin Configuration**

# 3.4. Pin Description

Table 1:

| Name             | Pin Description           | I/O  | Active | Description                                                                                                                            |

|------------------|---------------------------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| Buses            |                           | I    |        |                                                                                                                                        |

| U1D[015]         | 53,4947,4542,4037,3533,28 | I/O* | High   | User 1 Data Bus                                                                                                                        |

| U2D[015]         | 2320,1815,1310,85         | I/O* | High   | User 2 Data Bus                                                                                                                        |

| MD[015]          | 5962,6467,6972,7477       | I/O* | High   | Memory Data Bus                                                                                                                        |

| MC[07]           | 8386,8891                 | I/O* | High   | Memory Check-bit Bus                                                                                                                   |

| Error Flags      |                           | •    |        |                                                                                                                                        |

| CERR             | 26                        | 0    | Low    | Correctable Error                                                                                                                      |

| NCERR            | 25                        | О    | Low    | Uncorrectable Error                                                                                                                    |

| General Con      | trol Signals              | •    |        |                                                                                                                                        |

| CORRECT          | 98                        | I*   | High   | When active, the EDAC is in CORRECT mode. If low, the EDAC is in DETECT mode.                                                          |

| SYNCHK           | 97                        | I*   | Low    | Selects the Syndrome bits (high byte) and the Check-bits (low byte) to be driven on the selected User Data Bus.                        |

| N22              | 27                        | I*   | High   | When active, the EDAC uses 6 check–bits. If low, the EDAC uses 8 check–bits in memory read.                                            |

| TRANS            | 96                        | I*   | H/L    | Selects the Data path to be used. If high, the EDAC access the memory, if low, the EDAC access the transfer buffer.                    |

| U2/U1            | 95                        | I*   | H/L    | Selects who is the master of User 1 and User 2. The master is responsible for applying RD/WRx, MEMx, and ENx signals in a correct way. |

| User 1 Contr     | ol Signals                | 1    | •      |                                                                                                                                        |

| RD/WRT           | 55                        | I*   | H/L    | User 1 Read/Write signal                                                                                                               |

| EN1              | 56                        | I*   | Low    | User 1 Output Enable                                                                                                                   |

| MEM1             | 57                        | I*   | Low    | User 1 Memory Select                                                                                                                   |

| User 1 Contr     | ol Signals                |      |        |                                                                                                                                        |

| RD/WR2           | 99                        | I*   | H/L    | User 2 Read/Write signal                                                                                                               |

| EN2              | 94                        | I*   | Low    | User 2 Output Enable                                                                                                                   |

| MEM2             | 3                         | I*   | Low    | User 2 Memory Select                                                                                                                   |

| Power (Buffe     | ers)                      |      |        |                                                                                                                                        |

| VCC <sub>B</sub> | 9,19,32,41,54,63,73,87    | I    | _      | Buffers supply (5 V nominal)                                                                                                           |

| $GND_B$          | 4,14,24,36,46,58,68,78,92 | I    | _      | Buffers 0 V nominal reference                                                                                                          |

| Power (Core)     | )                         |      |        |                                                                                                                                        |

| VCC <sub>C</sub> | 100                       | I    | _      | Core supply (5 V nominal)                                                                                                              |

| $GND_C$          | 93                        | I    | _      | Core 0 V reference                                                                                                                     |

<sup>\*</sup> Pull-up buffers

### 4. Check-Bit Generation

The Check-bit Generator produces 8 check-bits (whatever N22 value) from the incoming User Data Word UxD[0..15] according the Table 2.

Example: to create check-bit 0, bit 13, 12, 8, 7, 6, 5, 4 and 0 of the Data Word are XORed together.

If memory devices 8-bit wide are used, 24 bits (MD[0..15] & MC[0..7]) are stored to give error detection. But if memory devices 1-bit or 4-bit wide are used, 22 bits (MD[0..15] & MC[0..5]) are stored to give error detection.

Table 2: Check Bit Generation (indicates a bit of UxD bus used in the XOR/NXOR)

| MC[] | PARITY    |    |    |    |    |    |    |   | UxI | D[] |   |   |   |   |   |   |   |

|------|-----------|----|----|----|----|----|----|---|-----|-----|---|---|---|---|---|---|---|

|      |           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0    | Even(XOR) |    |    | X  | X  |    |    |   | X   | X   | X | х | Х |   |   |   | Х |

| 1    | Even(XOR) |    | х  |    |    | х  | Х  | Х | Х   |     | Х |   | X |   |   | Х |   |

| 2    | Odd(NXOR) | X  |    |    | X  |    |    | X |     |     |   | х |   | X | X | X | Х |

| 3    | Odd(NXOR) |    | X  | X  |    |    | х  |   |     |     |   |   | x | x | X | X | х |

|      |           |    |    |    |    |    |    |   |     |     |   |   |   |   |   |   |   |

| 4    | Even(XOR) | X  |    |    |    | X  | X  | X | X   | X   |   | X |   |   | X |   |   |

| 5    | Even(XOR) | X  | X  | X  | X  | X  |    |   |     | X   | X |   |   | X |   |   |   |

| 6    | Even(XOR) |    |    | X  |    | X  |    |   | X   | X   |   | х | X |   | X | X |   |

| 7    | Odd(NXOR) | X  |    | х  | X  | х  |    |   |     |     |   | х |   | х | Х | х |   |

### 5. Syndrome Generation

The syndrome Generator produces 8 syndrome—bits (whatever N22 value) from the incoming Memory Data Word MD[0..15] and the associated Check—bits MC[0..7] (or MC[0..5]) according the Table 3.

Syndrome-bit SY[x] is the XOR of the generated Check-bit MC[x] with the generation of Chek-bit on MD[..].

Example: to create syndrome-bit 3, first the bit 14, 13, 10, 4, 3, 2, 1 and 0 of the Data Word

(MD[14,13,10,4,3,2,1,0]) are NXORed. Then, the result is XORed with the associated Check-bit (MC[3]) of the Check-byte read in the same time as Data Word is checked.

If the memory uses x8 devices, then the bits should be physically divided as follows: MC[0..7], MD[0..7] and MD[8..15] . For x4 organization, the bits should be divided MC[0..2]+MC[6], MC[3..5]+MC[7], MD[0..3], MD[4..7], MD[8..11] and MD[12..15].

Table 3: Syndrome Bit Generation (indicates a bit of MD and MC buses used in the XOR/NXOR)

| SY[] | PARITY    |    |    |    |    |    |    |   | MI | <b>)</b> [] |   |   |   |   |   |   |   |   |   |   | MC | [] |   |   |   |

|------|-----------|----|----|----|----|----|----|---|----|-------------|---|---|---|---|---|---|---|---|---|---|----|----|---|---|---|

|      |           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 5 | 4 | 3  | 6  | 2 | 1 | 0 |

| 0    | EVEN(XOR) |    |    | х  | х  |    |    |   | х  | х           | х | х | х |   |   |   | х |   |   |   |    |    |   |   | Х |

| 1    | EVEN(XOR) |    | х  |    |    | Х  | х  | Х | Х  |             | х |   | Х |   |   | х |   |   |   |   |    |    |   | х |   |

| 2    | ODD(NXOR) | Х  |    |    | Х  |    |    | Х |    |             |   | х |   | Х | Х | Х | Х |   |   |   |    |    | Х |   |   |

| 3    | ODD(NXOR) |    | х  | х  |    |    | х  |   |    |             |   |   | х | х | х | х | х |   |   |   | X  |    |   |   |   |

|      |           |    |    |    |    |    |    |   |    |             |   |   |   |   |   |   |   |   |   |   |    |    |   |   |   |

| 4    | EVEN(XOR) | х  |    |    |    | х  | х  | х | х  | х           |   | х |   |   | х |   |   |   |   | X |    |    |   |   |   |

| 5    | EVEN(XOR) | х  | х  | х  | х  | Х  |    |   |    | х           | х |   |   | Х |   |   |   |   | Х |   |    |    |   |   |   |

|      |           |    |    |    |    |    |    |   |    |             |   |   |   |   |   |   |   |   |   |   |    |    |   |   |   |

| 6    | EVEN(XOR) |    |    | х  |    | х  |    |   | х  | х           |   | х | х |   | х | X |   |   |   |   |    | X  |   |   |   |

| 7    | ODD(NXOR) | х  |    | Х  | Х  | Х  |    |   |    |             |   | х |   | X | х | х |   | х |   |   |    |    |   |   |   |

MATRA MHS Rev. D (09 Dec. 97)

# 6. Syndrome Decoding

The syndrome decoder generates the error flags  $\overline{CERR}$  (Correctable ERRor) and  $\overline{NCERR}$  (Non–Correctable ERRor). If a correctable error occurs, the 29C516E EDAC provides corrected data to the user. The inputs are

the 8 syndrome bits from the syndrome generator, the 16 data bits from the memory and the control signal N22. N22 signal controls if 22 or 24 bits shall be decode from the entire memory word.

Table 4: 6-Bit Syndrome Word to Bit-In-Error (N22="1")

|      |      |       |      |    | Hex | 0     | 1    | 2    | 3    |

|------|------|-------|------|----|-----|-------|------|------|------|

| Sync | lrom | e Bit | SY[. | .] | 5   | 0     | 0    | 1    | 1    |

|      |      |       |      |    | 4   | 0     | 1    | 0    | 1    |

| Hex  | 3    | 2     | 1    | 0  |     |       |      |      |      |

| 0    | 0    | 0     | 0    | 0  |     | N.E.D | MC4  | MC5  | D    |

| 1    | 0    | 0     | 0    | 1  |     | MC0   | D    | D    | MD7  |

| 2    | 0    | 0     | 1    | 0  |     | MC1   | D    | D    | MD11 |

| 3    | 0    | 0     | 1    | 1  |     | D     | MD8  | MD6  | D    |

| 4    | 0    | 1     | 0    | 0  |     | MC2   | D    | D    | MD15 |

| 5    | 0    | 1     | 0    | 1  |     | D     | MD5  | MD12 | D    |

| 6    | 0    | 1     | 1    | 0  |     | D     | MD9  | M    | D    |

| 7    | 0    | 1     | 1    | 1  |     | M     | D    | D    | M    |

| 8    | 1    | 0     | 0    | 0  |     | MC3   | D    | D    | M    |

| 9    | 1    | 0     | 0    | 1  |     | D     | M    | MD13 | D    |

| A    | 1    | 0     | 1    | 0  |     | D     | MD10 | MD14 | D    |

| В    | 1    | 0     | 1    | 1  |     | MD4   | D    | D    | M    |

| С    | 1    | 1     | 0    | 0  |     | D     | MD2  | MD3  | D    |

| D    | 1    | 1     | 0    | 1  |     | MD0   | D    | D    | M    |

| E    | 1    | 1     | 1    | 0  |     | MD1   | D    | D    | M    |

| F    | 1    | 1     | 1    | 1  |     | D     | M    | M    | D    |

Note: N.E.D = No Errors Detected

MDx = Memory Data Bit–In–Error

MCx = Memory Check Bit–In–Error

D = Double–Bit–In–Error Detected

M = Multi–Bit–In–Error Detected

| Table 5: 8-Bit Syndrome Word to Bit-In-Error (N2 | $\sqrt{22} = 0$ |

|--------------------------------------------------|-----------------|

|--------------------------------------------------|-----------------|

|     |     |     |     |   | Hex | 0     | 1    | 2    | 3 | 4   | 5   | 6 | 7   | 8   | 9 | A    | В    | C   | D   | E    | F    |

|-----|-----|-----|-----|---|-----|-------|------|------|---|-----|-----|---|-----|-----|---|------|------|-----|-----|------|------|

|     |     |     |     |   | 7   | 0     | 0    | 0    | 0 | 0   | 0   | 0 | 0   | 1   | 1 | 1    | 1    | 1   | 1   | 1    | 1    |

| Sy  | ndr | ome | Bit |   | 6   | 0     | 0    | 0    | 0 | 1   | 1   | 1 | 1   | 0   | 0 | 0    | 0    | 1   | 1   | 1    | 1    |

|     | SY  | []  |     |   | 5   | 0     | 0    | 1    | 1 | 0   | 0   | 1 | 1   | 0   | 0 | 1    | 1    | 0   | 0   | 1    | 1    |

|     |     |     |     |   | 4   | 0     | 1    | 0    | 1 | 0   | 1   | 0 | 1   | 0   | 1 | 0    | 1    | 0   | 1   | 0    | 1    |

| Hex | 3   | 2   | 1   | 0 |     |       |      |      |   |     |     |   |     |     |   |      |      |     |     |      |      |

| 0   | 0   | 0   | 0   | 0 |     | N.E.D | MC4  | MC5  | D | MC6 | D   | D | D   | MC7 | D | D    | D    | D   | M   | M    | D    |

| 1   | 0   | 0   | 0   | 1 |     | MC0   | D    | D    | D | D   | D   | D | MD7 | D   | M | D    | M    | M   | D   | D    | D    |

| 2   | 0   | 0   | 1   | 0 |     | MC1   | D    | D    | M | D   | D   | D | D   | D   | M | D    | D    | M   | D   | D    | MD11 |

| 3   | 0   | 0   | 1   | 1 |     | D     | D    | MD6  | D | D   | MD8 | D | D   | D   | M | D    | D    | D   | D   | M    | D    |

| 4   | 0   | 1   | 0   | 0 |     | MC2   | D    | D    | D | D   | М   | M | M   | D   | D | D    | MD15 | M   | D   | D    | D    |

| 5   | 0   | 1   | 0   | 1 |     | D     | M    | D    | D | D   | D   | M | M   | D   | D | MD12 | D    | D   | MD5 | D    | D    |

| 6   | 0   | 1   | 1   | 0 |     | D     | MD9  | M    | D | D   | D   | M | M   | D   | D | M    | D    | D   | M   | M    | D    |

| 7   | 0   | 1   | 1   | 1 |     | M     | D    | D    | M | M   | D   | D | D   | M   | D | D    | M    | M   | D   | D    | M    |

| 8   | 1   | 0   | 0   | 0 |     | MC3   | D    | D    | M | D   | М   | D | D   | D   | D | D    | M    | M   | D   | D    | M    |

| 9   | 1   | 0   | 0   | 1 |     | D     | M    | M    | D | D   | М   | D | D   | M   | M | D    | D    | D   | M   | MD13 | D    |

| A   | 1   | 0   | 1   | 0 |     | D     | MD10 | MD14 | D | D   | D   | D | D   | M   | D | D    | D    | D   | M   | M    | D    |

| В   | 1   | 0   | 1   | 1 |     | D     | D    | D    | M | MD4 | D   | D | D   | M   | M | M    | M    | D   | M   | D    | М    |

| С   | 1   | 1   | 0   | 0 |     | D     | M    | D    | D | D   | D   | M | M   | D   | D | MD3  | D    | D   | MD2 | D    | D    |

| D   | 1   | 1   | 0   | 1 |     | MD0   | D    | D    | M | D   | D   | M | M   | D   | D | D    | M    | M   | D   | D    | M    |

| E   | 1   | 1   | 1   | 0 |     | M     | D    | D    | M | D   | D   | M | M   | D   | D | D    | M    | MD1 | D   | D    | М    |

| F   | 1   | 1   | 1   | 1 |     | D     | M    | M    | D | D   | М   | M | M   | D   | M | М    | D    | D   | M   | M    | D    |

Note: N.E.D = No Errors Detected MDx = Memory Data Bit–In–Error MCx = Memory Check Bit–In–Error D = Double–Bit–In–Error Detected

# 7. The 6-Bit Syndrome Word

M = Multi-Bit-In-Error Detected

This feature is available when the N22 pin is driven at a high level.

#### 7.1. No Errors

If there are no errors in the read Data or Check–Bit, all the syndrome byte is "00". The EDAC flags are inactive.

No Error: SY=00

#### 7.2. Single Bit-Error

A single bit-error in a Memory Data word read (MD[..]) causes three syndrome bits to be set to one. The code formed indicates which bit of the Memory Data word is incorrect.

For example, if MD[2] were incorrect, the syndrome byte would have bits 2, 3 and 4 set to one. The syndrome decoder of 29C516E EDAC decodes the information in the syndrome byte and only sets low the error flag  $\overline{CERR}$ . In correct mode (CORRECT pin active), it inverts (and hence corrects) the relevant bit in error of the Memory

Data word and provides the expected Data word for the EDAC controller.

If there is an error in the Memory Check-bit (MC[..]), only one bit of the syndrome is set to one.

In this case, the syndrome decoder sets low the correctable error flag  $\overline{CERR}$ , but  $\overline{NCERR}$  does not change. It does not correct the Check–bit because these bits are not used by the system.

29C516E

#### Table 6: Single Bit-Error

| MD[]                 | [15]            | [14]            | [13]            | [12]            | [11]            | [10]            | [9]             | [8]             | [7]             | [6]             | [5]             | [4]    | [3]             | [2]             | [1]             | [0]    |

|----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------|-----------------|-----------------|-----------------|--------|

| SY <sub>(hexa)</sub> | 34 <sub>h</sub> | 2A <sub>h</sub> | 29 <sub>h</sub> | 25 <sub>h</sub> | 32 <sub>h</sub> | 1A <sub>h</sub> | 16 <sub>h</sub> | 13 <sub>h</sub> | 31 <sub>h</sub> | 23 <sub>h</sub> | 15 <sub>h</sub> | $0B_h$ | 2C <sub>h</sub> | 1C <sub>h</sub> | 0E <sub>h</sub> | $0D_h$ |

| MC[]                 | [-]            | [-]            | [5]             | [4]             | [3]             | [2]             | [1]             | [0]             |

|----------------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| SY <sub>(hexa)</sub> | — <sub>h</sub> | — <sub>h</sub> | 20 <sub>h</sub> | 10 <sub>h</sub> | 08 <sub>h</sub> | 04 <sub>h</sub> | 02 <sub>h</sub> | 01 <sub>h</sub> |

#### 7.3. Double-Bit Error

If two errors occurs, there will be either 2, 4 or 6 bits set to one in the syndrome byte. The syndrome value generated by a double–bit error does not take place of a syndrome value generated by a single–bit error. Then, only the non correctable error flag NCERR will be activated to indicate that errors are present but cannot

be corrected.

Example: If MD[4] and MC[2] are incorrect, syndrome bits [0], [1], [2] and [3] are set to one (SY=0Fh),  $\overline{NCERR}$  is set low and  $\overline{CERR}$  remains at high level.

#### 7.4. Triple-Bit Error

Triple—Bit Error When three errors are detected, an error flag is set low as warning to the system. But the generated syndrome can have the listed value of single—bit error. The device must be in detect mode to prevent false correction occurring.

Example: If MD[0], MD[14] and MC[1] are corrupted,

the syndrome value is "25h". This is decoded by the 29C516E EDAC as being a correctable error on MD[12]. The  $\overline{CERR}$  flag is set low and correction would take place if the device is in correct mode. This would cause more errors.

### 7.5. 4-bit Wide Memory Error

The 6 check-bit code can be used to provide error detection for up to 4 errors occurring in the following groups: MD[15..12], MD[11..8], MD[7..4], MD[3..0], MC[5..3] and MC[2..0]. The 29C516E EDAC can flag any number of errors in 4-bit wide memory chip. A

special attention must be taken, multi-bit error (3) located into the defined groups can provide the syndrome byte of a single-bit error.

Example: If MD[3], MD[2], MD[1] and MD[0] are in error, the syndrome code is "33 h";

# 8. The 8-Bit Syndrome Word

This feature is available when the N22 pin is driven at a low level.

#### 8.1. No Errors

If there are no errors in the read Data or Check–Bit, all the syndrome byte is "00". The EDAC flags are inactive.

No Error: SY=00

#### 8.2. Single Bit-Error

Single Bit–Error A single bit–error in a Memory Data word read (MD[..]) causes three syndrome bits to be set to one. The code formed indicates which bit of the Memory Data word is incorrect.

For example, if MD[10] were incorrect, the syndrome byte would have bits 1, 3 and 4 set to one. The syndrome decoder of 29C516E EDAC decodes the information in the syndrome byte and only sets low the error flag  $\overline{\text{CERR}}$ . In correct mode (CORRECT pin active), it inverts (and hence corrects) the relevant bit in error of the Memory

Data word and provides the expected Data word for the EDAC controller.

If there is an error in the Memory Check-bit (MC[..]), only one bit of the syndrome is set to one.

In this case, the syndrome decoder sets low the correctable error flag  $\overline{CERR}$ , but  $\overline{NCERR}$  does not change. It does not correct the Check–bit because these bits are not used by the system.

#### **Table 7: Single Bit Error**

| MD[]                 | [15]            | [14]            | [13]            | [12]            | [11]            | [10]            | [9]             | [8]             | [7]             | [6]             | [5]             | [4]    | [3]             | [2]             | [1]             | [0]    |

|----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------|-----------------|-----------------|-----------------|--------|

| SY <sub>(hexa)</sub> | 34 <sub>h</sub> | 2A <sub>h</sub> | 29 <sub>h</sub> | 25 <sub>h</sub> | 32 <sub>h</sub> | 1A <sub>h</sub> | 16 <sub>h</sub> | 13 <sub>h</sub> | 31 <sub>h</sub> | 23 <sub>h</sub> | 15 <sub>h</sub> | $0B_h$ | 2C <sub>h</sub> | 1C <sub>h</sub> | 0E <sub>h</sub> | $0D_h$ |

| MC[]                 | [-]            | [-]            | [5]             | [4]             | [3]             | [2]             | [1]             | [0]             |

|----------------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| SY <sub>(hexa)</sub> | — <sub>h</sub> | — <sub>h</sub> | 20 <sub>h</sub> | 10 <sub>h</sub> | 08 <sub>h</sub> | 04 <sub>h</sub> | 02 <sub>h</sub> | 01 <sub>h</sub> |

#### 8.3. Double-Bit Error

If two errors occur, there will be 2, 3, 4, 5, 6 or 8 bits set to one in the syndrome byte. The syndrome value generated by a double—bit error does not take place of a syndrome value generated by a single—bit error. Then, only the non correctable error flag  $\overline{\text{NCERR}}$  will be

### 8.4. Triple-Bit Error

When three errors are detected, an error flag is set low as warning to the system. But the generated syndrome can have the listed value of single-bit error. The device must be in detect mode to prevent false correction occurrence. Example: If MD[0], MD[9] and MC[0] are corrupted, the syndrome value is "1Ah".

#### 8.5. 4-bit Wide Memory Error

The 8 check-bit code can be used to provide error detection for up to 4 errors occur in the following groups: MD[15..12], MD[11..8], MD[7..4], MD[3..0], MC[7..4] and MC[3..0]. The 29C516E EDAC can flag any number of errors in 4-bit wide memory chip.

#### 8.6. 8-bit Wide Memory Error

The 8 check-bit code can be used to provide error detection for up to 8 errors occurring in the following groups: MD[15..8], MD[7..0] and MC[7..0].

The 29C516E EDAC can flag any number of errors in 8-bit wide memory chip. A special attention must be taken, multi-bit error (3) located into the defined groups

#### 9. Transactions

Transactions Three types of transactions may be done:

#### 9.1. Memory Read

The TRANS pin is driven at a high level to select the access to the memory. The external arbiter drives the  $U2/\overline{U1}$  pin and dispatches the commands  $RD/\overline{WRx}$ ,

activated to indicate that errors are present but cannot be corrected.

Example: If MD[5] and MC[7] are incorrect, syndrome bits [0], [2], [4] and [6] are set to one (SY=55h), NCERR is set low and CERR remains at high level.

This is decoded by the 29C516E EDAC as being a correctable error on MD[10]. The CERR flag is set low and correction would take place if the device is in correct mode. This would cause more errors.

A special attention must be taken, multi-bit error (3) located into the defined groups can provide the syndrome byte of a single-bit error.

Example: If MD[11], MD[10], MD[9] and MD[8] are in error, the syndrome code is "AD h".

can provide the syndrome byte of a single-bit error. Example: If MD[13], MD[12], MD[10] and MD[9] are in error, the syndrome code is "40h". (In 6 check-bit coding, the syndrome code should have been "00h", the "No Error Detected" value.) Note that the syndrome code

"40 h" is also the code for MC[6] in error.

MEMx and ENx. All transaction managed by the master user can be listened by the second user.

#### Table 8:

| TRANS | $\overline{\mathrm{U2/\overline{U1}}}$ | CORRECT | SYNCHIK | RD/WR1 | EN1 | <u>MEM1</u> | RD/WR2 | EN2 | MEM2 | CERR | NCERR | Function                                          |

|-------|----------------------------------------|---------|---------|--------|-----|-------------|--------|-----|------|------|-------|---------------------------------------------------|

|       |                                        |         |         |        |     |             |        |     |      | 1    | 1     | UD1[015] = MD[015]                                |

|       |                                        | 1       | 1       | 1      | 0   | 0           | x      | x   | X    | 0    | 1     | $UD1[015] = \{corrected MD[015]\}$                |

|       |                                        |         |         |        |     |             |        |     |      | X    | 0     | $UD1[015] = \{corrupted MD[015]\}$                |

| 1     | 0                                      | 0       | 1       | 1      | 0   | 0           | x      | x   | x    | x    | x     | UD1[015] = MD[015]                                |

| 1     | U                                      | X       | 0       | 1      | U   | U           | Λ.     | Λ.  | Λ    | Λ.   | Λ     | $UD1[015] = \{MC[07]   Syndrome\}$                |

|       |                                        |         |         | 1      | 1   | X           | x      | x   | x    | x    | x     | UD1[015] = H.Z                                    |

|       |                                        | X       | x       | 1      | X   | 1           | Х      | Х   | X    | Х    | A     |                                                   |

|       |                                        |         |         | 1      | X   | X           | 1      | 0   | 0    | X    | X     | UD2[015] = {expected UD1[015]} (User 2 listening) |

|       |                                        |         |         |        |     |             |        |     |      | 1    | 1     | UD2[015] = MD[015]                                |

|       |                                        | 1       | 1       | x      | x   | X           | 1      | 0   | 0    | 0    | 1     | $UD2[015] = \{corrected MD[015]\}$                |

|       |                                        |         |         |        |     |             |        |     |      | X    | 0     | $UD2[015] = \{corrupted MD[015]\}$                |

| 1     | 1                                      | 0       | 1       | x      | x   | x           | 1      | 0   | 0    | x    | х     | UD2[015] = MD[015]                                |

| 1     | 1                                      | X       | 0       | X      | A   | Х           | 1      | U   | U    | Х    | A     | $UD2[015] = \{MC[07]   Syndrome \}$               |

|       |                                        |         |         | x      | x   | x           | 1      | 1   | X    | X    | x     | UD2[015] = H.Z                                    |

|       |                                        | X       | x       | X      | , x | Α           | 1      | X   | 1    |      | Α     |                                                   |

|       |                                        |         |         | 1      | 0   | 0           | 1      | X   | X    | X    | Х     | UD1[015] = {expected UD2[015]} (User 1 listening) |

x : don't care

# 9.2. Memory Write

The TRANS pin is driven at a high level to select the access to the memory. The external arbiter drives the  $U2/\overline{U1}$  pin and dispatches the commands  $RD/\overline{WRx}$ ,

$\overline{MEMx}$  and  $\overline{ENx}$ . All transaction managed by the master user can be listened by the second user.

Table 9:

| TRANS | U2/ <u>U1</u> | RD/WR1 | EN1 | MEM1 | RD/WR2 | EN2 | MEM2 | Function                                                            |

|-------|---------------|--------|-----|------|--------|-----|------|---------------------------------------------------------------------|

|       |               | 0      | 0   | 0    | X      | x   | x    | MD[015] = UD1[015]<br>MC[07] = {check-bits generated from UD1[015]} |

| 1     | 0             | 0      | 1   | X    | х      | x   | x    | MD[015] = H.Z                                                       |

|       |               | U      | X   | 1    | A      | Х   | Х    | MC[07] = H.Z                                                        |

|       |               | 0      | X   | X    | 1      | 0   | 0    | UD2[015] = UD1[015] (User 2 listening)                              |

|       |               | х      | х   | X    | 0      | 0   | 0    | MD[015] = UD2[015]<br>MC[07] = {check-bits generated from UD2[015]} |

| 1     | 1             |        |     |      | 0      | 1   |      | MD[015] = H.Z                                                       |

|       |               | X      | Х   | X    | U      | X   | 1 MC | MC[07] = H.Z                                                        |

|       |               | 1      | 0   | 0    | 0      | X   | X    | UD1[015] = UD2[015] (User 1 listening)                              |

x : don't care

$\overline{CERR}$  and  $\overline{NCERR}$  are not valid

CORRECT and  $\overline{\mbox{SYNCHK}}$  are not active

### 9.3. User to User Transfer

The TRANS pin is driven at a low level to select this mode. The external arbiter drives the  $U2/\overline{U1}$  pin and  $\overline{MEMx}$  and  $\overline{ENx}$ .

**Table 10:**

| TRANS | U2/ <u>U1</u> | RD/WR1 | EN1 | MEMI | RD/WR2 | EN2 | MEM2 | Function            |

|-------|---------------|--------|-----|------|--------|-----|------|---------------------|

|       | 0             | 1      | 0   | 1    | X      | X   | X    | UD1[015] = UD2[015] |

| 0     |               |        | 1   | X    | x      | x   | x    | UD1[015] = H.Z      |

|       |               |        | X   | 0    | Α      | A   | , x  |                     |

|       |               |        | 0   | 1    | X      | X   | X    | UD2[015] = UD1[015] |

|       |               | 0      | 1   | X    |        |     | х    | UD2[015] = H.Z      |

|       |               |        | Х   | 0    | X      | X   | X    |                     |

|       | 1             | x      | x   | x    | 1      | 0   | 1    | UD2[015] = UD1[015] |

|       |               |        |     |      |        | 1   | x    | UD2[015] = H.Z      |

| 0     |               |        |     |      |        | Х   | 0    |                     |

|       |               |        |     |      | 0      | 0   | 1    | UD1[015] = UD2[015] |

|       |               |        |     |      |        | 1   | Х    | UD1[015] = H.Z      |

|       |               |        |     |      |        | X   | 0    |                     |

x : don't care

CERR and NCERR are not valid

CORRECT and  $\overline{\mbox{SYNCHK}}$  are not active

# 10. Signal Timing

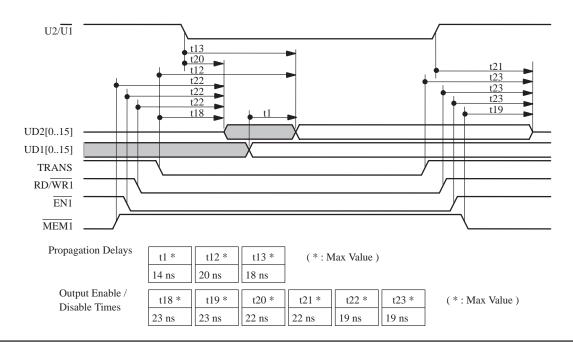

### 10.1. Memory Write

**Figure 4.Memory Write Timing Diagram**

**Figure 5.Transfer Write Timing Diagram**

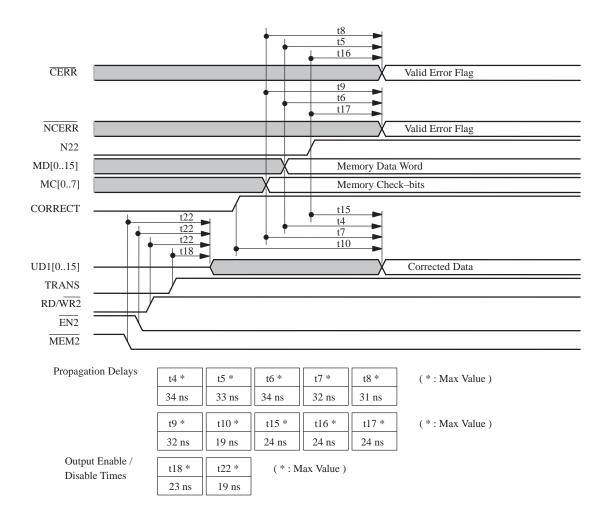

# 10.2. Memory Read

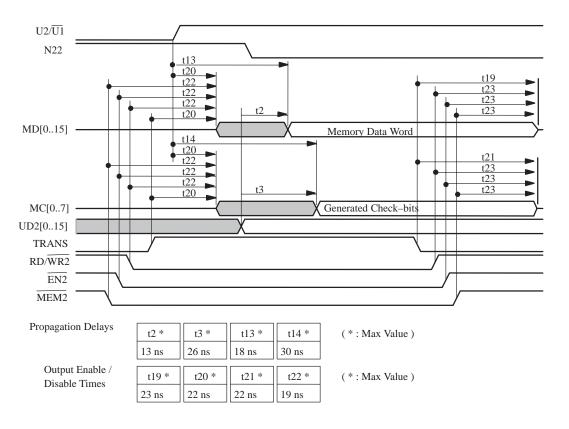

#### Figure 6.Memory Read Timing Diagram

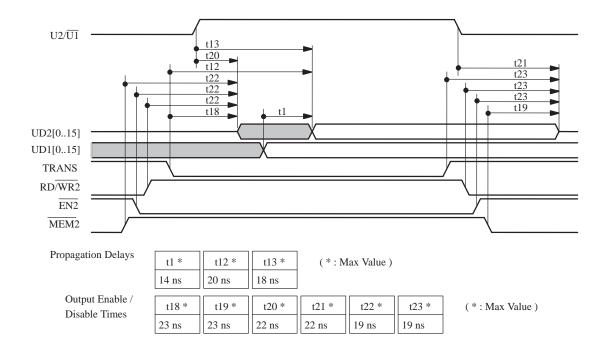

### 10.3. Transfer Read

Figure 7.Transfer Read Timing Diagram

### 11. Electrical Characteristics

# 11.1. Absolute Maximum Ratings

Table 11:

| Parameter                                                | Value               |  |  |

|----------------------------------------------------------|---------------------|--|--|

| Supply voltage, Vcc                                      | - 0.5 to 7V         |  |  |

| Input voltage range                                      | -0.5 to Vcc + 0.5 V |  |  |

| Input current per power pin                              | +/- 50 mA           |  |  |

| Input current per signal pin                             | +/- 10 mA           |  |  |

| Continuous output current, one pin                       | +/- 30 mA           |  |  |

| Soldering lead temperature 1.6 mm from case for max 10 s | + 300 °C            |  |  |

| Storage temperature                                      | − 65 °C to + 150 °C |  |  |

| Maximum package power dissipation                        | 1.0 W               |  |  |

# 11.2. Operating Conditions

### **Table 12:**

| Parameter                   | Min  | Тур | Max | Unit |

|-----------------------------|------|-----|-----|------|

| Supply voltage, Vcc         | 4.5  | 5.0 | 5.5 | Volt |

| Operating temperature range | - 55 |     | 125 | °C   |

### 11.3. Static Electrical Characteristics

### **Table 13:**

| Parameter     |                                             | Condition                                                                                              | Min.    | Тур  | Max   | Unit |

|---------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------|---------|------|-------|------|

| VIH           | High level input voltage                    |                                                                                                        | 2,2     |      |       | V    |

| VIL           | Low level input voltage                     |                                                                                                        |         |      | 0,8   | V    |

| <b>V</b> OH1  | High level output voltage                   | IOH = $-20  \mu A$                                                                                     | Vcc-0.1 |      |       | V    |

| Vol1          | Low level output voltage                    | $IOL = +20 , \mu A$                                                                                    |         |      | 0,1   | V    |

| VOH2          | High level output voltage                   | <b>I</b> OH = - 12.8 mA                                                                                | 3,7     |      |       | V    |

| VOL2          | Low level output voltage                    | <b>I</b> OL = + 12.8 mA                                                                                |         |      | 0,4   | V    |

| IIL           | Low level input current                     | Vin = Gnd                                                                                              | - 10    | - 1  |       | μΑ   |

| <b>I</b> ILP  | Low level input current, (Pull-up Input)    | Vin = Gnd                                                                                              | - 100   | - 40 |       | μΑ   |

| <b>I</b> IH   | High level input current                    | Vin = Vcc                                                                                              |         | + 1  | + 10  | μΑ   |

| <b>I</b> IHP  | High level input current, (Pull-down Input) | Vin = Vcc                                                                                              |         | + 40 | + 100 | μΑ   |

| Ioz           | Output leakage current                      | Outputs disable,<br>(Gnd <vout<vcc)< td=""><td>- 10</td><td></td><td>+ 10</td><td>μΑ</td></vout<vcc)<> | - 10    |      | + 10  | μΑ   |

| IOZLP         | Output leakage current, (Pull-up Input)     | Outputs disable,<br>(Vout=Gnd)                                                                         | - 100   | - 40 |       | μΑ   |

| <b>I</b> OZHP | Output leakage current, (Pull-down Input)   | Outputs disable, (Vout=Vcc)                                                                            |         | +40  | + 100 | μΑ   |

| CI            | Input pin capacitance                       |                                                                                                        |         |      | 8     | pF   |

| Cio           | I/O pin capacitance                         |                                                                                                        |         |      | 12    | pF   |

| ICCSB         | Standby supply current                      |                                                                                                        |         | + 10 | + 20  | μΑ   |

# 12. Ordering information