**TOSHIBA** TD6338P

TOSHIBA BIPOLAR DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TD6338P

## BI-CMOS 10 BIT SERIAL-INPUT/PARALLEL OUTPUT DRIVER

The TD6338P is an IC built using a Bi-CMOS process characterized by high output withstand voltage. It contains a serial-input, 10-stage parallel-output shift register and latches as well as a bipolar 10-stage parallel output driver.

It also has a serial output which facilitates output expansion.

#### **FEATURES**

- Serial input and 10-stage parallel/serial output

- Serial output allows cascade expansion.

- DISABLE input for output control

- High output withstand voltage : ≧ 60V

- Wide operating temperature range : Ta = -40 to  $85^{\circ}C$

Weight: 1.4g (Typ.)

#### PIN LAYOUT

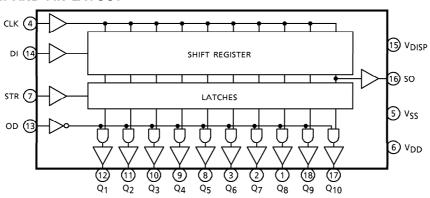

#### **BLOCK DIAGRAM AND PIN LAYOUT**

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade control laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

#### **PIN DESCRIPTION**

| PIN No.                       | SYMBOL                                                                                                    | DESCRIPTION                                                                                                                           |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 12 to 8<br>3 to 1<br>18 to 17 | Q <sub>1</sub> ~Q <sub>10</sub>                                                                           | Parallel output pins which supply shift register output when the strobe input (STR) is high and the output disable input (OD) is low. |  |  |

| 4                             | CLK                                                                                                       | Clock input pin for shift register. The shift register becomes active on the leading edge of the clock.                               |  |  |

| 5                             | Vss                                                                                                       | Grounded.                                                                                                                             |  |  |

| 6                             | $V_{DD}$                                                                                                  | Power supply pin                                                                                                                      |  |  |

| 7                             | STR                                                                                                       | When this signal is low, data is held; when it is high, data is rewritten.                                                            |  |  |

| 13                            | OD Output disable input pin. When this signal is low, data is output; when high, all outputs are set low. |                                                                                                                                       |  |  |

| 14                            | DI                                                                                                        | Serial data input pin                                                                                                                 |  |  |

| 15                            | V <sub>DISP</sub>                                                                                         | Power supply pin for parallel output                                                                                                  |  |  |

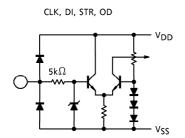

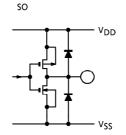

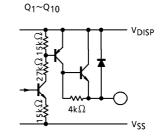

#### I/O CIRCUIT DIAGRAM

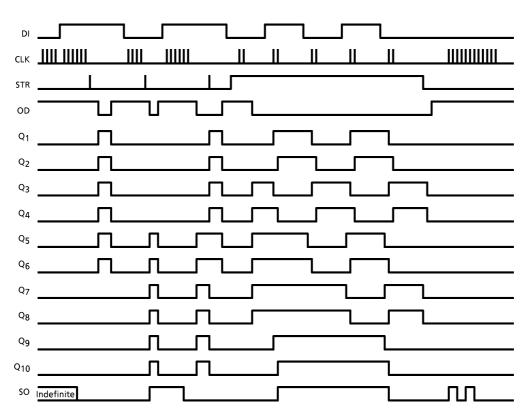

#### **OUTLINE OF FUNCTIONS**

The circuit consists of a 10-stage D-type flip-flop and ten latches and buffers connected to the outputs of the flip-flop.

Suppose that data is fed to the serial data input (DI) pin and clock pulses are supplied to the clock input (CLK) pin. When the clock changes from low to high, the data enters the shift register, and the data in the shift register shifts at the same time.

Shift register data is output at the parallel output pins when the strobe input (STR) is high and the output disable input (OD) is low.

When the strobe input is set low, the contents of the latches are held regardless of the contents of the shift register.

The serial data output (SO) pin supplies a signal with the same polarity as the parallel outputs. When multiple TD6338Ps are used for output expansion, the serial data output (SO) of one TD6338P is connected to the serial data input (DI) of the next-stage TD6338P.

When the output disable input (OD) is set high, the outputs  $Q_1$  to  $Q_{10}$  become low. At the time of power-on, set the OD input high so that the outputs  $Q_1$  to  $Q_{10}$  will be kept low until input data is set to determine the internal logic state.

#### **TIMING CHART**

## **VOLTAGE WAVEFORM**

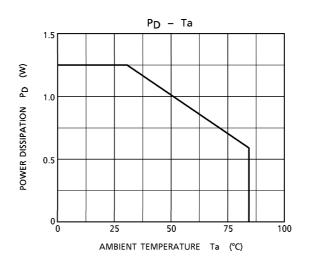

## **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL            | TEST CONDITION                                 | RATING                          | UNIT |  |

|-----------------------|-------------------|------------------------------------------------|---------------------------------|------|--|

| Display Voltage       | V <sub>DISP</sub> | _                                              | 65                              | V    |  |

| Supply Voltage        | V <sub>DD</sub>   | _                                              | -0.3 to 15                      | V    |  |

| Output Voltage        | \/                | SO Output                                      | -0.3 to V <sub>DD</sub> + 0.3   | \ \  |  |

| Output Voltage        | Vout              | Q <sub>1</sub> to Q <sub>10</sub> : Output off | -0.3 to V <sub>DISP</sub> + 0.3 | "    |  |

| Output Current        | lout              | Q <sub>1</sub> to Q <sub>10</sub> : Output on  | - 40                            | mA   |  |

| Input Voltage         | VIN               | _                                              | -0.3 to V <sub>DD</sub> + 0.3   | V    |  |

| Power Dissipation     | PD                | _                                              | 1.25                            | W    |  |

| Operating Temperature | Topr              | _                                              | -40 to 85                       | °C   |  |

| Storage Temperature   | T <sub>stg</sub>  | _                                              | - 55 to 150                     | °C   |  |

### **RECOMMENDED CONDITIONS**

| CHARACTERISTIC | SYMBOL           | TEST CONDITION                                                                     | MIN. | TYP. | MAX. | UNIT |

|----------------|------------------|------------------------------------------------------------------------------------|------|------|------|------|

| Supply Voltage | $V_{DD}$         | _                                                                                  | 4    | 5    | 6    | V    |

| Output Voltage | ٧o               | Q <sub>1</sub> to Q <sub>10</sub> : Output off                                     | _    | _    | 55   | ٧    |

| Output Current | I <sub>OUT</sub> | Current per circuit Q <sub>1</sub> to Q <sub>10</sub> : Output on at the same time | _    | 15   | _    | mA   |

## DC ELECTRICAL CHARACTERISTICS (Ta = -40 to 85°C, $V_{DD} = 5V$ , $V_{DISP} = 55V$ )

| CHARACTERISTIC        | SYMBOL          | TEST<br>CIR-<br>CUIT | TEST CONDITION               | MIN.  | TYP. | MAX. | UNIT     |

|-----------------------|-----------------|----------------------|------------------------------|-------|------|------|----------|

| Input Voltage         | V <sub>IH</sub> | _                    | _                            | 3.4   |      | _    | V        |

| Imput voltage         | V <sub>IL</sub> | _                    | _                            | _     | 1    | 1.1  | <b>'</b> |

| land Comment          | lіН             | _                    | V <sub>IH</sub> = 3.4V       | _     |      | 20   |          |

| Input Current         | IIL             | _                    | V <sub>IL</sub> = 1.1V       | _     | _    | 5    | $\mu$ A  |

| Output Voltage        | Voн             | _                    | $I_{OH} = 20 \mu A$ , SO     | 4.3   | _    | _    | v        |

| Output Voltage        | VOL             | _                    | $I_{OL} = 20 \mu A$ , SO     | _     | _    | 0.7  | <b>'</b> |

| Output Current        | IOH             | _                    | V <sub>OH</sub> = 4.5V, SO   | - 100 | _    | _    |          |

| Output Current        | lOL             | _                    | V <sub>OL</sub> = 0.5V, SO   | 300   | _    | _    | $\mu$ A  |

| Output Valtage        | Voн             | _                    | I <sub>OH</sub> = - 15mA, QN | 52.5  | _    | _    | V        |

| Output Voltage        | VOL             | _                    | $R_{OUT} = 15k\Omega$ , QN   | _     | _    | 1.5  | <b>'</b> |

| Command Canadanandian | IDISP           | _                    | All output circuits off      | _     |      | 6.0  | A        |

| Current Consumption   | l <sub>DD</sub> | _                    | All output circuits off      | _     | _    | 10.0 | mA       |

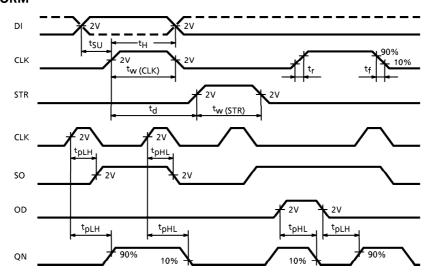

AC ELECTRICAL CHARACTERISTICS (Ta = -40 to  $85^{\circ}$ C,  $V_{DD} = 4$  to 6V,  $V_{DISP} = 55V$ )

|                       |                          |                      | ונוטי ייי טטי ייי                       |      |      |      |         |

|-----------------------|--------------------------|----------------------|-----------------------------------------|------|------|------|---------|

| CHARACTERISTIC        | SYMBOL                   | TEST<br>CIR-<br>CUIT | TEST CONDITION                          | MIN. | TYP. | MAX. | UNIT    |

| Clock Pulse Frequency | f (CLK)                  | _                    | Input duty: 40 to 60%                   | _    | _    | 800  | kHz     |

| Clock Pulse Width     | <sup>t</sup> w (CLK)     | _                    | _                                       | 500  | _    | _    | ns      |

| Strobe Pulse Width    | <sup>t</sup> w (STR)     | _                    | _                                       | 600  | _    | _    | ns      |

| Data Setup Time       | tsu                      | _                    | _                                       | 150  | _    | _    | ns      |

| Data Hold Time        | tH                       | _                    | _                                       | 400  | _    | _    | ns      |

| Clock Latch Time      | <sup>t</sup> d (CLK-STR) | _                    | _                                       | 1.5  | _    | _    | $\mu$ s |

| Clock Pulse Rise Time | <sup>t</sup> r (CLK)     | _                    | _                                       | _    | _    | 500  | ns      |

| Clock Pulse Fall Time | tf (CLK)                 | _                    | _                                       | _    | _    | 500  | ns      |

|                       | t <sub>pLH</sub>         | _                    | From input CLK to output SO             | _    | _    | 2.0  |         |

|                       | t <sub>pHL</sub>         |                      | $R_{L (SO)} = \infty$ , $C_{L} = 15pF$  | _    | _    | 2.0  |         |

| Transfer Delay Time   | t <sub>pLH</sub>         |                      | From input CLK to output QN             |      | _    | 3.0  | $\mu$ s |

|                       | t <sub>pHL</sub>         |                      | $R_{L(QN)} = 2k\Omega$ , $C_{L} = 15pF$ | _    | _    | 7.0  |         |

|                       | t <sub>pLH</sub>         |                      | From input OD to output QN              | _    | _    | 6.0  |         |

|                       | t <sub>pHL</sub>         |                      | $R_{L(QN)} = 2k\Omega$ , $C_{L} = 15pF$ | _    | _    | 2.0  |         |

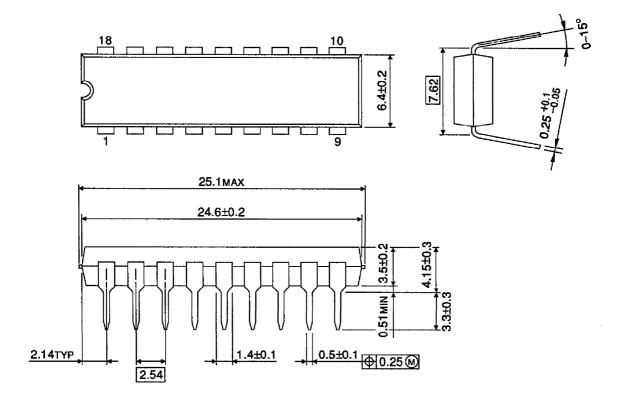

#### OUTLINE DRAWING DIP18-P-300-2.54D

Unit: mm

Weight: 1.4g (Typ.)