# **HA16640NT**

Preliminary February 1985

## Write/Mechanism Controller for Floppy Disk Drive

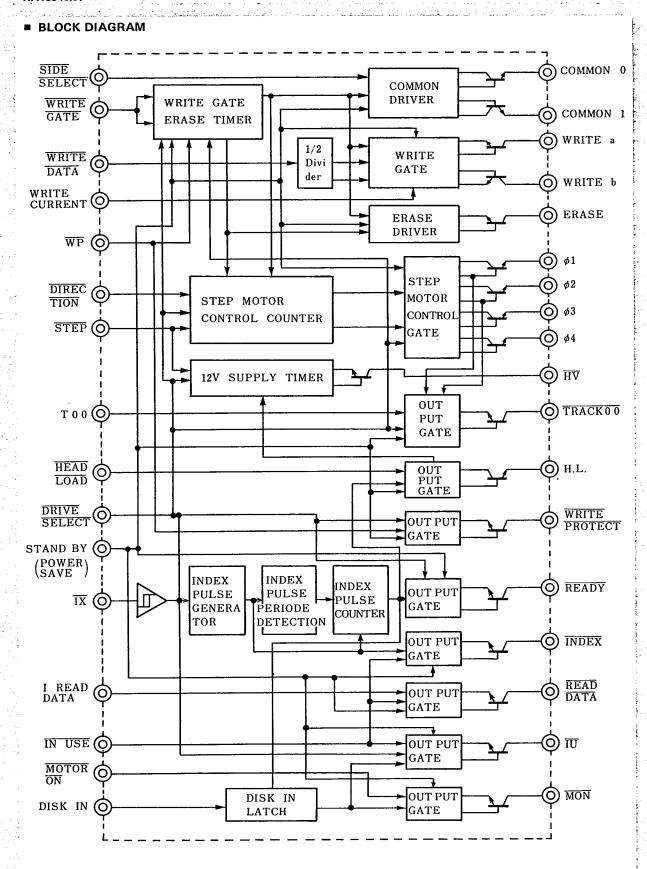

This IC can provide WRITE + MECHANISM CONTROL function is one chip for FLOPPY DISK DRIVE

#### **■ FEATURES**

- WRITE Circuit includes COMMON, WRITE, ERASE drivers, and has capability of application for many kind of FDD.

- WRITE Circuit also includes tripple power supply monitor circuits, so can protect the Disk from abnormal writing or erasing at ON, OFF of supply voltage.

- The delay time between write gate and erase gate timing is generated by internal MONO MULTI Circuit, so this IC is able to apply for many kind of FDD and HEAD component.

- The function of MECHANISM CONTROL circuit conforms to the standard FDD's interface.

- MECHANISM CONTROL Circuit has a power save function, and at the stand-by mode in operation, power save circuit protects the equipment from internal temperature increasing by inhibiting the load current in external components, and also reduces the power dissipation in IC chip.

- The output interface has capability of large drive current, and internal logic circuit has low power consumption by means of Bi-CMOS technology. Especially, in the output interface circuit, it is not necessary to have any external TTL ICs because of including line drivers into IC chip.

- With this device, it is able to design the print circuit board without TTL ICs, and to reduce many external components, also to shrink an area of print circuit board.

- Signal processing and control circuit in FDD are able to be constructed with only two ICs and some external discrete devices by connecting with FDD READ IC, HA16631P/MP.

<sup>\*</sup> In the WRITE CIRCUIT, power supply monitor circuits are included to watch the Line Voltage of 5V and 12V. When the line voltage goes down to abnormal value, the COMMON, WRITE, ERASE drivers are all inhibited rapidly.

#### **ABSOLUTE MAXIMUM RATING** $(T_a = 25^{\circ}C)$

T-52-33-11

| Item                                            | Symbol           | Ratings                  | Unit | Applicable Terminal |

|-------------------------------------------------|------------------|--------------------------|------|---------------------|

| Supply Voltage                                  | $V_{DD1}$        | -0.3 to +7.0             | v    | $V_{DD1}$           |

| Supply Voltage                                  | $V_{DD2}$        | -0.3 to +14.0            | v    | $V_{DD2}$           |

| Interface Input Voltage                         | V <sub>IN1</sub> | -0.3 to V <sub>DD1</sub> | v    | Note 1              |

| Interface Input Voltage                         | $V_{IN2}$        | -0.3 to V <sub>DD2</sub> | · v  | Note 2              |

| Interface Output Current                        | $I_{OL1}$        | 50                       | mA   | Note 3              |

| IU Terminal Output Current                      | $I_{OL2}$        | 20                       | mA   | IU                  |

| HV Terminal Output Current                      | $I_{OL3}$        | 15                       | mA   | HV                  |

| MON Terminal Output Current                     | $I_{OL4}$        | 5                        | mA   | MON                 |

| HL Terminal Output Current                      | $I_{OH5}$        | 10                       | mA   | HL                  |

| STEP Terminal Output Current                    | I <sub>OH6</sub> | 5                        | mA   | φ1 φ2 φ3 φ4         |

| COMMON Drive Current (WRITE MODE)               | Iocw             | 100                      | mA   | COMMON φ.1.         |

| COMMON Drive Current (READ MODE)                | IOCR             | 5                        | mA   | COMMON φ.1.         |

| WRITE Drive Current                             | IOWW             | 15                       | mA   | WRITE a,b           |

| ERASE Drive Current                             | IOEW             | 85                       | mA   | ERASE               |

| Input Current on the WRITE Current Set Terminal | I <sub>WC</sub>  | 3.75                     | mA   | WRITE CURRENT       |

| Power Dissipation                               | $P_D$            | 850<br>(0 to 50°C)       | mW   |                     |

| Operating Temperature Range                     | TOP              | 0 to +70                 | °C   |                     |

| Storage Temperature Range                       | T <sub>stg</sub> | 55 to +125               | °C   |                     |

Notes 1. Applicable Terminal: SIDE SELECT, WRITE DATA, STEP, DIRECTION, IN USE, MOTOR ON, HEAD LOAD, STAND BY, WRITE GATE, DRIVE SELECT, IREAD DATA

2. Applicable Terminal: T00, DISK IN, WP, IX and also Terminals from MM Circuit connecting with the external C,R

3. Except for IU, HV, MON, HL, φ1 φ2 φ3 φ4.

## ■ ELECTRICAL CHARACTERISTICS (Ta = 25°C)

|               | Circuit Block        | Item                                                  | Test Condition                                                   | Symbol             | min      | typ      | max  | Unit |

|---------------|----------------------|-------------------------------------------------------|------------------------------------------------------------------|--------------------|----------|----------|------|------|

|               | Supply Voltage       | Supply Voltage Range                                  |                                                                  | $V_{DD1}$          | 4.5      | 5.0      | 5.5  | V    |

|               |                      | Supply Voltage Range                                  |                                                                  | $V_{DD2}$          | 10.8     | 12.0     | 13.2 | V    |

|               | COMMON<br>Driver     | Output Voltage at<br>Selected WRITE Mode              | $V_{DD2} = 12V$ $I_{OCW} = -100 \text{mA}$                       | Vocw               | _        | 10.7     | -    | v    |

|               |                      | Output Voltage at<br>Unselected WRITE Mode            | V <sub>DD2</sub> = 12V<br>Unselected                             | Vocwu              | _        | -        | 0.7  | v    |

|               |                      | Output Voltage at<br>Selected READ Mode               | $V_{DD2} = 12V$ $I_{COR} = -5mA$                                 | VOCR               | -        | 4.7      | _    | v    |

|               |                      | Output Voltage at<br>Unselected READ Mode             | $V_{DD2} = 12V$<br>Unselected                                    | Vocru              | -        | _        | 0.7  | v    |

|               |                      | Output Current Range                                  |                                                                  | I <sub>COM</sub>   | -        | _        | 100  | mA   |

| ij            | WRITE<br>Driver      | Input Current Range on the WRITE Current set Terminal |                                                                  | I <sub>WC</sub>    | 0        | _        | 2.5  | mA   |

| WRITE Circuit |                      | WRITE Current Accuracy                                | WRITE Driver output Voltage = 10V $I_{WC} = 1 \text{mA}$         | I <sub>OWW</sub>   | 3.6      | 4.0      | 4.4  | mA   |

| WR            |                      | WRITE Current Temperature Coefficient                 | $I_{WC} = 1 \text{mA}$ $T_a = 0 \text{ to } 70^{\circ} \text{C}$ | TCIOW              | -        | ±0.05    | -    | %/°C |

|               |                      | WRITE Current Symmetry                                | $V_{DD1} = 5V,$<br>$V_{DD2} = 12V$<br>$I_{owa}I_{owb}$           | $\Delta I_{OW}$    | -1       | <u>-</u> | +1   | %    |

|               |                      | Leak Current                                          | $V_{DD1} = 5V,$ $V_{DD2} = 12V$ $V_{OW} = 20V$                   | $I_{LKW}$          | _        | _        | 100  | μА   |

|               | ERASE<br>Driver      | Output Low<br>Voltage                                 | $V_{DD1} = 4.5 \text{V}$ $I_{OE} = 80 \text{mA}$                 | V <sub>OLER</sub>  | <u> </u> | -        | 0.6  | v    |

|               |                      | Output Leak Current                                   | $V_{DD1} = 5.5 \text{V}$<br>$V_{OER} = 20 \text{V}$              | ILKER              | _        | _        | 200  | μА   |

|               | Lower Line           | 12V Detection Voltage                                 |                                                                  | V <sub>PRV12</sub> | -        | 8.1      | _    | V    |

|               | Voltage<br>Protector | 5V Detection Voltage                                  |                                                                  | V <sub>PRV5</sub>  | ] -      | 3.8      |      | v    |

|                           | Circuit Block                   | Item                         | Test Condition                                      | Symbol            | min            | typ  | max      | Unit     |

|---------------------------|---------------------------------|------------------------------|-----------------------------------------------------|-------------------|----------------|------|----------|----------|

|                           | Signal                          | High Level Input Voltage     | $V_{DD1} = 5.0 \text{V}$                            | $V_{IHI}$         | 2.4            | _    | -        | V        |

|                           | Interface<br>(Note 1)           | Low Level Input Voltage      | $V_{DD1} = 5.0 \text{V}$                            | $V_{ILI}$         | -              | _    | 0.8      | V        |

|                           | Signal<br>Interface<br>(Note 1) | High Level Input Current     | $V_{DD1} = 5.5 \text{V}$ $V_{IH} = 5.5 \text{V}$    | $I_{HI}$          |                | -    | 10       | μА       |

| .                         |                                 | Low Level Input Current      | $V_{DD1} = 5.5V$ $V_{IL} = 0V$                      | $I_{ILI}$         | -10            | _    | _        | μА       |

| <b>E</b>                  |                                 | High Level Input Voltage     | $V_{DD1} = 5.0 \text{V}$                            | $V_{IHS}$         | 3.3            |      | _        | v        |

| 3                         |                                 | Low Level Input Voltage      | $V_{DD1} = 5.0 \text{V}$                            | $V_{ILS}$         | -              |      | 1.7      | V        |

| WRITE Circuit             | Sensor<br>Interface<br>(Note 2) | High Level Input Current     | $V_{DD1} = 5.5V$ $V_{IH} = 5.5V$                    | $I_{IHS}$         |                | _    | 10       | μА       |

| <b>≩</b>                  | (110.00 2)                      | Low Level Input Current      | $V_{DD1} = 5.5 \text{V}$ $V_{IL} = 0 \text{V}$      | $I_{ILS}$         | -10            |      | -        | μА       |

|                           | 71                              | Higher Threshold Voltage     | $V_{DD1} = 5V$                                      | V <sub>THIX</sub> | _              | 3.5  |          | V        |

|                           | Index                           | Lower Threshold Voltage      | $V_{DD1} = 5V$                                      | $V_{THIX}$        |                | 2.0  | <u> </u> | V        |

|                           | Input<br>Interface              | Hysterisis                   | $V_{DD1} = 5V$                                      | $V_{HYS}$         | _              | 1.5  |          | V        |

|                           | Interrace                       | Input Current                | $V_{DDI} = 4.5 \text{V}$<br>$V_{IH} = 2.6 \text{V}$ | I <sub>IHIX</sub> | -80            |      | 100      | μА       |

|                           | Signal<br>Output                | Low Level Output<br>Voltage  | $V_{DD1} = 4.5V$ $I_{OL} = 48mA$                    | V <sub>OLI</sub>  | _              | -    | 0.4      | v        |

|                           | Interface                       | High Level Output Current    | $V_{DD1} = 5.5V$ $V_{OH} = 5.5V$                    | I <sub>OHI</sub>  | _              | -    | 250      | μΑ       |

|                           | IU Output                       | Low Level Output<br>Voltage  | $V_{DDI} = 4.5V$ $I_{OL} = 10 \text{mA}$            | VOLIU             | _              |      | 0.5      | v        |

|                           |                                 | High Level Output Current    | $V_{DD1} = 5.5V$ $V_{OH} = 5.5V$                    | Іоніи             | _              | -    | 100      | μА       |

|                           | HV Output                       | Low Level Output<br>Voltage  | $V_{DDI} = 4.5V$ $I_{OL} = 15 \text{mA}$            | V <sub>OLHV</sub> | -              |      | 0.5      | v        |

|                           |                                 | High Level Output Current    | $V_{DD1} = 5.5V$ $V_{OH} = 13.2V$                   | $I_{OHHV}$        | -              | _    | 100      | μА       |

|                           |                                 | Low Level Output             | $V_{DD1} = 4.5 V$                                   | V                 | <del> </del>   |      | 0.4      | v        |

| Mechanism Control Circuit | MON Output                      | Voltage                      | $I_{OL} = 5 \text{mA}$                              | V <sub>OLMN</sub> | ļ <del>-</del> |      | 0.4      | <u> </u> |

|                           |                                 | High Level Output Current    | $V_{DD1}$ = 5.5V<br>$V_{OH}$ = 5.5V                 | I <sub>OHMN</sub> |                |      | 50       | μА       |

|                           | HL Output                       | High Level Output Voltage    | $V_{DD1} = 5V$ $I_{OH} = -10$ mA                    | VOHHL             | 3.6            | _    | -        | V        |

| THO?                      |                                 | Low Level Output Current     | $V_{DD1} = 5.5 \text{V}$<br>$V_{OL} = 0 \text{V}$   | IOLHL             | -20            | -    | _        | μА       |

| msnu<br>Msnu              | STEP<br>Output                  | High Level<br>Output Voltage | $V_{DD1} = 5V$ $I_{OH} = -5 \text{mA}$              | VOHSTP            | 3.6            | -    | -        | v        |

| lecha:                    |                                 | Low Level Output Current     | $V_{DD1} = 5.5 \text{V}$ $V_{OL} = 0 \text{V}$      | IOLSTP            | -20            | _    | _        | μА       |

| 4                         | ERASE<br>Timer                  | ERASE ON DELAY               | $Cex = 0.034 \mu F$ $Rex = 33k\Omega$               | t <sub>EN</sub>   | 0.42           | 0.50 | . 0.58   | ms       |

|                           |                                 | ERASE OFF DELAY              | $Cex = 0.069 \mu F$ $Rex = 33k\Omega$               | $t_{EF}$          | 0.86           | 1.02 | 1.18     | ms       |

|                           | INDEX,<br>READY<br>Circuit      | Index Pulse Width            | $Cex = 0.033\mu F$ $Rex = 220k\Omega$               | t <sub>IXW</sub>  | 2.61           | 3.08 | 3.55     | ms       |

| -                         |                                 | Index Detection Period       | Cex = 0.22μF<br>Rex = 390kΩ                         | t <sub>IXI</sub>  | 31.1           | 36.6 | 42.1     | ms       |

|                           | 12V Hold                        | Hold Period                  | $Cex = 2.3 \mu F$ $Rex = 56 kΩ$                     | t <sub>HV</sub>   | 47.1           | 55.5 | 63.9     | ms       |

|                           | Dissipation Current             | at 12V Supply Current 1      | $V_{DD1} = 5.5V,$ $V_{DD2} = 13.2V$ No Load         | $I_{DD1}$         | -              | -    | 65       | mA       |

|                           |                                 | Supply Current 2             | $V_{DD1} = 5.5V,$<br>$V_{DD2} = 13.2V$<br>No Load   | $I_{DD2}$         | -              | _    | 10       | mA       |

T-52-33-11

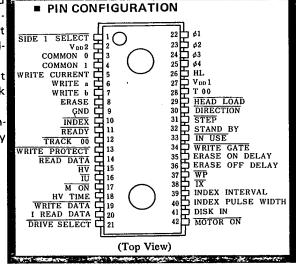

#### ■ Pin Description

| Symbol                            | Name                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СОМ 0                             | Common<br>Driver 0                    | Output terminal of Common Driver (SIDE 0). During the Head Select signal is selecting SIDE 0, a common voltage appears on this terminal. The voltage value at WRITE Mode and that READ Mode are shown in the Electrical Characteristics. This terminal supplies a current which equals to write current + erase current. When the SIDE 0 is unselected, a common voltage doesn't appear, and this terminal is pulled down to ground by a internal resistor with high resistance.    |

| COM 1                             | Common<br>Driver 1                    | Output terminal of Common Driver. (SIDE 1). The function is as same as that of SIDE 0.                                                                                                                                                                                                                                                                                                                                                                                              |

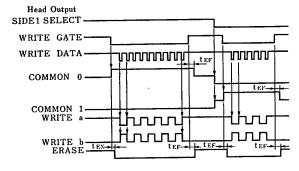

| SIDE<br>SELECT                    | Side<br>Select                        | Input terminal for Head Select signal. This signal selects the SIDE 0 or SIDE 1 of the common driver.                                                                                                                                                                                                                                                                                                                                                                               |

| WRITE<br>a, b                     | Write<br>Drive<br>a, b                | Output terminal of Write Driver.  The current multiplied by 4 with the determined current at the write current terminal is sinked.  WRITE a and WRITE b turn on alternately according to the Write Data "1" or "0".                                                                                                                                                                                                                                                                 |

| ERASE                             | Erase<br>Driver                       | Output terminal of Erase Driver.  The drive transistor turns on during the period of Erase Gate signal keeping low, and the Erase Gate timing is generated by write Gate signal in IC circuit.  This terminal has open collector NPN transistor, and erase current must be determined by an external resistor.                                                                                                                                                                      |

| WRITE<br>CURRENT                  | Write<br>Current                      | The terminal to determine the Write Current.  The Write current is determined with connecting an external resistor to +5V supply.  The Write Current on the WRITE a, b terminals is multiplied by 4 with the current on the WRITE CURRENT terminal, as follow equation. $I_{WT} = \frac{3.38}{Rex} \times 4 \text{ (mA)}$ where, $I_{WT}$ : WRITE CURRENT on the WRITE a, b Terminals.  Rex: External pull up resistor on the WRITE CURRENT terminal, and use the Value in kΩ unit. |

| WRITE<br>DATA                     | Write<br>Data Input                   | Write Data input terminal. The signal is devided through the counter in IC, and drives the Write Driver.                                                                                                                                                                                                                                                                                                                                                                            |

| WRITE<br>GATE                     | Write Gate                            | Input terminal for Write Gate signal.  The write gate is enable at input Low, and allows data writing.  Erase Gate signal is generated with the determined delay from the negative and positive edge of write Gate signal, and drives an erase driver.                                                                                                                                                                                                                              |

| WP                                | Write<br>Protect<br>Input             | Input terminal for the detected write protect signal from the Disk.  Common, Write, Erase drivers are all inhibited at input low, and WRITE PROTECT driver turns  ON.                                                                                                                                                                                                                                                                                                               |

| ERASE<br>ON<br>DELAY              | Erase ON<br>Timer                     | Terminal for connecting the external time contact Cex, Rex of internal Mono Multi circuit to determine the delay time between the both negative edge of write Gate and Erase Gate signal. It is necessary to determine the delay time for the fittest value according to the kind of FDD and HEAD component.                                                                                                                                                                        |

| ERASE OFF<br>DELAY                | Erase OFF<br>Timer                    | As same as above, but the delay time is determined between the both positive edge of Write Gate signal and Erase Gate signal.                                                                                                                                                                                                                                                                                                                                                       |

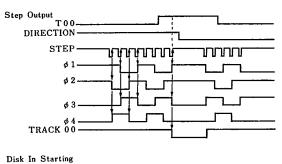

| STEP                              | step signal<br>Input                  | Terminal for step pulse input to drive the stepping motor to seek tracks. With each one step pulse input, the driver outputs $\phi_1$ , $\phi_2$ , $\phi_3$ , $\phi_4$ change sequentialy.                                                                                                                                                                                                                                                                                          |

| DIREC-<br>TION                    | Direction<br>Input                    | Input terminal for Direction signal to determine the direction of stepping motor revolution. Output drivers change with the direction of $\phi_1 \rightarrow \phi_2 \rightarrow \phi_3 \rightarrow \phi_4$ at the input low, and $\phi_1 \rightarrow \phi_4 \rightarrow \phi_3 \rightarrow \phi_2$ at the input High.                                                                                                                                                               |

| $\phi_1, \phi_2$ $\phi_3, \phi_4$ | 4 Phase<br>stepper<br>Drive<br>Output | Output terminals to drive the stepping motor coil. With each step pulse input, outputs change with the direction determined by Direction signal.  Output driver has emitter follower construction, but the driver cannot drive the stepping moto coil directly.  It is necessary to have external driver devices such as discrete transistors.                                                                                                                                      |

## HA16640NT

| Symbol                  | Name                       | - Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

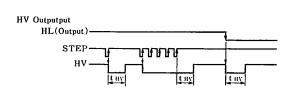

| ĦV                      | Voltage<br>Change<br>Timer | Timer output terminal to drive an external transistors switching supply voltage 12V to 5V each other for stepping motor coil.  With each step pulse input or each head load execution, the output turns ON during the determined period.  It is enable to switch supply voltage 12V to 5V alternately and to supply 12V for the stepping motor coil during the period of Low level on this terminal. |

| HV<br>TIME              | HV Timer                   | Terminal for connecting the external time constant of internal Mono Multi circuit to determine the period of keeping the HV output Low level.                                                                                                                                                                                                                                                        |

| WRITE<br>PROTECT        | Write Pro-<br>tect Output  | When the input level of $\overline{\text{WP}}$ turns Low and the drive select is executed, this output turns ON.                                                                                                                                                                                                                                                                                     |

| Т00                     | Track 00<br>Input          | Input terminal for 00 track detection.<br>High level input makes the 00 track detection.                                                                                                                                                                                                                                                                                                             |

| TRACK 00                | Track 00<br>Output         | Output terminal for 00 track detection. When the input level of T00 is High, and the both output $\phi_1$ , $\phi_2$ are High, this output turns ON.                                                                                                                                                                                                                                                 |

| ĪX                      | Index Input                |                                                                                                                                                                                                                                                                                                                                                                                                      |

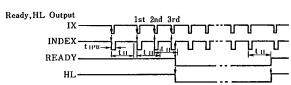

| INDEX                   | Index<br>Ouput             | Output for the Index pulse. With each input of the detected Index pulse at the $\overline{IX}$ terminal, the width formed pulse appears on this terminal as a Index pulse.                                                                                                                                                                                                                           |

| INDEX<br>PULSE<br>WIDTH | Index pulse<br>Width set   | Terminal for connecting the external time constant of the internal Mono Multi circuit to determine the output pulse width on INDEX.  It is enable to adjust the pulse width independently to the diameter of the DISK hole.                                                                                                                                                                          |

| READY                   | Ready<br>Output            | Output of the Ready signal.  When the disk revolution gets to the normal, after counting three index pulses, the output on this terminal turns ON, and shows FDD has gone into READY state.  If the revolution goes down under the normal value, the output turns OFF rapidly and shows NOT READY state.  And also the output shows High level continuously when Drive unit is not selected.         |

| INDEX<br>INTERVAL       | Index<br>Interval          | Terminal for connecting the external time constant of the internal Mono Multi circuit to determine the reference index period corresponding to the standard revolution number of the DISK.  In case of the FDD equipment having another revolution number, it is easier to adjust reference period by changing the time constant.                                                                    |

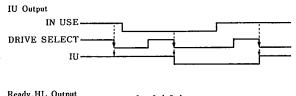

| DRIVE<br>SELECT         | Drive<br>Select<br>Input   | Input terminal for Drive select signal. Input low makes the selected operation, and Write function, output interface, IU output are all enable.                                                                                                                                                                                                                                                      |

| STAND<br>BY             | Stand by<br>Input          | Input terminal for Power Save Signal to reduce the power consumption in FDD equipment an LSI.  Input high inhibits all output terminals in write and Mechanism control circuit except commo driver, so power consumption in external circuit is reduced and this LSI makes itself into slee mode.  At the same time, common driver turns the READ mode.                                              |

| HEAD<br>LOAD            | Head Load                  | Input terminal for Head Load signal.  When READY is low and operation is under the not stand-by mode, head load is enable at the input low.                                                                                                                                                                                                                                                          |

| HL                      | Head Load<br>Output        | Terminal for Head Load output. Circuit has a emitter follower construction. But this terminal cannot drive the coil of head load magnet directly. It is necessary to have an external driving transistor.                                                                                                                                                                                            |

| IN USE                  | In Use<br>Output           | Input terminal for IN USE signal.  When the DISK is charged and the DRIVE equipment is selected, and also the operation is under the not stand-by mode, in use output is enable with the input low.                                                                                                                                                                                                  |

| IU .                    | In Use<br>Output           | In Use Output. Circuit has a open collector NPN transistor, and can drive LED directly.                                                                                                                                                                                                                                                                                                              |

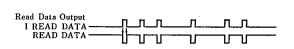

| I READ<br>DATA          | Read Data<br>Input         | Input terminal for Read Data from READ circuit such as HA16631P/MP. When both DRIVE SELECT and STAND BY are Low, inverted read data pulses appear on the READ DATA terminal.                                                                                                                                                                                                                         |

T-52-33-11

| Symbol             | Name                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ<br>DATA       | Read Data<br>Output | Output terminal for Read Data. Circuit has an open collector driver, and negative data pulses appear on this terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DISK IN            | Disk in<br>Input    | Input terminal for Disk charge detection signal.  Input High shows the charged state. When the charged Disk is detected, MON output turns ON and the motor starts, and also IU output turns ON too.  This function does not depend on the input level of MOTOR ON and IN USE. When the Disk revolution gets to normal state, after counting eight Index pulses, both MON and IU output turns OFF, so the motor stops and IN USE LED turns OFF.  After this operation, both MON and IU output depend on the input level of MOTOR ON and IN USE.  If the Disk is discharged, the motor stops and IU output is inhibited rapidly. |

| MOTOR ON           | Motor On            | Input terminal for the motor ON, OFF, control signal. Motor ON is enable at the input Low. Under the condition of the charged Disk and not-stand by, MON output turns OFF.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MON                | Motor On<br>Output  | Output terminal for the motor ON, OFF, control signal. Circuit has an open collector NPN driving transistor. Output Low makes the motor ON and High makes OFF. Also this terminal is able to connect to the motor control IC.                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{\mathrm{DD1}}$ | 5V Power<br>Supply  | 5V Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $V_{\mathbf{DD2}}$ | 12V Power<br>Supply | 12V Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GND                | Ground              | System ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### **■ EXAMPLE OF APPLICATION CIRCUIT** +5V +12V R 12 HEAD © 39 R<sub>6</sub> Why John Head Coil 38 Magnet Coil 36 <del>\_\_\_\_\_</del> 35 34 -@ 0 32 **@ @** 0 0 R1 MOTOR CONTROL IC Rex.1 28 27 26 25 Cex 1 HA16631 P 23 22 GND

T-52-33-1

#### **HA16640NT**

DISK IN

M ON

A World Leader in Technology

# Hitachi America, Ltd.

Semiconductor and IC Sales and Service Division 2210 O'Toole Avenue, San Jose, CA 95131 1-408-942-1500

7th 8th

**FEBRUARY 1985**

Printed in U.S.A.

8