## SONY

# **CXD1948R**

# IEEE1394 Link Layer LSI for DVB and DSS

#### Description

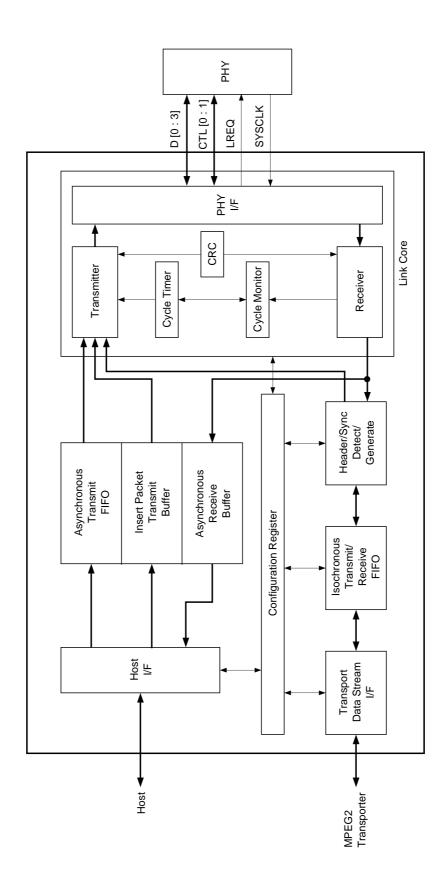

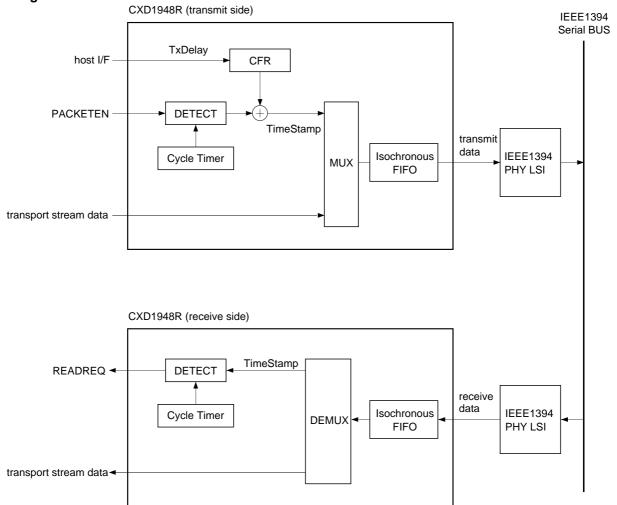

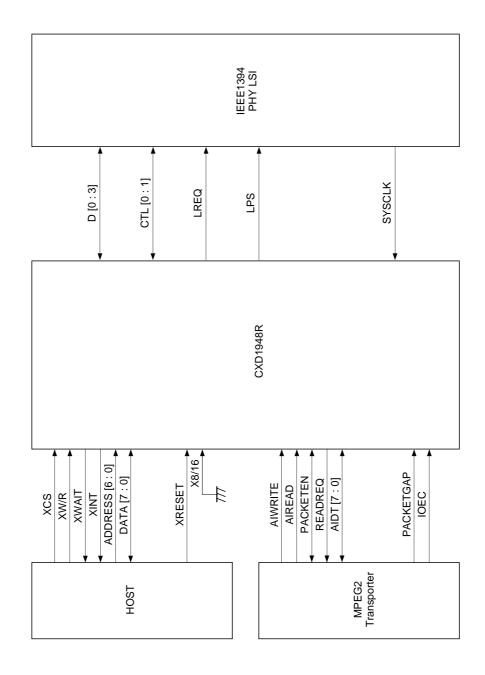

The CXD1948R is a Link Layer LSI conforming to the IEEE1394 serial bus standard. During transmission, the MPEG2 transport stream is time stamped, transformed to IEEE1394 format and sent to the IEEE1394 Phy IC.

During reception, the signal from IEEE1394 is kept in the built-in FIFO, synchronized to the time stamp value and output.

This IC utilizes Apple Computer's Fire Wire technology.

#### **Features**

- Conforms to IEEE1394 serial bus standard

- · Supports DVB and DSS transport streams

- Dedicated ports for asynchronous data/isochronous data

- Isochronous data inserted from asynchronous data port

- · Smoothing buffer function

- Large capacity FIFO

$\begin{tabular}{ll} Isochronous transmit/receive FIFO & 960 \times 32 \ bits \\ Asynchronous transmit FIFO & 30 \times 33 \ bits \\ Asynchronous receive FIFO & 36 \times 33 \ bits \\ Isochronous Insert Packet Transmit Buffer \\ \end{tabular}$

$47 \times 33$  bits

CIP header automatic attachment/detection

#### **Applications**

- Digital interface for D-STB

- Digital interface for D-VHS

#### Structure

Silicon gate CMOS IC

#### **Absolute Maximum Ratings** (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul> | Vdd     | Vss - 0.5 to +4.6        | V  |  |  |

|------------------------------------|---------|--------------------------|----|--|--|

| <ul> <li>Input voltage</li> </ul>  | Vı      | Vss - 0.5 to $Vdd + 0.5$ | V  |  |  |

| <ul> <li>Output voltage</li> </ul> | Vo      | Vss - 0.5 to $Vdd + 0.5$ | V  |  |  |

| Operating temperature              | erature |                          |    |  |  |

|                                    | Topr    | -20 to +75               | °C |  |  |

| Storage temperature                |         |                          |    |  |  |

|                                    | Tstg    | -55 to +150              | °C |  |  |

|                                    |         |                          |    |  |  |

#### **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | $V_{DD}$ | 3.0 to 3.6 | V  |

|------------------------------------|----------|------------|----|

| Operating temperature              | erature  |            |    |

|                                    | Topr     | -20 to +75 | °C |

Fire Wire is a registered trademark of Apple Computer Corporation, USA

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

## Contents

| 1. | Block Diagram                                                                | 3  |

|----|------------------------------------------------------------------------------|----|

| 2. | Pin Configuration                                                            | 4  |

| 3. | Pin Description                                                              | 5  |

| 4. | Electrical Characteristics                                                   | 8  |

|    | 4-1. DC Characteristics                                                      | 8  |

|    | 4-2. AC Characteristics                                                      | 8  |

|    | 4-3. Timing Definitions                                                      | 8  |

| 5. | Isochronous Communication                                                    | 9  |

|    | 5-1. Built-in FIFO                                                           | 9  |

|    | 5-2. Transport Stream I/F                                                    | 10 |

|    | 5-3. Transport Stream Packet Split and Combine Functions                     | 18 |

|    | 5-4. Transport Stream                                                        | 19 |

|    | 5-5. Isochronous Packet Structure                                            | 20 |

|    | 5-6. Relationship between Additional Data and CFR Registers                  | 27 |

|    | 5-7. 27MHz Time Stamp                                                        | 27 |

|    | 5-8. Dummy Packet Transmission                                               | 28 |

|    | 5-9. Time Stamp                                                              | 29 |

|    | 5-10. Error Processing                                                       | 30 |

|    | 5-11. Late Processing                                                        | 31 |

| 6. | Asynchronous Communication                                                   | 31 |

|    | 6-1. Host/IF                                                                 | 31 |

|    | 6-2. CFR                                                                     | 34 |

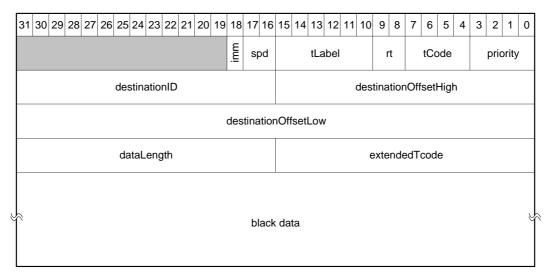

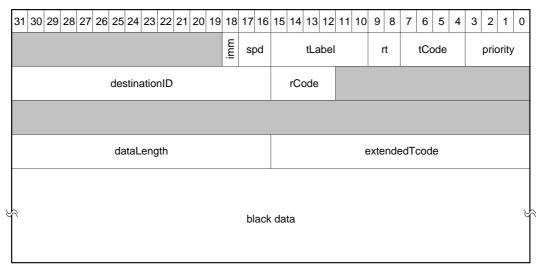

|    | 6-3. Asynchronous Packet Transmission                                        | 44 |

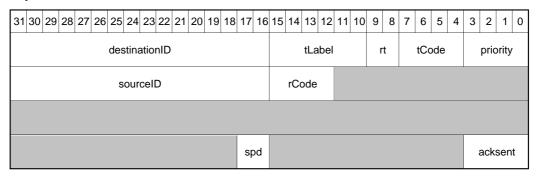

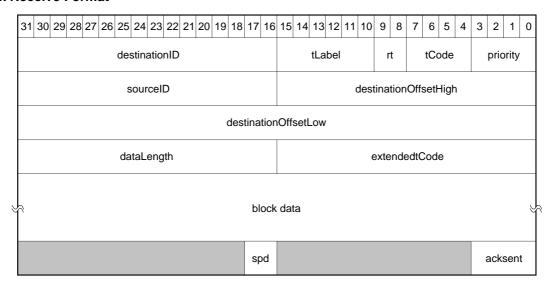

|    | 6-4. Asynchronous Packet Reception                                           | 47 |

|    | 6-5. CXD1948R Data Format                                                    | 52 |

|    | 6-6. Self-ID Packet Receiving Error Processing                               | 62 |

| 7. | Insert Packet                                                                | 63 |

|    | 7-1. Insert Packet Transmission                                              | 63 |

|    | 7-2. Adding a Time Stamp to the Insert Packet                                | 66 |

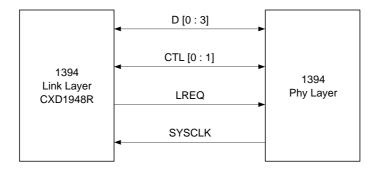

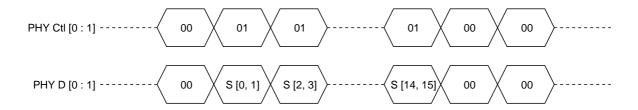

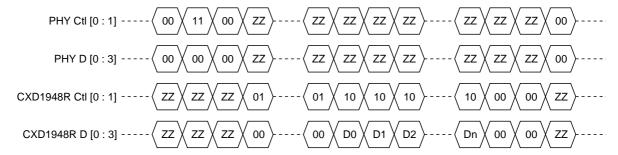

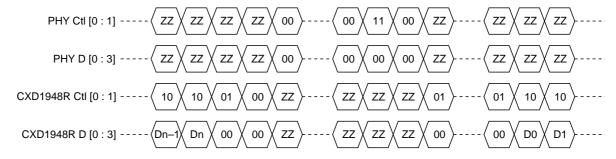

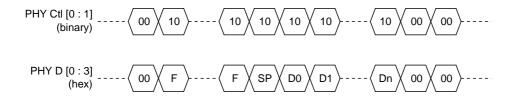

| 8. | Link-Phy Communication                                                       | 67 |

|    | 8-1. Link-Phy Interface Specifications                                       | 67 |

|    | 8-2. Communication                                                           | 67 |

| 9. | Parallel Input/Output Port                                                   | 74 |

| 10 | ). System Configuration Example                                              | 75 |

| Ar | nnex. Corresponding Table for CFR Access Address And Host Interface I/O Data | 76 |

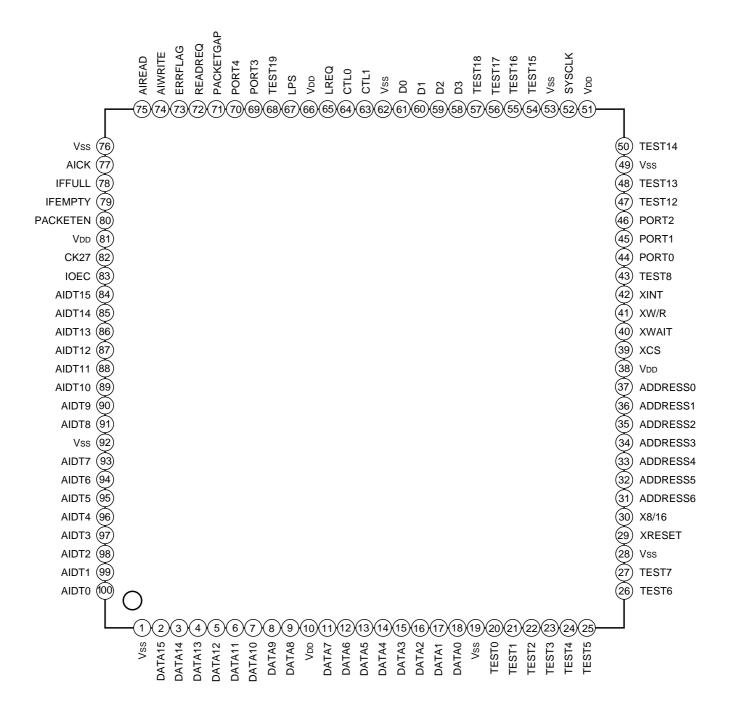

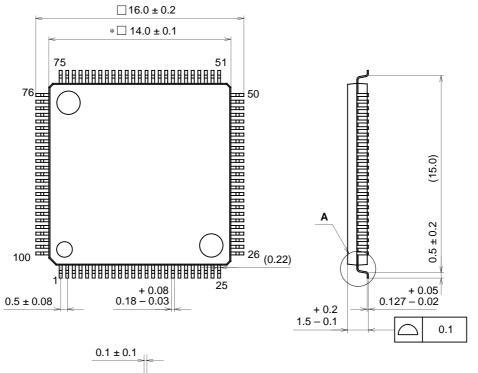

## 2. Pin Configuration

## 3. Pin Description

| Pin | Symbol   | I/O | Description                                                  |

|-----|----------|-----|--------------------------------------------------------------|

| No. |          |     | · · ·                                                        |

| 1   | Vss      | _   | GND                                                          |

| 2   | DATA15   | I/O | I/O data with host I/F BIT 15                                |

| 3   | DATA14   | I/O | I/O data with host I/F BIT 14                                |

| 4   | DATA13   | I/O | I/O data with host I/F BIT 13                                |

| 5   | DATA12   | I/O | I/O data with host I/F BIT 12                                |

| 6   | DATA11   | I/O | I/O data with host I/F BIT 11                                |

| 7   | DATA10   | I/O | I/O data with host I/F BIT 10                                |

| 8   | DATA9    | I/O | I/O data with host I/F BIT 9                                 |

| 9   | DATA8    | I/O | I/O data with host I/F BIT 8                                 |

| 10  | VDD      | _   | Power supply                                                 |

| 11  | DATA7    | I/O | I/O data with host I/F BIT 7                                 |

| 12  | DATA6    | I/O | I/O data with host I/F BIT 6                                 |

| 13  | DATA5    | I/O | I/O data with host I/F BIT 5                                 |

| 14  | DATA4    | I/O | I/O data with host I/F BIT 4                                 |

| 15  | DATA3    | I/O | I/O data with host I/F BIT 3                                 |

| 16  | DATA2    | I/O | I/O data with host I/F BIT 2                                 |

| 17  | DATA1    | I/O | I/O data with host I/F BIT 1                                 |

| 18  | DATA0    | I/O | I/O data with host I/F BIT 0                                 |

| 19  | Vss      | _   | GND                                                          |

| 20  | TEST0    | _   | Test pin*                                                    |

| 21  | TEST1    | _   | Test pin*                                                    |

| 22  | TEST2    | _   | Test pin*                                                    |

| 23  | TEST3    | _   | Test pin*                                                    |

| 24  | TEST4    | _   | Test pin*                                                    |

| 25  | TEST5    | _   | Test pin*                                                    |

| 26  | TEST6    | _   | Test pin*                                                    |

| 27  | TEST7    | _   | Test pin*                                                    |

| 28  | Vss      | _   | GND                                                          |

| 29  | XRESET   | I   | Master reset signal 0: Active; 1: Non-active                 |

| 30  | X8/16    | I   | I/O data with host I/F bus select signal 0: 8 bit; 1: 16 bit |

| 31  | ADDRESS6 | I   | Host I/F address bus BIT 6                                   |

| 32  | ADDRESS5 | I   | Host I/F address bus BIT 5                                   |

| 33  | ADDRESS4 | I   | Host I/F address bus BIT 4                                   |

| 34  | ADDRESS3 | I   | Host I/F address bus BIT 3                                   |

$<sup>\</sup>ensuremath{^{*}}$  The test pins should be used open.

| Pin<br>No. | Symbol   | I/O | Description                                          |

|------------|----------|-----|------------------------------------------------------|

| 35         | ADDRESS2 | ı   | Host I/F address bus BIT 2                           |

| 36         | ADDRESS1 | I   | Host I/F address bus BIT 1                           |

| 37         | ADDRESS0 | ı   | Host I/F address bus BIT 0                           |

| 38         | Vdd      | _   | Power supply                                         |

| 39         | XCS      | I   | Host I/F chip select signal 0: Active; 1: Non-active |

| 40         | XWAIT    | 0   | Host I/F wait signal 0: Active; 1: Non-active        |

| 41         | XW/R     | I   | Host I/F write/read signal 0: Write; 1: Read         |

| 42         | XINT     | 0   | Host I/F interrupt signal 0: Active; 1: Non-active   |

| 43         | TEST8    | _   | Test pin*                                            |

| 44         | PORT0    | I/O | Parallel I/O port BIT0                               |

| 45         | PORT1    | I/O | Parallel I/O port BIT1                               |

| 46         | PORT2    | I/O | Parallel I/O port BIT2                               |

| 47         | TEST12   | _   | Test pin*                                            |

| 48         | TEST13   | _   | Test pin*                                            |

| 49         | Vss      | _   | GND                                                  |

| 50         | TEST14   | _   | Test pin*                                            |

| 51         | Vdd      | _   | Power supply                                         |

| 52         | SYSCLK   | ı   | Phy I/F system clock (49.152MHz)                     |

| 53         | Vss      | _   | GND                                                  |

| 54         | TEST15   | _   | Test pin*                                            |

| 55         | TEST16   | _   | Test pin*                                            |

| 56         | TEST17   | _   | Test pin*                                            |

| 57         | TEST18   | _   | Test pin*                                            |

| 58         | D3       | I/O | Phy I/F data bus BIT 3                               |

| 59         | D2       | I/O | Phy I/F data bus BIT 2                               |

| 60         | D1       | I/O | Phy I/F data bus BIT 1                               |

| 61         | D0       | I/O | Phy I/F data bus BIT 0                               |

| 62         | Vss      | _   | GND                                                  |

| 63         | CTL1     | I/O | Phy I/F control bus BIT 1                            |

| 64         | CTL0     | I/O | Phy I/F control bus BIT 0                            |

| 65         | LREQ     | 0   | Phy I/F request signal                               |

| 66         | Vdd      |     | Power supply                                         |

| 67         | LPS      | 0   | Phy I/F Link power status signal                     |

| 68         | TEST19   | —   | Test pin*                                            |

$<sup>\</sup>ensuremath{^{*}}$  The test pins should be used open.

| Pin<br>No. | Symbol    | I/O | Description                                                                                 |

|------------|-----------|-----|---------------------------------------------------------------------------------------------|

| 69         | PORT3     | I/O | Parallel I/O port BIT3                                                                      |

| 70         | PORT4     | I/O | Parallel I/O port BIT4                                                                      |

| 71         | PACKETGAP | I   | Timing signal for adding time stamp to inserted isochronous packet 0: Non-active; 1: Active |

| 72         | READREQ   | 0   | Received packet synchronization reference signal 0: Non-active; 1: Active                   |

| 73         | ERRFLAG   | I/O | Packet error signal 0: Non-active; 1: Active                                                |

| 74         | AIWRITE   | I   | Transport stream I/F data write enable signal 0: Non-active; 1: Active                      |

| 75         | AIREAD    | I   | Transport stream I/F data read enable signal 0: Non-active; 1: Active                       |

| 76         | Vss       | _   | GND                                                                                         |

| 77         | AICK      | I   | Transport stream I/F clock                                                                  |

| 78         | IFFULL    | 0   | Isochronous FIFO status output 1: Full                                                      |

| 79         | IFEMPTY   | 0   | Isochronous FIFO status output 1: Empty                                                     |

| 80         | PACKETEN  | I/O | Transport stream I/F packet enable signal 0: Non-active; 1: Active                          |

| 81         | VDD       | _   | Power supply                                                                                |

| 82         | CK27      | I   | Clock input for 27MHz time stamp (open when not in use)                                     |

| 83         | IOEC      | ı   | Transport stream I/F data bus control signal 0: Input; 1: Output                            |

| 84         | AIDT15    | I/O | Transport stream I/F data bus BIT 15                                                        |

| 85         | AIDT14    | I/O | Transport stream I/F data bus BIT 14                                                        |

| 86         | AIDT13    | I/O | Transport stream I/F data bus BIT 13                                                        |

| 87         | AIDT12    | I/O | Transport stream I/F data bus BIT 12                                                        |

| 88         | AIDT11    | I/O | Transport stream I/F data bus BIT 11                                                        |

| 89         | AIDT10    | I/O | Transport stream I/F data bus BIT 10                                                        |

| 90         | AIDT9     | I/O | Transport stream I/F data bus BIT 9                                                         |

| 91         | AIDT8     | I/O | Transport stream I/F data bus BIT 8                                                         |

| 92         | Vss       | _   | GND                                                                                         |

| 93         | AIDT7     | I/O | Transport stream I/F data bus BIT 7                                                         |

| 94         | AIDT6     | I/O | Transport stream I/F data bus BIT 6                                                         |

| 95         | AIDT5     | I/O | Transport stream I/F data bus BIT 5                                                         |

| 96         | AIDT4     | I/O | Transport stream I/F data bus BIT 4                                                         |

| 97         | AIDT3     | I/O | Transport stream I/F data bus BIT 3                                                         |

| 98         | AIDT2     | I/O | Transport stream I/F data bus BIT 2                                                         |

| 99         | AIDT1     | I/O | Transport stream I/F data bus BIT 1                                                         |

| 100        | AIDT0     | I/O | Transport stream I/F data bus BIT 0                                                         |

$<sup>^{</sup>st}$  The test pins should be used open.

## 4. Electrical Characteristics

## 4-1. DC Characteristics

$(Ta = 25^{\circ}C, Vss = 0V)$

| Item                | Symbol          | Conditions                                                | Min.                  | Тур. | Max.   | Unit |

|---------------------|-----------------|-----------------------------------------------------------|-----------------------|------|--------|------|

| Input voltage       | ViH             | CMOS input cell                                           | 0.7Vdd                |      |        | V    |

| Input voltage       | VIL             | CMOS input cell                                           |                       |      | 0.2Vdd | V    |

| Output voltage      | Vон             | lон = −4.0mA                                              | V <sub>DD</sub> - 0.4 |      |        | V    |

| Output voltage      | Vol             | IoL = 4.0mA                                               |                       |      | 0.4    | V    |

| Input leak current  | l <sub>11</sub> | Bidirectional pin (input state)                           | -40                   |      | 40     | μA   |

| Input leak current  | l <sub>12</sub> | Normal input pin                                          | -10                   |      | 10     | μA   |

| Output leak current | loz             | Tri-state pin (for high impedance state) VIN = Vss or VDD | -40                   |      | 40     | μΑ   |

## 4-2. AC Characteristics (VDD = 3.0 to 3.6 V)

| Item         | Applicable pin                                      | Symbol           | Normal clock                                                | Conditions       | Min. | Тур. | Max. | Unit |

|--------------|-----------------------------------------------------|------------------|-------------------------------------------------------------|------------------|------|------|------|------|

| Input setup  | AIDT [15 : 0], ERRFLAG,<br>PACKETEN, IOEC, AIWRITE, | Tsu <sub>1</sub> | AICK                                                        |                  |      |      | 10   | ns   |

| Input hold   | AIREAD, PACKETGAP                                   | Th <sub>1</sub>  | AIREAD                                                      | AIREAD CL = 10pF |      |      | 0    | ns   |

| Output delay | AIDT [15 : 0], ERRFLAG,<br>READREQ                  | Td <sub>1</sub>  | Td <sub>1</sub> AlWRITE                                     |                  | 5    |      | 40   | ns   |

| Input setup  | D [3 : 0], CTL [1 : 0]                              | Tsu <sub>2</sub> |                                                             |                  | 5    |      |      | ns   |

| Input hold   | 0 [3 . 0], CTL [1 . 0]                              | Th <sub>2</sub>  | SYSCLK CL = 10pF                                            | CL = 10pF        | 2    |      |      | ns   |

| Output delay | D [3:0], CTL [1:0], LREQ                            | Td <sub>2</sub>  |                                                             |                  | 2    |      | 15   | ns   |

| Input setup  | ADDRESS [6 : 0],                                    | Тsuз             |                                                             |                  |      |      |      |      |

| Input hold   | DATA [15 : 0], XCS, XWR                             | Thз              | Refer to P.31 ATF/CFR/IPF write timing  ATF/CFR read timing |                  |      |      |      |      |

| Output delay | DATA [15:0], XWAIT, XINT                            | Tdз              | ATT/OF K Todd unling                                        |                  |      |      |      |      |

<sup>\*1</sup> During asynchronous I/F, the reference clock is AIWRITE (transmit)/AIREAD (receive).

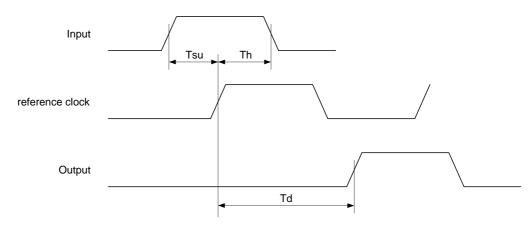

## 4-3. Timing Definitions

#### 5. Isochronous Communication

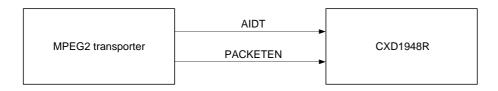

The CXD1948R has a function which transmits and receives DVB and DSS transport stream data as isochronous packets.

The communication of transport stream data with the DVB and DSS systems is performed using a dedicated I/O data bus and several control signal pins. (See below.)

Further, it supports a wide variety of application I/F, including 8-bit data and 16-bit data, synchronous and asynchronous.

| Name     | Width | in/out | Description                                                   |

|----------|-------|--------|---------------------------------------------------------------|

| AIDT     | 16    | in/out | Transport stream data bus                                     |

| PACKETEN | 1     | in/out | Indicates a valid packet (valid: 1; invalid: 0)               |

| ERRFLAG  | 1     | in/out | Indicates that the packet is an error (error: 1; no error: 0) |

| AIWRITE  | 1     | in     | Data write strobe signal                                      |

| AIREAD   | 1     | in     | Data read strobe signal                                       |

| READREQ  | 1     | out    | Packet read request signal                                    |

| AICK     | 1     | in     | Clock for interface (during sync)                             |

#### 5-1. Built-in FIFO

The CXD1948R has a built-in dedicated FIFO for isochronous communication.

The FIFO capacity is 3840 bytes, and it can accumulate 20 packets worth of DVB transport stream.

In order to actually use the built-in FIFO, the bank structure must be set. This is performed by the CFR PacketBanks register.

#### 5-2. Transport Stream Data I/F

#### 5-2-1. Data Bus

The data interface is 8 bit/16 bit, and switching is done by accessing the CFR AIDT16 register. (The default value is 8 bit.)

#### 5-2-2. Transport Packet Size

Data communication is done in transport stream packet units.

The data size for one packet can be set optionally by accessing the S PacketSize register on the CFR.

S\_PacketSize expresses the byte size of 1 source packet for isochronous communication.

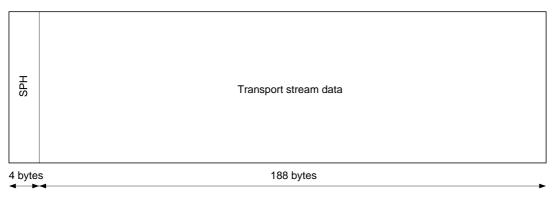

For DVB specifications, this is 192 (data 188 bytes, source packet header 4 bytes).

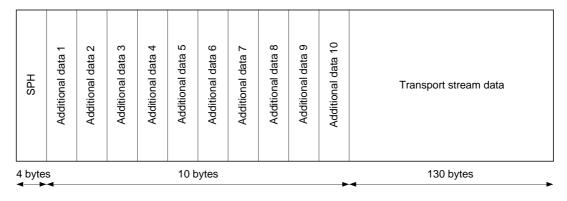

#### 5-2-3. Isochronous Additional Data

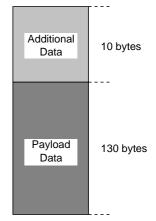

Optional data can be added to the transport stream packet when isochronous communication is performed. Setting of the additional data is done by setting the CFR AddSize and AddData1 to AddData10 registers. AddSize is a 4-bit register, and expresses the number of additional bytes for isochronous transmit/receive. AddData1 to AddData10 are each 8-bit registers, and express the additional data for isochronous transmit/receive.

The default setting is no additional data.

The additional data is inserted between the source packet header and the transport stream data.

The smallest group of data that can be handed under IEEE1394 is 32 bits, so the setting must be such that the total of the transport stream data and additional data is a 32-bit unit.

An example is shown below.

#### **Example of Isochronous Communication Setting**

When S\_PacketSize = 192 and AddSize = 0 (example of setting for DVB)

When S\_PacketSize = 144 and TxAddSize = 10 (example of setting for DSS)

#### 5-2-4. Transmit Interface

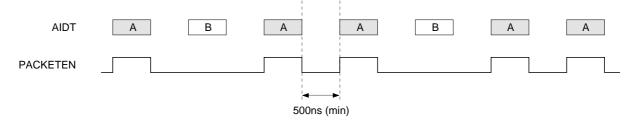

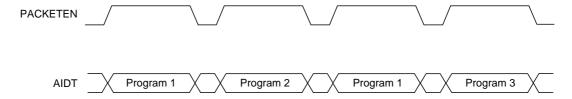

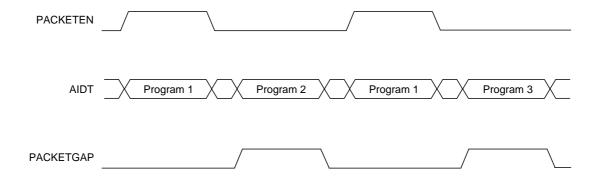

The CXD1948R is designed for use not only in transmitting an entire input transport stream, but also in transmitting one program only in the stream. The packet for transmission is selected through PACKETEN input as in the diagram below.

Moreover, constraints are imposed in the packet intervals of streams that can be input to the CXD1948R. Each time the CXD1948R receives one packet of transport stream data, it adds time stamp data and data from the host I/F, and there must be an interval of 500ns or more for this processing. The timing is illustrated below. Also, the PACKETEN input signal must input "HIGH" while the first data of the transport stream packet is being sent. The maximum period for PACKETENABLE signal high is the period that the transport stream packet data is valid.

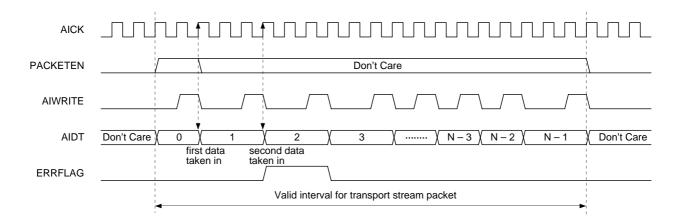

The timing charts for synchronous/asynchronous interface are shown below.

#### **Transmit Interface Limits**

Transmission of Program A

#### Transmit Interface (for sync mode/8 bit/Nbyte)

Sync interface mode is obtained by setting the CFR AsyncAl register to 0. (The default is 0.)

The CXD1948R identifies the first data of the transport stream packet by detecting that the PACKETEN signal has gone from low to high.

There is no particular need to input the PACKETEN signal after the first data. The size of the data taken in as valid data is equal to the value set in the CFR S\_PacketSize register, decreased by 4 and by the value set in the AddSize register. The timing for taking in of the data internally is done by AICK rise when AIWRITE is high.

The AIWRITE signal is used as the enable signal, so the interval that the AIWRITE signal is high relative to one data must be one AICK clock interval. The interval that the AIWRITE signal is low relative to one data is not specified.

The limits on AICK input frequency are given below.

For 8-bit data input: 40MHz (Max.), 2MHz (Min.) For 16-bit data input: 20MHz (Max.), 2MHz (Min.)

The ERRFLAG input during transmit can be made valid by setting the CFR ErrBitEnable register to 1. (The default is 0.)

The CXD1948R identifies the subject packet as an error if the ERRFLAG input is high for even one data during transport stream packet valid interval.

The switching timing for ERRFLAG input can be changed in the same way as data switching timing, with AIWRITE signal rise.

## Transmit Interface (for asynchronous mode/8 bit/Nbyte)

Asynchronous interface mode is obtained by setting the CFR AsyncAl register to 1. (The default is 0.)

The CXD1948R identifies the first data of the transport stream packet by detecting that the PACKET\_EN signal has gone from low to high.

There is no particular need to input the PACKET\_EN signal after the first data.

The size of the data taken in as valid data is equal to the value set in the CFR S\_PacketSize register, decreased by 4 and by the value set in the AddSize register. The timing for taking in of the data internally is done by AIWRITE rise.

The AIWRITE input is used as the clock, so there must be one AIWRITE input rising edge relative to one data. AIWRITE input duty is not specified, but the AIWRITE input must continue to be input evenly as the clock even outside of the transport stream packet valid interval.

The limits on AIWRITE input frequency are given below.

For 8-bit data input: 20MHz (Max.), 1MHz (Min.) For 16-bit data input: 10MHz (Max.), 1MHz (Min.)

The ERRFLAG input during transmit can be made valid by setting the CFR ErrBitEnable register to 1. (The default is 0.)

The CXD1948R identifies the subject packet as an error if the ERRFLAG input is high for even one data during transport stream packet valid interval.

The switching timing for ERRFLAG input can be changed in the same way as data switching timing, with AIWRITE signal rise.

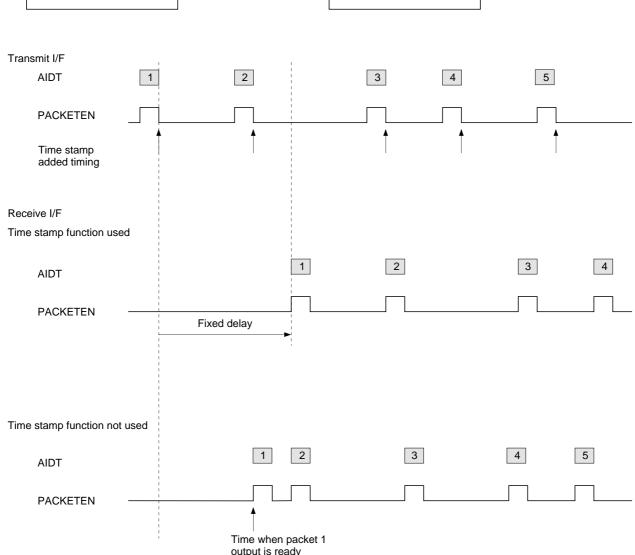

#### 5-2-5. Receive Interface

The CXD1948R supports two modes; one in which data is output based on the time stamp value added to the transport stream packet during transmission, and one in which the data is output consecutively as soon as it is ready, without using the time stamp.

When output is based on the time stamp value, the actual output timing is done using a value which is the time stamp value with a fixed delay added. This is done in order to keep the packet intervals even on the transmit and receive sides.

When the time stamp value is not used for output, data output begins when the packet has completely arrived at the receive side. In this case, the time required for the packet to be sent and arrive completely at the receive side varies for each isochronous cycle, and packet interval on the transmit side can not be guaranteed.

The timing is shown below.

The mode in which the time stamp is not used can be set by setting the CFR TmsDis register to 1. (The default is 0.)

#### **Receive Interface**

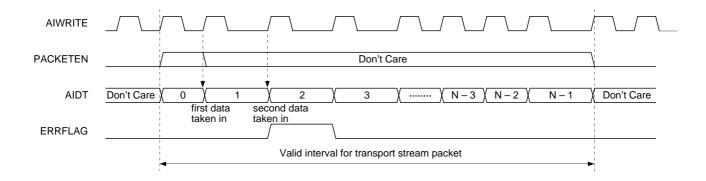

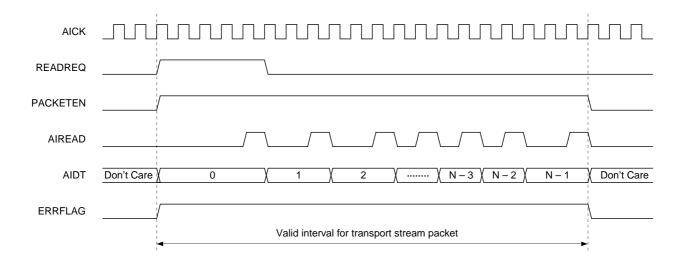

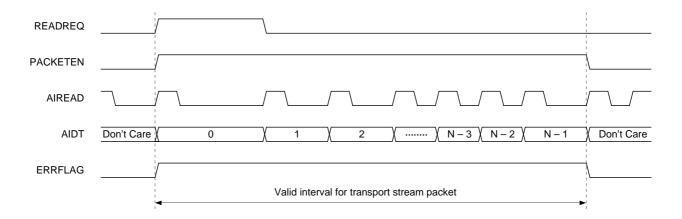

#### Receive Interface (for sync mode/8 bit/Nbyte)

Sync interface mode is obtained by setting the CFR AsyncAl register to 0. (The default is 0.)

The CXD1948R outputs the first data of the transport stream packet by changing the READREQ output signal and PACKETEN output signal from low to high when the packet has been completely received and is ready for output.

The READREQ output signal goes low when the first data is output.

The same as for transmit, the result of subtracting 4 and the value set in the AddSize register from the value set in the CFR S\_PacketSize register is used as the size of the valid data output in one packet. The timing is done by the AICK rise when AIREAD is high.

The AIREAD signal is used as the enable signal, so the interval that the AIREAD signal is high relative to one data must be one AICK clock interval. The interval that the AIREAD signal is low relative to one data is not specified.

The limits on AICK input frequency are given below.

For 8-bit data input: 40MHz (Max.), 2MHz (Min.) For 16-bit data input: 20MHz (Max.), 2MHz (Min.)

The ERRFLAG input during receive can be made valid by setting the CFR ErrBitEnable register to 1. (The default is 0.)

The CXD1948R outputs the ERRFLAG at high during the valid interval if the output transport stream packet is an error.

The switching timing for ERR\_FLAG input can be changed in the same way as data switching timing, with AIREAD signal rise.

#### Receive Interface (for asynchronous mode/8 bit/Nbyte)

Sync interface mode is obtained by setting the CFR AsyncAI register to 0. (The default is 0.)

The CXD1948R outputs the first data by changing the READREQ output signal and PACKETEN output signal from low to high when the packet has been completely received and is ready for output.

The READREQ output signal goes low when the first data is output.

The same as for transmit, the result of subtracting 4 and the value set in the AddSize register from the value set in the CFR S\_PacketSize register is used as the size of the valid data output in one packet. The timing is done by the AIREAD signal rise.

The AIREAD signal is used as the clock, so there must be one AIREAD input rising edge relative to one data. AIREAD input duty is not specified, but the AIREAD input must continue to be input evenly as the clock even outside of the transport stream packet valid interval.

The interval that the AIREAD signal is low relative to one data is not specified.

The limits on AICK input frequency are given below.

For 8-bit data input: 20MHz (Max.), 1MHz (Min.) For 16-bit data input: 10MHz (Max.), 1MHz (Min.)

The ERRFLAG input during receive can be made valid by setting the CFR ErrBitEnable register to 1. (The default is 0.)

The CXD1948R outputs the ERRFLAG at high during the valid interval if the output transport stream packet is an error.

The switching timing for ERR\_FLAG input can be changed in the same way as data switching timing, with AIREAD signal rise.

#### 5-2-6. Using the ERRFLAG Pin

The CXD1948R can function as a transport stream data interface using error information.

Concretely, this is done using the ERRFLAG pin.

Like other transport stream data interfaces, the ERRFLAG pin is a bidirectional pin. I/O switching is performed by the CFR IGFMode register.

Also, ERRFLAG control is performed by the CFR ErrBitEn and ErrOutEn registers.

The settings when using ERRFLAG during transmit and receive are given below.

#### **Transmit settings**

The ERRFLAG input can be made valid by setting the CFR ErrBitEn register to "1". (The default is "0".)

In order to add the error information provided by ERRFLAG to an isochronous packet and transmit this information, the added data must be 4 bytes or more.

Concretely, the CFR AddSize register value must be 4 or larger.

Both of the conditions below must be met to send error information using the ERRFLAG pin during transmit.

- (1) The ErrBitEn register is 1.

- (2) The AddSize register is 4 or higher.

#### Receive settings

The ERRFLAG output can be made valid by setting the CFR ErrOutEn register to "1". (The default is "0".) The CXD1948R handles received packet errors in two ways as follows.

(1) Packets with error information added to the transport stream data

In this case, the error information must be added to the received isochronous packet.

In addition, the CFR ErrBitEn register must be set to 1.

(2) Error packets occurring during isochronous communication

These errors refer to packets received with non-consecutive DBC values due to CRC errors or Late processing during transmit.

In this case, only the CFR ErrOutEn register is set.

Setting this register to "1" inserts an error packet between packets with non-consecutive DBC values.

As a result, one packet of ERRFLAG = 1 data is read by the transport stream data interface.

If the ErrOutEn register is set to 0, this processing is not performed.

Non-consecutive DBC values also result when the receive FIFO overflows, and the processing is the same in these cases as well.

#### 5-3. Transport Stream Packet Split and Combine Functions

The CXD1948R supports split and combine functions in order to use the bus bandwidth effectively.

Concretely, the input transport stream packet can be split or combined according to the input rate and transmitted as an isochronous packet.

The minimum size which can be split on the CXD1948R is one data block.

For DVB specifications, one data block consists of 24 bytes, which means that 1 packet can be divided into eighths for transmission.

The maximum size which can be combined is 15 packets. However, if the number of packets which can be transmitted in that cycle is smaller than the number that can be combined, all the packets present are combined in the transmission FIFO buffer and transmitted.

The number of data blocks to be transmitted in one isochronous cycle is set before hand according to the stream peak rate.

This is done by setting values in the CFR NOSP and NODB registers.

The number of transmit source packets in one isochronous cycle is expressed by NOSP, and the number of transmit data blocks in one isochronous cycle is expressed by NODB.

The default values are NOSP = 0001 and NODB = 000, for transmission of one source packet in one isochronous cycle. Always be sure to set either NOSP or NODB to 0.

If the isochronous transmission parameters are not set such that the transmission rate is greater than the input stream peak rate, the FIFO buffer may fail.

#### **Example of Isochronous Transmit using Packet Split and Combine Functions** Ε h CXD1948R MPEG2 transporter L 0 'n S []3[] 1 2 IEEE1394 Isochronous t 1 2 (//3// S р t p 1 2 2 3 t Н g 2 //8// 3 4 2 6 9 s 1 m<sup>2</sup> []3]] 5 //4// 2 С 4/ 5 a<sub>6</sub> [7] // 8//

-18 -

## 5-4. Transport Stream Data Bandwidth

The bandwidths on which transport stream data can be transmitted on the CXD1948R are illustrated below.

## DVB

| NOSP<br>value | NODB<br>value | No. of transmit data | Transmittable data rate |

|---------------|---------------|----------------------|-------------------------|

| 0000          | 001           | 1 data block         | 1.5Mbps                 |

| 0000          | 010           | 2 data blocks        | 3.0Mbps                 |

| 0000          | 100           | 4 data blocks        | 6.0Mbps                 |

| 0001          | 000           | 1 source packet      | 12.0Mbps                |

| 0010          | 000           | 2 source packets     | 24.0Mbps                |

| 0011          | 000           | 3 source packets     | 36.0Mbps                |

| 0100          | 000           | 4 source packets     | 48.1Mbps                |

| 0101          | 000           | 5 source packets     | 60.1Mbps                |

## DSS

| NOSP  | NODB  | No. of transmit data | Transmittable | Transmittable data rate |              |  |

|-------|-------|----------------------|---------------|-------------------------|--------------|--|

| value | value | No. or transmit data | data rate     | Addsize = Ah            | Addsize = 0h |  |

| 0000  | 001   | 1 data block         | 2.2Mbps       | 2.0Mbps                 | 2.2Mbps      |  |

| 0000  | 010   | 2 data blocks        | 4.4Mbps       | 4.1Mbps                 | 4.4Mbps      |  |

| 0001  | 000   | 1 source packet      | 8.9Mbps       | 8.3Mbps                 | 8.9Mbps      |  |

| 0010  | 000   | 2 source packets     | 12.0Mbps      | 16.6Mbps                | 17.9Mbps     |  |

| 0011  | 000   | 3 source packets     | 26.8Mbps      | 24.9Mbps                | 26.8Mbps     |  |

| 0100  | 000   | 4 source packets     | 35.8Mbps      | 33.2Mbps                | 35.8Mbps     |  |

| 0101  | 000   | 5 source packets     | 44.8Mbps      | 41.6Mbps                | 44.8Mbps     |  |

| 0110  | 000   | 6 source packets     | 53.7Mbps      | 49.9Mbps                | 53.7Mbps     |  |

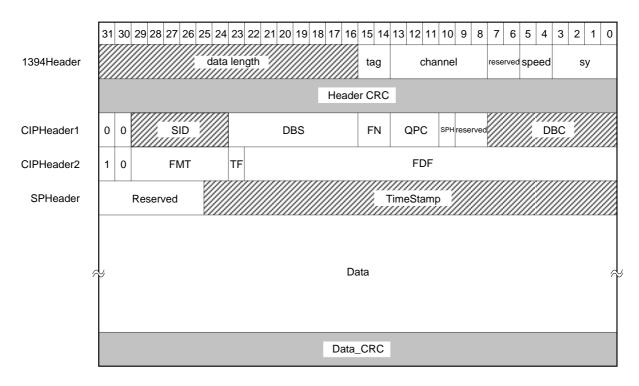

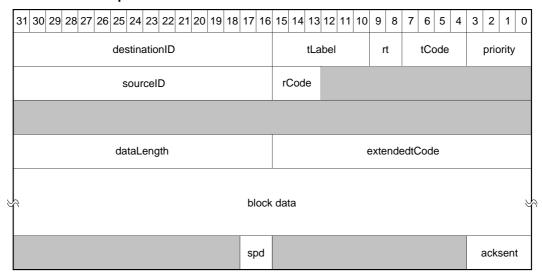

#### 5-5. Isochronous Packet Structure

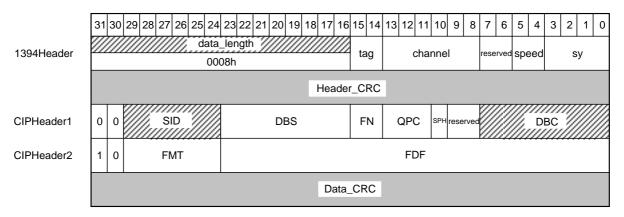

The basic isochronous packet structure supported by the CXD1948R is illustrated below.

On the CXD1948R, CIPHeaders 1 and 2 are automatically attached/detected in conformity to AV protocol.

Also, a source packet header is automatically added/detected on the transport stream packet based on the MPEG Data Transmission for IEEE1394 Digital Interface specifications proposed in DVB-SMI.

When one source packet is transmitted in one isochronous cycle, 1st quadlet is 1394Header, 2nd quadlet is Header\_CRC (added at Link Core), 3rd quadlet is CIPHeader1, 4th quadlet is CIPHeader2, 5th quadlet is source packet header and 6th quadlet and after is the data area. The final quadlet is Data\_CRC (added at Link Core). When a dummy packet is transmitted, there are only 1394Header, Header\_CRC, CIPHeader1, CIPHeader2 and Data\_CRC.

#### **Basic Structure**

#### 1394Header Fields

| Field Name  | Description                                                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| data_length | Indicates the byte length of data from CIPHeader1.                                                                                   |

| tag         | Type of format for data transferred as isochronous packet. 00: no Header 01: format defined by AV protocol 10: Reserved 11: Reserved |

| channel     | Channel number used by the transmitted packet.                                                                                       |

| speed       | Defines transfer speed. 00: 100Mbit/s 01: 200Mbit/s 10: 400Mbit/s 11: Undefined The CXD1948R supports "00" and "01".                 |

| sy          | This field is defined by the application.                                                                                            |

**Note:** The Link Core must be informed of the communication speed in the case of isochronous communication, so [5 : 4] of [7 : 4], where a tCode is inserted, is used as the speed code. This is replaced with tCode (1010) at the Link Core.

#### **CIPHeader1 Fields**

| Field Name | Description                                                                                                                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SID        | The CXD1948R Node ID. (0 to 3Fh)                                                                                                                                                                    |

| DBS        | The number of quadlets transferred in one isochronous packet. For DVB specifications, this is "00000110b" and for DSS specifications, "00001001b".                                                  |

| FN         | Indicates how many data blocks a source packet is divided into.                                                                                                                                     |

| QPC        | The number of quadlets added to an incomplete packet when the source packet is split. Fixed at "0h" on the CXD1948R.                                                                                |

| SPH        | Expresses whether a source packet header is used or not. Fixed at "1" on the CXD1948R.                                                                                                              |

| DBC        | Increased by one for each data block. This is a free run continuity counter. When multiple data blocks are to be sent as a single isochronous packet, indicates the value for the first data block. |

## **CIPHeader2 Fields**

| Field Name | Description                                                                                        |

|------------|----------------------------------------------------------------------------------------------------|

| FMT        | Data format ID. This is "100000b" for DVB and "100001b" for DSS specifications.                    |

| TF         | Indicates whether data is time-shifted. 1 if time-shifted; 0 if not time-shifted.                  |

| FDF        | Used in application defined by FMT. The value set via the host I/F is input as is on the CXD1948R. |

#### SPHeader fields

| Field Name | Description                                                                                                        |

|------------|--------------------------------------------------------------------------------------------------------------------|

| Reserved   | The value set via the host I/F is input as is on the CXD1948R.                                                     |

| TimeStamp  | This is the value of the time that the transport stream packet arrived at the CXD1948R plus the fixed delay value. |

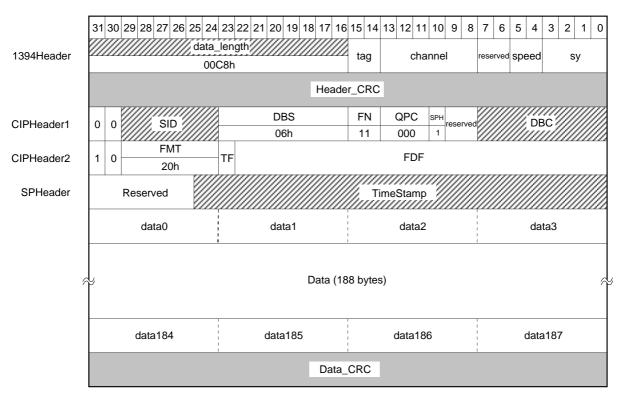

#### 5-5-1. DVB Format

The DVB format supported by the CXD1948R is described below.

The CFR S\_PacketSize and AddSize registers are set as shown below when using the CXD1948R in DVB format.

S\_PacketSize: 0C0h

AddSize: 0h

Next, the NOSP and NODB registers are set. These determine how many data are to be transmitted/received in one isochronous cycle.

The structures of isochronous packets for transmit/receive of data consisting of 1 source packet, 4 data blocks or 2 source packets in one isochronous cycle are illustrated below.

## **DVB/Isochronous Packet Structure (1 source packet)**

#### **DVB/Isochronous Packet Structure (4 data blocks)**

(Second half data) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 7 5 4 2 1 0 6 3 data\_length 1394Header channel reserved speed sy 0068h Header\_CRC DBS QPC FΝ SPH CIPHeader1 0 SID DBC 06h 11 000 1 FMT CIPHeader2 0 TF **FDF** 20h data92 data93 data94 data95 data96 data97 data98 data99 Data (96 bytes) data184 data185 data186 data187 Data\_CRC

#### **DVB/Isochronous Packet Structure (2 source packets)**

SONY CXD1948R

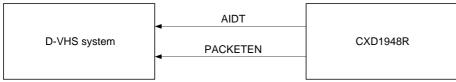

#### 5-5-2. DSS Format

The DSS format supported by the CXD1948R is described below.

The interface with the system and the CFR setting differ according to whether the CXD1948R is used as DSS-STB or DSS-DVHS system digital I/F, as follows:

- A) DSS-STB system digital I/F: S\_PacketSize: 090h; AddSize: 0h

- B) DSS-DVHS system digital I/F: S\_PacketSize: 090h; AddSize: Ah

The isochronous data format on the IEEE1394 bus does not change for A and B. Only the amount of data interfaced with the system changes.

The DSS-STB system interfaces with 130 bytes as one packet of transport stream.

The CXD1948R adds a 4-byte source packet header and 10 bytes of data set on the CFR via the host I/F to the received 130 bytes, then transmits them as an isochronous packet.

For the DSS-DVHS system, only the source packet header is removed from the received isochronous packet, and 140 bytes of data are output as transport stream data.

The above is for the case of transmission; in reception, 140 bytes of data is input from the DSS-DVHS system, and 130 bytes of data is output to the DSS-STB system.

The same as for the DVB format, the amount of data transmitted in one isochronous cycle is set by the NOSP and NODB registers.

Interface with DSS-STB system

Pavload

Data

130 bytes

Isochronous packet

on IEEE1394 bus

1394header 4 bytes headerCRC 4 bytes CIPheader1 4 bytes CIPheader2 4 bytes SPheader 4 bytes Additional 10 bytes Data Pavload 130 bytes Data 4 bytes Data\_CRC

Interface with DSS-DVHS system

## **DSS/Isochronous Packet Structure (1 source packet)**

| 1394Header | data                            | 23 22 21 20 19 18 17 16<br>Length | 15 14 13 12 11 10 9 8 tag channel | 3 7 6 5 4 3 2 1 0 reserved speed sy |  |  |

|------------|---------------------------------|-----------------------------------|-----------------------------------|-------------------------------------|--|--|

|            |                                 | Header                            | _CRC                              |                                     |  |  |

| CIPHeader1 | 0 0 SID                         | DBS<br>09h                        | FN QPC SPH reserve                | DBC                                 |  |  |

| CIPHeader2 | 1 0 FMT 21h                     | TF                                | FDF                               |                                     |  |  |

| SPHeader   | Reserved                        |                                   | TimeStamp                         |                                     |  |  |

|            | TIF Reserved Tii                | meStamp (27MHz)                   | EFTFUF CR                         | MS Reserved                         |  |  |

|            | Reserved                        | Channel I                         | Information Reserved              |                                     |  |  |

|            | Re                              | served                            | data0                             | data1                               |  |  |

|            | data2                           | data3                             | data4                             | data5                               |  |  |

| 4          | ≈ Data (130 bytes)              |                                   |                                   |                                     |  |  |

|            | data126 data127 data128 data129 |                                   |                                   |                                     |  |  |

|            | Data_CRC                        |                                   |                                   |                                     |  |  |

Note: The diagonally shaded areas ([]]) for 1394Header and CIPHeader1 and 2 are attached automatically by the CXD1948R. Other areas are set from the external microcomputer via the host I/F. The white areas ([]]) indicate additional data.

In transmission from the CXD1948R to an IEEE 1394PHYIC, the four bits marked "reserved" and "speed" of the 1394Header are automatically replaced by "tcode".

#### **Additional Data Fields**

| Field Name             |                          | Description                                        |

|------------------------|--------------------------|----------------------------------------------------|

| TIF                    | Time Stamp Invalid Flag  | 1: Invalid, 0: valid                               |

| TimeStamp              | Time stamp value stamped | d at 27MHz synchronized to MPEG2 transport stream. |

| EF                     | Error Flag               | 1: Error, 0: No Error                              |

| TF                     | Transition Flag          | 1: Transition (1sec), 0: No Transition             |

| UF                     | VBV Underflow Flag       | 1: Underflow, 0: Normal                            |

| CR                     | Copy Right               |                                                    |

| MS                     | Multi/Single             | 00: Single program, 01: 10: 11: Reserved           |

| Channel<br>Information |                          |                                                    |

| Reserved for bit rate  |                          |                                                    |

#### 5-6. Relationship between Additional Data and CFR Registers

The CXD1948R has 10 bytes of data registers for additional data. These are common registers for transmit and receive. Setting is done from the host I/F to add data to the transport stream data.

For receive, the additional data is detected from the isochronous packet and the value is written in.

The relationship between the CFR additional data registers AddData and the additional data in DSS format is described below.

| CFR Registers |   |     | DS  | SS A | Addit | ional Data |     |

|---------------|---|-----|-----|------|-------|------------|-----|

| MSB LSE       | } | MSI | 3   |      |       |            | LSB |

| AddData1      |   | TIF | Re  | eser | ved   |            |     |

| AddData2      |   |     | Tiı | meS  | tam   | p (27MHz)  |     |

| AddData3      |   | EF  | TF  | UF   |       | CR         |     |

| AddData4      |   | М   | IS  |      | Ras   | erved      |     |

| AddData5      |   |     |     | •    | 1103  | erveu      |     |

| AddData6      |   |     | C   | hanı | nel I | nfomation  |     |

| AddData7      |   |     |     |      |       | momation   |     |

| AddData8      |   |     |     |      |       |            |     |

| AddData9      |   |     |     | F    | Rese  | erved      |     |

| AddData10     |   |     |     |      |       |            |     |

#### 5-7. 27MHz Time Stamp

When a 27MHz time stamp synchronized to the transport stream is added on the CXD1948R, the CFR 27MTS register is set to "1". Further, a 27MHz clock must be input from the CK27 pin. When the 27MTS register is set to "0", the 27MHz time stamp field value enters as is to the lowest 4 bits of the AddData1 register and the value of the AddData2 register.

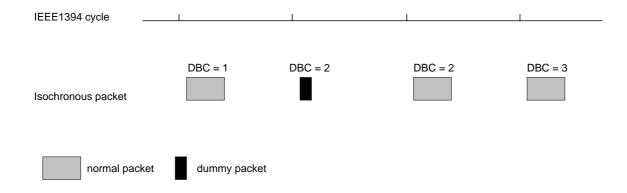

#### 5-8. Dummy Packet Transmission

The CXD1948R has a function that automatically transmits a dummy packet when isochronous transmission is muted, or when there is no packet to be transmitted during isochronous transmission.

The dummy packet consists of header information only. The DBC value is the normal packet value transmitted on the next isochronous cycle.

#### **Dummy Packet Structure**

Note: The diagonally shaded areas ([[[]]]) for 1394Header and CIPHeader1 and 2 are attached automatically by the CXD1948R. Other areas are set from the external microcomputer via the host I/F.

In transmission from the CXD1948R to an IEEE 1394PHYIC, the four bits marked "reserved" and "speed" of the 1394Header are automatically replaced by "tcode".

## Example of Dummy Packet Transmission (for transmit of 1 data block)

#### 5-9. Time Stamp

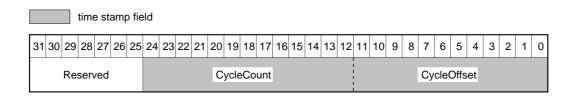

The CXD1948R has a function that adds a time stamp to the input transport stream packet and transmits it, detects the time stamp on a received packet, and outputs the transport stream packet based on that value. The time stamp is 25 bits, and is superimposed on the source packet header.

#### **Source Packet Header Structure**

#### **Time Stamp Field**

| Field Name  | Description                                                                                    |

|-------------|------------------------------------------------------------------------------------------------|

| CycleCount  | Time intervals of less than 1 second are expressed in units of 125µs. (0 to 1F3Fh)             |

| CycleOffset | Time intervals of less than 125µs are expressed in units of 24.576MHz clock cycles. (0 to BFF) |

## **Time Stamp Adding**

The CXD1948R takes in the internal cycle timer value when the transport stream packet is completely received. Next it adds the CFR TxDelay register value set from the host I/F to the cycle timer value, and superimposes it on the source packet header as a time stamp.

#### **Time Stamp Detection**

After completely receiving the isochronous packet, the CXD1948R detects the superimposed time stamp to the source packet header. It compares the detected time stamp value and the internal cycle timer value, and starts data output from the point where the times match. (Actually output request is performed.)

Also, if the time is already past, it performs data output immediately.

#### **Block Diagram**

#### 5-10. Error Processing

When a correct packet can not be received, for example if a CRC error is generated or a packet which violates protocol is received, the CXD1948R automatically performs error processing.

Error processing control is done by setting the CFR ErrOutEn register.

A description of error processing follows.

### **Processing for Transmit**

ErrFlag input becomes valid when the CFR ErrBit Enable register is set to "1".

The input error packet is processed in the same way as a normal packet.

However, error information is also transmitted, so only the mode when additional data is added to the transport stream data is valid. (The superimposed position of the error information is the MSB of the additional data 3rd byte.)

ErrFlag input becomes invalid when the ErrBitEnable register is set to "0".

#### **Processing for Receive**

ErrFlag output becomes valid when the CFR ErrBit Enable register is set to "1".

When the received isochronous packet is judged as an error, ErrFlag is made "1" and output.

Because the time stamp cannot be trusted, output is performed immediately.

When the ErrFlagEnable register is set to "0", only the correctly received isochronous packets are output.

#### 5-11. Late Processing

The CXD1948R automatically performs late processing when an isochronous packet is transmitted.

In late processing, the time stamp superimposed on the source packet header of the packet for transmission is consulted, and if there is the possibility that the receiving side may not receive the entire packet within the timing indicated by the time stamp, the packet transmission is canceled.

The time stamp value is the time when the transport stream packet was received plus TxDelay, so the number of packets for late processing can be reduced by making the TxDelay value larger.

However, the upper limit of the TxDelay value depends on the stream transmission rate and the built-in FIFO buffer capacity.

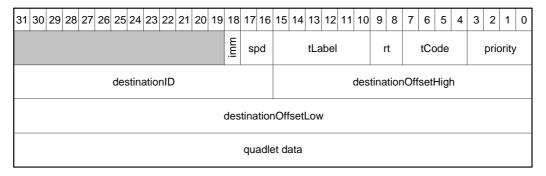

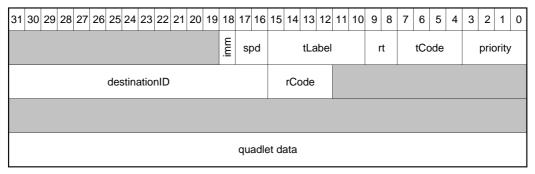

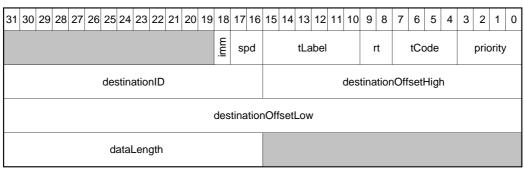

#### 6. Asynchronous Communication

#### 6-1. Host/IF

The host I/F controls data communication between the external CPU and the CXD1948R ATF/ARF/CFR/IPB\*1, respectively.

Communications between the CPU and CXD1948R include:

- 1) CPU writes data to ATF → asynchronous packet transmit

- 2) CPU reads data in ARF → asynchronous packet receive

- 3) CPU writes data to CFR → mode, header data setting

- 4) CPU reads data in CFR → internal status, header data read-in

- 5) CXD1948R informs CPU of an interrupt event with an interrupt signal

- 6) CPU performs insert of isochronous packet from host I/F

- 7) CPU sets additional information (10 bytes) in isochronous packet

The CXD1948R supports 16-bit and 8-bit host I/F.

The ATF/ARF/CFR built in to the CXD1948R have a 32-bit structure, so all bits can not be accessed with one access. The target address must be accessed two consecutive times for 16 bits and four consecutive times for 8 bits.

The roles played by the signals communicated between the CXD1948R and the external microcomputer are given bellow.

| DATA [15:0]   | in/out | Data for writing to or reading from specified address                        |

|---------------|--------|------------------------------------------------------------------------------|

| ADDRESS [7:0] | in     | Address for writing or reading data                                          |

|               |        | Data destination (CFR or FIFO) and data breakpoint (Write or Confirm) are    |

|               |        | discriminated according to the address                                       |

| XCS           | in     | Access enable from host bus (low active)                                     |

| XW/R          | in     | Data read/write enable signal (high: read; low: write)                       |

| XWAIT         | out    | Indicates access (read or write) completed to specified address (low active) |

| XINT          | out    | Interrupt signal. Indicates some kind of interrupt when low                  |

|               |        | Type of interrupt and mask specified by CFR                                  |

| X8/16         | in     | Host I/F data bus switching                                                  |

|               |        | H: 16 bits; L: 8 bits                                                        |

<sup>\*1</sup> ATF (Asynchronous Transmit Fifo), ARF (Asynchronous Receive Fifo), CFR (Configuration Register), IPB (Insert Packet transmit Buffer)

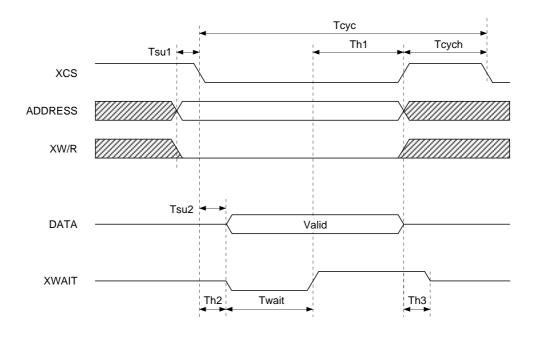

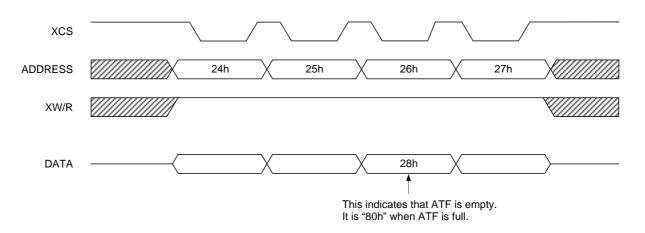

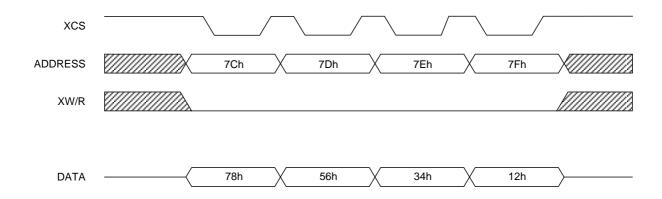

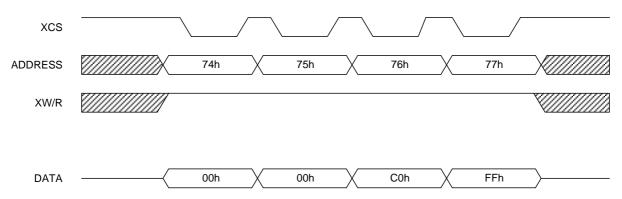

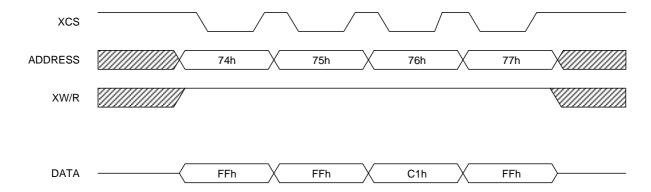

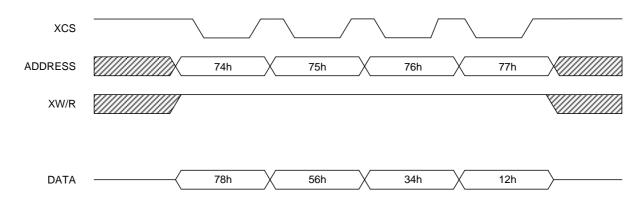

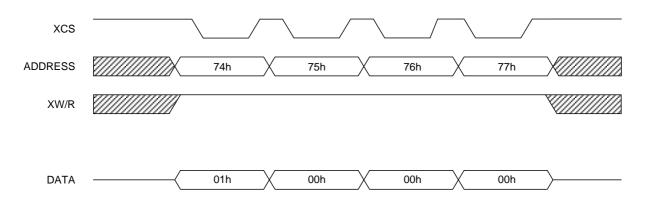

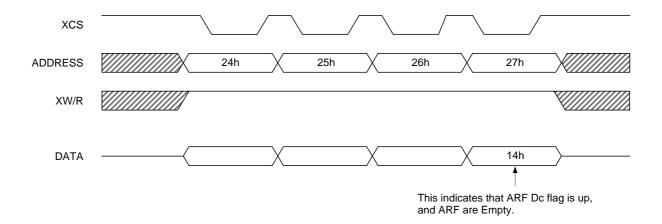

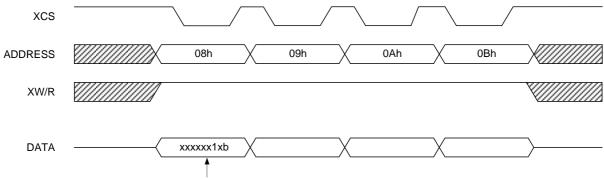

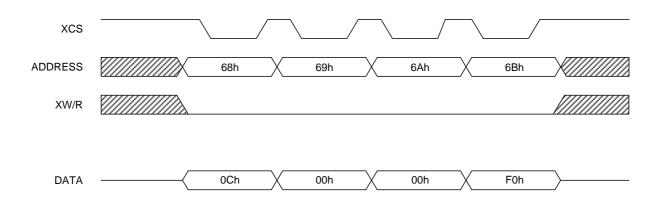

## Writing Timing to ATF/CFR/IPF

For write, the CXD1948R latches ADDRESS, XW/R and DATA at XCS falling edge. The timing chart is illustrated below.

$Tsu1 \geq 0ns, \, Tsu2 \leq 5ns, \, Th1 \geq 0ns$   $Tcyc \geq 250ns, \, Tcych \geq 100ns, \, Twait \leq 100ns, \, Th2 \leq 5ns, \, Th3 \leq 5ns$

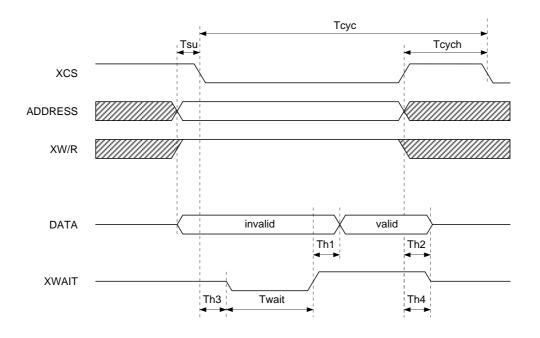

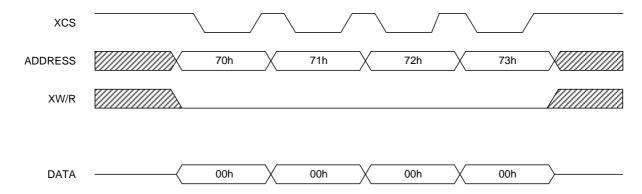

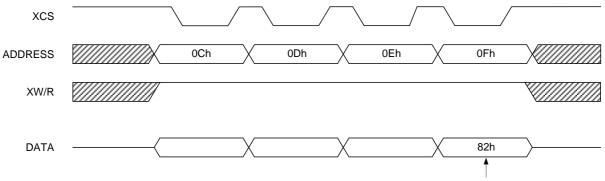

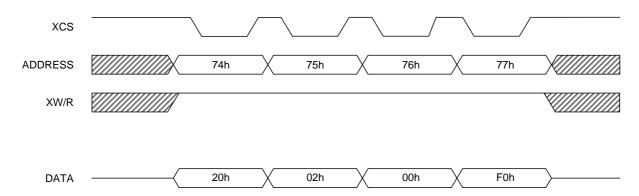

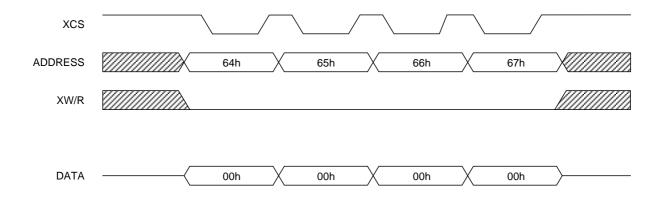

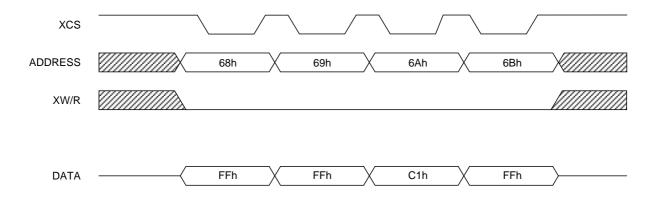

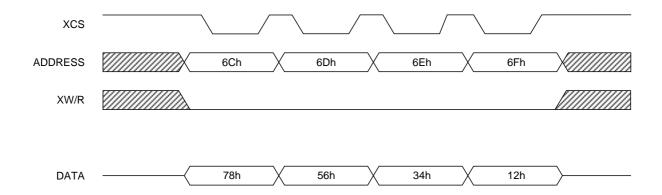

## Timing for Data Read from ARF/CFR

For read, the CXD1948R latches ADDRESS and XW/R at XCS falling edge. The timing chart is illustrated below.

Tsu  $\geq$  0ns, Th1  $\geq$  5ns Tcyc  $\geq$  400ns, Tcych  $\geq$  100ns, Twait  $\leq$  250ns, Th2  $\leq$  5ns, Th3  $\leq$  5ns, Th4  $\leq$  5ns

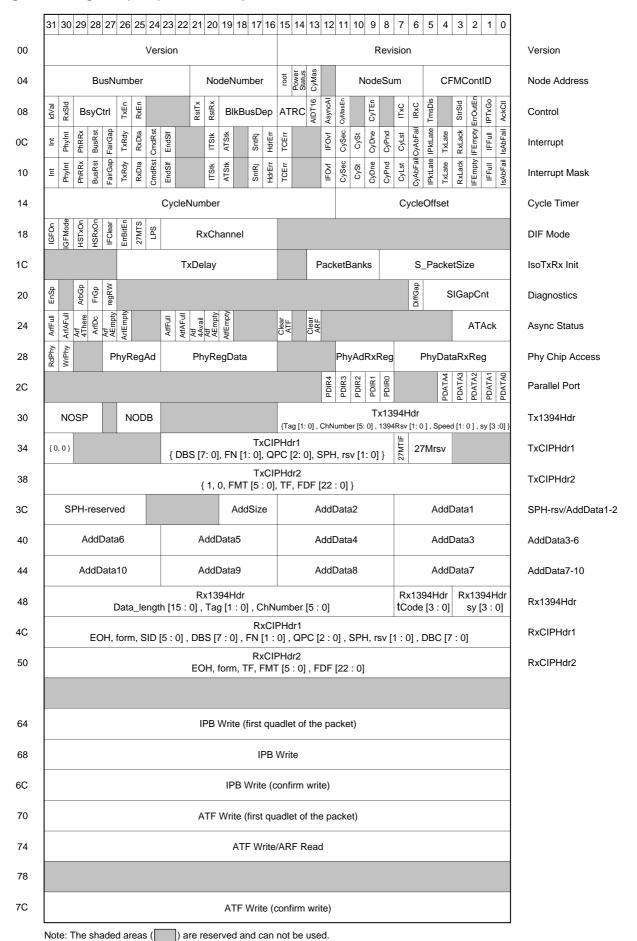

#### **Configuration Register (CFR) Address Map**

#### 6-2. CFR (Configuration Register)

This is a memory space to store the status information and operation mode and packet header information inside the chip. Read/write with the external microcomputer can be performed via the host I/F. (Be sure to set to "0" when writing to the reserved area.)

The address map and register contents are shown below.

#### **Register Description**

#### 1) Version/Revision Register

These registers have the CXD1948R version/revision written in them.

The register address is 00h; they are read only, and the initial value is 0000\_0001h.

| Bit      | Name     | Function                 |

|----------|----------|--------------------------|

| 31 to 16 | Version  | CXD1948R Version Number  |

| 15 to 0  | Revision | CXD1948R Revision Number |

#### 2) Node Address Register

These registers are used for packet receive/refuse control, and to monitor root/cycle master status and the total number of nodes connected.

The register address is 04h and the initial value is FFFF\_0040h.

Only the bus number is read/write, and the other registers are normally read only, but the diagnostic register can be read/write by setting regRW to "1".

| Bit      | Name         | Function                                                                                                                                                                          |  |  |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31 to 22 | Bus Number   | Bus number of connected bus                                                                                                                                                       |  |  |

| 21 to 16 | Node Number  | Node number of this link                                                                                                                                                          |  |  |

| 15       | root         | Root/not root for this link 1: root; 0: not root                                                                                                                                  |  |  |

| 14       | Power Status | Cable power status for this mode                                                                                                                                                  |  |  |

| 12       | CyMst        | Whether or not this link is cycle master 1: cycle master; 0: not                                                                                                                  |  |  |

| 11 to 6  | NodeSum      | Total number of connected nodes. Value is 0 when an error occurs in Self_ID communication.                                                                                        |  |  |

| 5 to 0   | CFMcontID    | The Phy_ID of the contender is inserted here. However, when the node can itself be a contender and it has a larger Phy_ID than this value, then the node itself is the contender. |  |  |

# 3) Control Register

These registers perform settings for the CXD1948R basic operations.

The register address is 08h; they are read/write, and the initial value is C400\_0A00h.

| Bit      | Name      | Function                                                                                                                                                                                                                                                                                                                                            |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31       | idVal     | Receives packet from the address set in the node address register at "1". Receives packet at bus number "3Fh" node number "3fh" only at "0".                                                                                                                                                                                                        |

| 30       | RxSld     | Validates reception of SelfID packet at "1". Non-valid at "0". Processing for NodeSum, CFMContID, DiffGap and SIGapCnt is invalid.                                                                                                                                                                                                                  |

| 29 to 27 | BsyCtrl   | Controls Busy status of input packet.  000 = Returns busy according to normal busy/retry protocol when necessary.  (Always fixed at "000" on the CXD1948R)                                                                                                                                                                                          |

| 26       | TxEn      | Transmitter does not transmit Arbitration and packet when "0"                                                                                                                                                                                                                                                                                       |

| 25       | RxEn      | Receiver does not receive packet when "0"                                                                                                                                                                                                                                                                                                           |

| 21       | RstTx     | Sync resets transmitter when set to "1" This bit is cleared automatically                                                                                                                                                                                                                                                                           |

| 20       | RstRx     | Sync resets receiver when set to "1" This bit is cleared automatically                                                                                                                                                                                                                                                                              |

| 19 to 16 | BlkBusDep | Access limits on Broadcast packets for the CSR bus-dependent area can be set here. Each bit corresponds to 128 bytes of the CSR bus-dependent area. With the LSB corresponding to the first 128 bytes, and so on until the MSB corresponding to the last 128 bytes, access to any area for which the corresponding bit has been set "1" is invalid. |

| 15, 14   | ATRC      | The Retry Code can be controlled. The Retry Code for the packet being sent is the logical OR of the value set here and the value stored in ATF.                                                                                                                                                                                                     |

| 13       | AIDT16    | Selects AIDT bus width. 8 bits at "0" and 16 bits at "1"                                                                                                                                                                                                                                                                                            |

| 12       | AsyncAl   | Transport stream I/F setting. Synchronous at "0" and asynchronous at "1".                                                                                                                                                                                                                                                                           |

| 11       | CyMasEn   | When "1" and the node becomes the ROOT, Cycle Master functions are activated.                                                                                                                                                                                                                                                                       |

| 9        | CyTEn     | Validates Cycle Offset increment at "1"                                                                                                                                                                                                                                                                                                             |

| 7        | ITxC      | Transmits isochronous packet with tCode = C at "1" Transmits isochronous packet with tCode = A at "0"                                                                                                                                                                                                                                               |

| 6        | IRxC      | Receives tCode = A, tCode = C packets as isochronous packet at "1" Receives tCode = A packet as isochronous packet at "0"                                                                                                                                                                                                                           |

| 0        | AckCtl    | Controls Ack code which is returned when tCode = 0, 1 (Write request quadlet/block) packets are received.  0: Ack code = 1 (complate), 1: Ack code = 0 (pending)                                                                                                                                                                                    |

| 5        | TmsDis    | Does not use time stamp for data read during receive at "1" Uses time stamp for data read during receive at "0"                                                                                                                                                                                                                                     |

| 3        | StrSid    | Takes received SelfID packet in to ARF at "1"  Does not take received SelfID packet in to ARF at "0"                                                                                                                                                                                                                                                |

| 2        | ErrOutEn  | Outputs error packet at ErrFlag High during receive at "1" Does not output error packet during receive at "0"                                                                                                                                                                                                                                       |

| 1        | IPTxGo    | Transmits insert packet at "1" Automatically changes to "0" after transmit                                                                                                                                                                                                                                                                          |

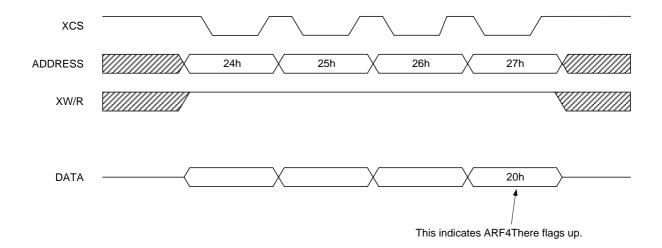

## 4) Interrupt and Interrupt-Mask Registers

These registers combine the Interrupt Register, which informs the host I/F of changes in the CXD1948R status, and the Interrupt Mask Register, which masks the Interrupt Register.

The address of the Interrupt Register is 0Ch, and when the regRW bit is "0", bits other than Int bit are cleared by writing. When the regRW bit is "1" all bits are read/write.

The address of the Interrupt-Mask Register is 10H and it is read/write.

The initial value for both registers is 0000\_0000h.

| Bit | Name     | Function                                                                                                                                            |  |  |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31  | Int      | Indicates the OR result of all the interrupt (interrupt mask) bits.                                                                                 |  |  |

| 30  | PhyInt   | Indicates Phy Interrupt received from Phy chip                                                                                                      |  |  |

| 29  | PhRRx    | Indicates data received from Phy to Phy register                                                                                                    |  |  |

| 28  | BusRst   | Indicates Bus Reset received from Phy                                                                                                               |  |  |

| 27  | FairGap  | Indicates FairGap received from Phy                                                                                                                 |  |  |

| 26  | TxRdy    | Transmitter is able to transmit                                                                                                                     |  |  |

| 25  | RxDta    | Receiver has received a correct packet                                                                                                              |  |  |

| 24  | CmdRst   | Receiver has received a packet addressed to CSR RESET_START register                                                                                |  |  |

| 23  | EndSlf   | SelfID phase complete                                                                                                                               |  |  |

| 20  | ITStk    | Transmitter detected wrong data in isochronous FIFO during isochronous transmit                                                                     |  |  |

| 19  | ATStk    | Transmitter detected wrong data in asynchronous FIFO during asynchronous transmit                                                                   |  |  |

| 17  | SntRj    | Receiver transmitted Busy Ack for a packet transmitted to this node because receive FIFO is full                                                    |  |  |

| 16  | HdrErr   | Receiver detected Header CRC error in the packet transmitted to this node                                                                           |  |  |

| 15  | TCErr    | Transmitter detected wrong tCode data in transmit FIFO                                                                                              |  |  |

| 12  | IFOvf    | Indicates overflow in isochronous FIFO                                                                                                              |  |  |

| 11  | CySec    | Indicates that Cycle Timer register Cycle Number upper 7 bits were incremented.  (This is generated almost every second when Cycle Timer is valid.) |  |  |

| 10  | CySt     | Transmitter/Receiver transmitted/received Cycle Start packet                                                                                        |  |  |

| 9   | CyDne    | After transmit or receive of Cycle Start packet, FairGap was detected on the bus. This means that the isochronous cycle is complete.                |  |  |

| 8   | CyPnd    | Indicates that Cycle Timer register Cycle Offset is "0". Stays as is until isochronous cycle is complete.                                           |  |  |

| 7   | CyLst    | When not Cycle Master, indicates that Cycle Timer completed 2 cycles without receiving Cycle Start packet.                                          |  |  |

| 6   | CyAbFail | Failure of Cycle Start packet transmission Arbitration                                                                                              |  |  |

| 5   | IPktLate | Late transmit of insert packet                                                                                                                      |  |  |

| 4   | TxLate   | Late transmit of isochronous packet                                                                                                                 |  |  |

| 3   | RxLack   | Indicates isochronous packet non-continuous DBC                                                                                                     |  |  |

| 2   | IFEmpty  | Isochronous FIFO empty                                                                                                                              |  |  |

| 1   | IFFull   | Isochronous FIFO full                                                                                                                               |  |  |

| 0   | IsAbFail | Failure of isochronous packet transmission Arbitration                                                                                              |  |  |

# 5) Cycle Timer Registers

These registers are composed of the 24.576MHz clock cycle Cycle Offset and the 125µs in its host, and the Cycle Master that counts 1 second. The value of all nodes are regulated by the Cycle Master node.

The register address is 14h; it is read/write, and the initial value is 0000\_0000h.

| Bit      | Name        | Function                                                                                                                                                                                     |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 12 | CycleNumber | The upper 7 bits counts seconds (1Hz) and the lower 13 bits count the isochronous cycle (8kHz = 125µs). The values are controlled by Control register Cycle Master and Cycle Timer Enable.   |