# HM5257165B-75/A6 HM5257805B-75/A6 HM5257405B-75/A6

512M LVTTL interface SDRAM 133 MHz/100 MHz 8-Mword × 16-bit × 4-bank/16-Mword × 8-bit × 4-bank /32-Mword × 4-bit × 4-bank PC/133, PC/100 SDRAM

E0081H10 (1st edition) (Previous ADE-203-1237A (Z)) Jan. 31, 2001

### **Description**

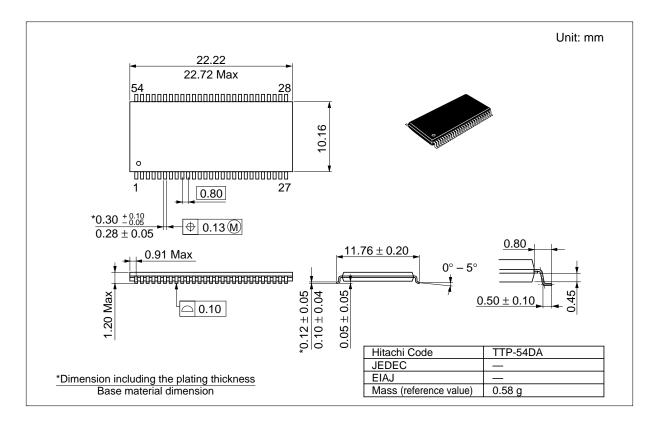

The HM5257165B is a 512-Mbit SDRAM organized as 8388608-word  $\times$  16-bit  $\times$  4 bank. The HM5257805B is a 512-Mbit SDRAM organized as 16777216-word  $\times$  8-bit  $\times$  4 bank. The HM5257405B is a 512-Mbit SDRAM organized as 33554432-word  $\times$  4-bit  $\times$  4 bank. All inputs and outputs are referred to the rising edge of the clock input. It is packaged in standard 54-pin plastic TSOP II.

### **Features**

- 3.3 V power supply

- Clock frequency: 133 MHz/100 MHz (max)

- LVTTL interface

- Single pulsed RAS

- 4 banks can operate simultaneously and independently

- Burst read/write operation and burst read/single write operation capability

- Programmable burst length: 1/2/4/8

- 2 variations of burst sequence

- Sequential (BL = 1/2/4/8)

- Interleave (BL = 1/2/4/8)

# $\underline{HM5257165B/HM5257805B/HM5257405B-75/A6}$

• Programmable CAS latency: 2/3

• Byte control by DQM: DQM (HM5257805B/HM5257405B)

: DQMU/DQML (HM5257165B)

• Refresh cycles: 8192 refresh cycles/64 ms

• 2 variations of refresh

— Auto refresh

—Self refresh

• Temperature range: 0 to 60°C

# **Ordering Information**

| Type No.                      | Frequency | <b>CAS</b> latency | Package                                   |

|-------------------------------|-----------|--------------------|-------------------------------------------|

| HM5257165BTD-75* <sup>1</sup> | 133 MHz   | 3                  | 400-mil 54-pin plastic TSOP II (TTP-54DA) |

| HM5257165BTD-A6               | 100 MHz   | 2/3                |                                           |

| HM5257805BTD-75*1             | 133 MHz   | 3                  |                                           |

| HM5257805BTD-A6               | 100 MHz   | 2/3                |                                           |

| HM5257405BTD-75*1             | 133 MHz   | 3                  |                                           |

| HM5257405BTD-A6               | 100 MHz   | 2/3                |                                           |

Notes: 1. 100 MHz operation at  $\overline{CAS}$  latency = 2

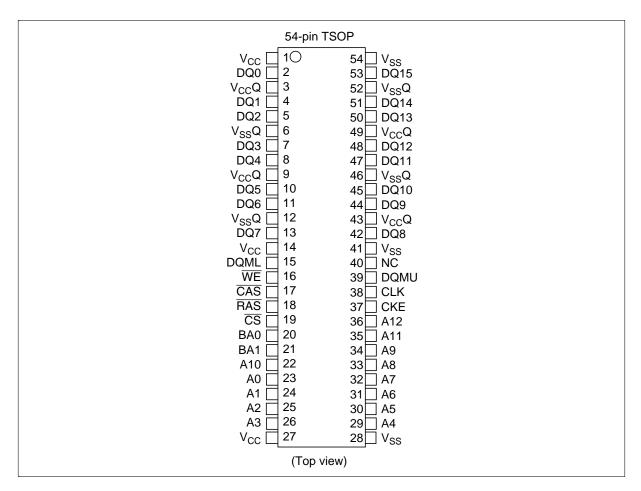

## Pin Arrangement (HM5257165B)

### **Pin Description**

| Pin name               | Function                      |         | Pin name          | Function                    |

|------------------------|-------------------------------|---------|-------------------|-----------------------------|

| A0 to A12,<br>BA0, BA1 | Address input                 |         | WE                | Write enable                |

|                        | — Row address A0 to A         | .12     | DQMU/DQML         | Input/output mask           |

|                        | — Column address A0 to A      | .9      | CLK               | Clock input                 |

|                        | — Bank select address BA0/B   | A1 (BS) | CKE               | Clock enable                |

| DQ0 to DQ15            | Data-input/output             |         | V <sub>cc</sub>   | Power for internal circuit  |

| CS                     | Chip select                   |         | V <sub>ss</sub>   | Ground for internal circuit |

| RAS                    | Row address strobe command    |         | $V_{cc}Q$         | Power for DQ circuit        |

| CAS                    | Column address strobe command | I       | V <sub>ss</sub> Q | Ground for DQ circuit       |

|                        |                               |         | NC                | No connection               |

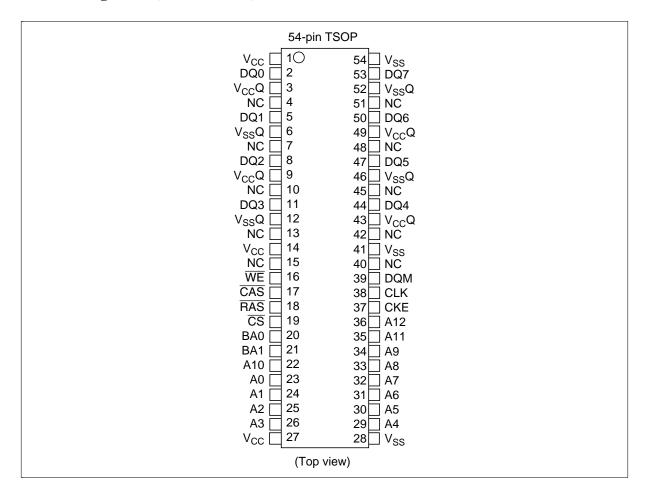

### Pin Arrangement (HM5257805B)

# **Pin Description**

| Pin name               | Function                           | Pin name          | Function                    |

|------------------------|------------------------------------|-------------------|-----------------------------|

| A0 to A12,<br>BA0, BA1 | Address input                      | WE                | Write enable                |

|                        | — Row address A0 to A12            | DQM               | Input/output mask           |

|                        | — Column address A0 to A9, A11     | CLK               | Clock input                 |

|                        | — Bank select address BA0/BA1 (BS) | CKE               | Clock enable                |

| DQ0 to DQ7             | Data-input/output                  | V <sub>cc</sub>   | Power for internal circuit  |

| CS                     | Chip select                        | V <sub>ss</sub>   | Ground for internal circuit |

| RAS                    | Row address strobe command         | V <sub>cc</sub> Q | Power for DQ circuit        |

| CAS                    | Column address strobe command      | V <sub>ss</sub> Q | Ground for DQ circuit       |

|                        |                                    | NC                | No connection               |

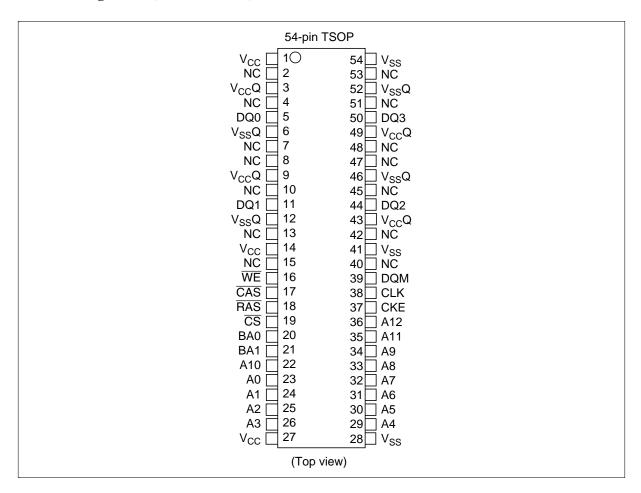

### Pin Arrangement (HM5257405B)

# **Pin Description**

| Pin name               | Function               |                   | Pin name          | Function                    |

|------------------------|------------------------|-------------------|-------------------|-----------------------------|

| A0 to A12,<br>BA0, BA1 | Address input          |                   | WE                | Write enable                |

|                        | — Row address          | A0 to A12         | DQM               | Input/output mask           |

|                        | — Column address       | A0 to A9, A11 A12 | CLK               | Clock input                 |

|                        | — Bank select addre    | ss BA0/BA1 (BS)   | CKE               | Clock enable                |

| DQ0 to DQ3             | Data-input/output      |                   | V <sub>CC</sub>   | Power for internal circuit  |

| CS                     | Chip select            |                   | V <sub>SS</sub>   | Ground for internal circuit |

| RAS                    | Row address strobe com | nmand             | $V_{cc}Q$         | Power for DQ circuit        |

| CAS                    | Column address strobe  | command           | V <sub>ss</sub> Q | Ground for DQ circuit       |

|                        |                        |                   | NC                | No connection               |

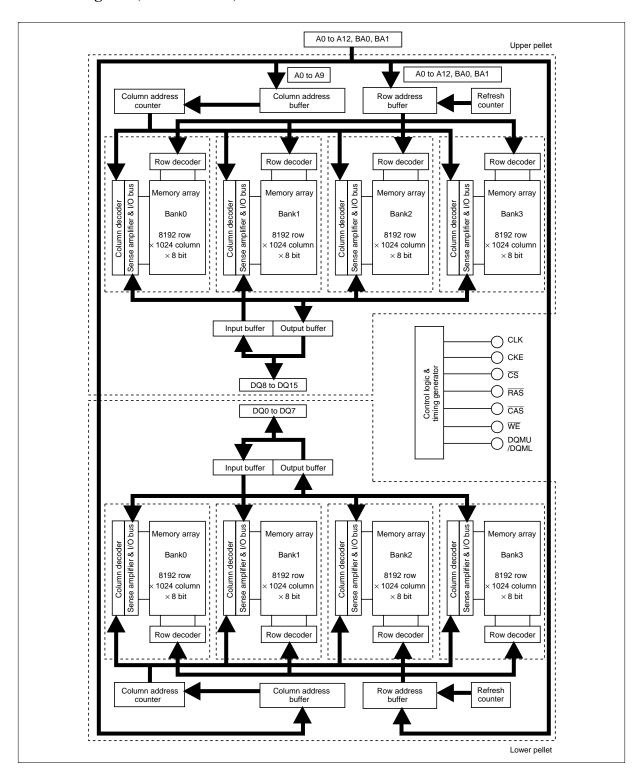

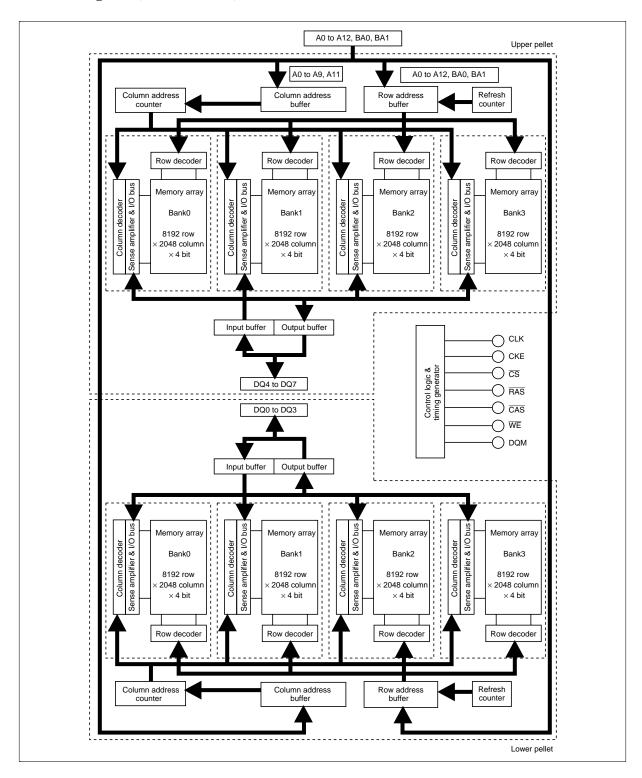

### **Block Diagram** (HM5257165B)

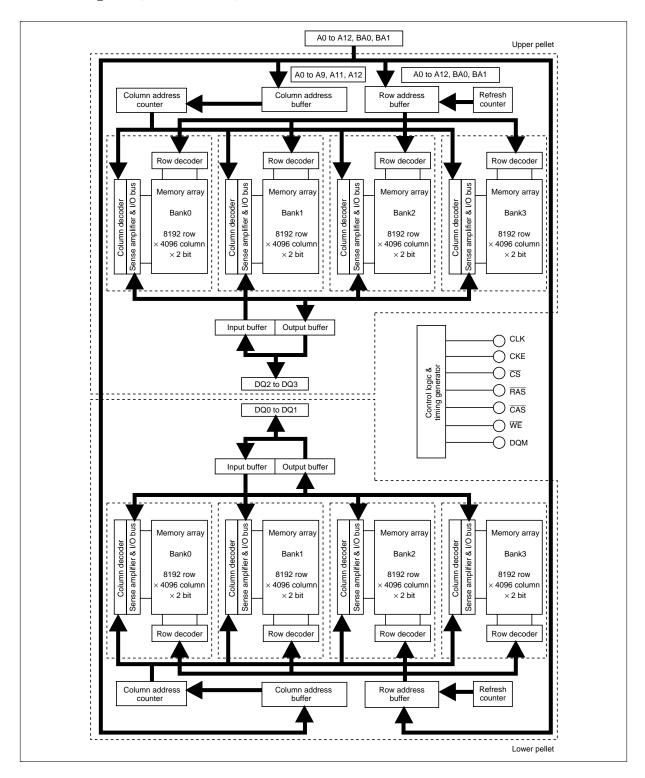

### **Block Diagram** (HM5257805B)

### **Block Diagram** (HM5257405B)

### **Pin Functions**

**CLK** (input pin): CLK is the master clock input to this pin. The other input signals are referred at CLK rising edge.

$\overline{\text{CS}}$  (input pin): When  $\overline{\text{CS}}$  is Low, the command input cycle becomes valid. When  $\overline{\text{CS}}$  is High, all inputs are ignored. However, internal operations (bank active, burst operations, etc.) are held.

RAS, CAS, and WE (input pins): Although these pin names are the same as those of conventional DRAMs, they function in a different way. These pins define operation commands (read, write, etc.) depending on the combination of their voltage levels. For details, refer to the command operation section.

**A0 to A12 (input pins):** Row address (AX0 to AX12) is determined by A0 to A12 level at the bank active command cycle CLK rising edge. Column address (AY0 to AY9; HM5257165B, AY0 to AY9, AY11; HM5257805B, AY0 to AY9, AY11, AY12; HM5257405B) is determined by A0 to A8, A9 A11 or A12 (A9; HM5257165B, A9, A11; HM5257805B, A9, A11, A12; HM5257405B) level at the read or write command cycle CLK rising edge. And this column address becomes burst access start address. A10 defines the precharge mode. When A10 = High at the precharge command cycle, all banks are precharged. But when A10 = Low at the precharge command cycle, only the bank that is selected by BA0/BA1 (BS) is precharged. For details refer to the command operation section.

**BA0/BA1** (**input pin**): BA0/BA1 are bank select signal (BS). The memory array of the HM5257165B, HM5257805B, the HM5257405B is divided into bank 0, bank 1, bank 2 and bank 3. HM5257165B contain 8192-row × 1024-column × 16-bit. HM5257805B contain 8192-row × 2048-column × 8-bit. HM5257405B contain 8192-row × 4096-column × 4-bit. If BA0 is Low and BA1 is Low, bank 0 is selected. If BA0 is Low and BA1 is High, bank 1 is selected. If BA0 is High and BA1 is Low, bank 2 is selected. If BA0 is High and BA1 is High, bank 3 is selected.

**CKE** (**input pin**): This pin determines whether or not the next CLK is valid. If CKE is High, the next CLK rising edge is valid. If CKE is Low, the next CLK rising edge is invalid. This pin is used for power-down mode, clock suspend mode and self refresh mode.

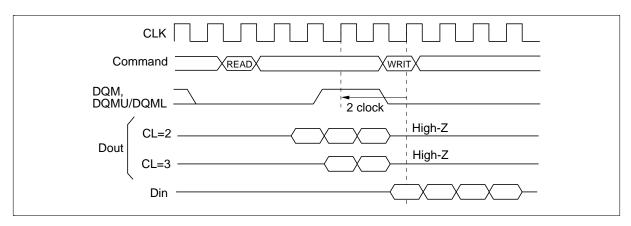

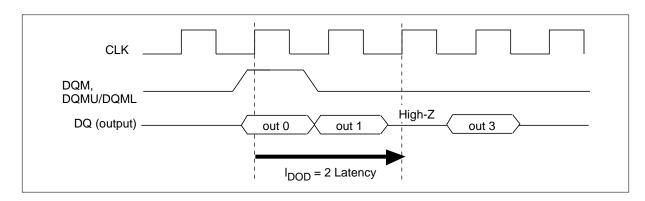

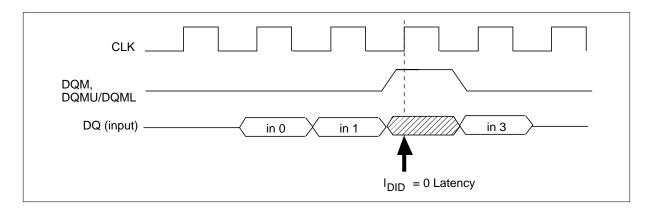

**DQM, DQMU/DQML** (input pins): DQM, DQMU/DQML controls input/output buffers.

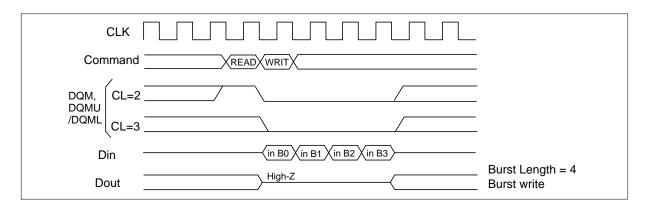

Read operation: If DQM, DQMU/DQML is High, the output buffer becomes High-Z. If the DQM, DQMU/DQML is Low, the output buffer becomes Low-Z. (The latency of DQM, DQMU/DQML during reading is 2 clocks.)

Write operation: If DQM, DQMU/DQML is High, the previous data is held (the new data is not written). If DQM, DQMU/DQML is Low, the data is written. (The latency of DQM, DQMU/DQML during writing is 0 clock.)

**DQ0 to DQ15 (DQ pins):** Data is input to and output from these pins (DQ0 to DQ15; HM5257165B, DQ0 to DQ7; HM5257805B, DQ0 to DQ3; HM5257405B).

$V_{CC}$  and  $V_{CC}Q$  (power supply pins): 3.3 V is applied. ( $V_{CC}$  is for the internal circuit and  $V_{CC}Q$  is for the output buffer.)

$V_{ss}$  and  $V_{ss}Q$  (power supply pins): Ground is connected. ( $V_{ss}$  is for the internal circuit and  $V_{ss}Q$  is for the output buffer.)

### **Command Operation**

#### **Command Truth Table**

The SDRAM recognizes the following commands specified by the CS, RAS, CAS, WE and address pins.

|                                    |          | CKE   |   | _  |     |     |    |         |     |              |

|------------------------------------|----------|-------|---|----|-----|-----|----|---------|-----|--------------|

| Command                            | Symbol   | n - 1 | n | CS | RAS | CAS | WE | BA0/BA1 | A10 | A0<br>to A12 |

| Ignore command                     | DESL     | Н     | × | Н  | ×   | ×   | ×  | ×       | ×   | ×            |

| No operation                       | NOP      | Н     | × | L  | Н   | Н   | Н  | ×       | ×   | ×            |

| Column address and read command    | READ     | Н     | × | L  | Н   | L   | Н  | V       | L   | V            |

| Read with auto-precharge           | READ A   | Н     | × | L  | Н   | L   | Н  | V       | Н   | V            |

| Column address and write command   | WRIT     | Н     | × | L  | Н   | L   | L  | V       | L   | V            |

| Write with auto-precharge          | WRIT A   | Н     | × | L  | Н   | L   | L  | V       | Н   | V            |

| Row address strobe and bank active | ACTV     | Н     | × | L  | L   | Н   | Н  | V       | V   | V            |

| Precharge select bank              | PRE      | Н     | × | L  | L   | Н   | L  | V       | L   | ×            |

| Precharge all bank                 | PALL     | Н     | × | L  | L   | Н   | L  | ×       | Н   | ×            |

| Refresh                            | REF/SELF | Н     | V | L  | L   | L   | Н  | ×       | ×   | ×            |

| Mode register set                  | MRS      | Н     | × | L  | L   | L   | L  | V       | V   | V            |

Note: H:  $V_{IH}$ . L:  $V_{IL}$ .  $\times$ :  $V_{IH}$  or  $V_{IL}$ . V: Valid address input

**Ignore command [DESL]:** When this command is set  $(\overline{CS})$  is High), the SDRAM ignore command input at the clock. However, the internal status is held.

**No operation [NOP]:** This command is not an execution command. However, the internal operations continue.

**Column address strobe and read command [READ]:** This command starts a read operation. In addition, the start address of burst read is determined by the column address (AY0 to AY9; HM5257165B, AY0 to AY9, AY11; HM5257805B, AY0 to AY9, AY11, AY12; HM5257405B) and the bank select address (BS). After the read operation, the output buffer becomes High-Z.

**Read with auto-precharge [READ A]:** This command automatically performs a precharge operation after a burst read with a burst length of 1, 2, 4 or 8.

**Column address strobe and write command [WRIT]:** This command starts a write operation. When the burst write mode is selected, the column address (AY0 to AY9; HM5257165B, AY0 to AY9, AY11; HM5257805B, AY0 to AY9, AY11, AY12; HM5257405B) and the bank select address (BA0/BA1) become the burst write start address. When the single write mode is selected, data is only written to the location specified by the column address (AY0 to AY9; HM5257165B, AY0 to AY9, AY11; HM5257805B, AY0 to AY9, AY11, AY12; HM5257405B) and the bank select address (BA0/BA1).

**Write with auto-precharge [WRIT A]:** This command automatically performs a precharge operation after a burst write with a length of 1, 2, 4 or 8, or after a single write operation.

**Row address strobe and bank activate [ACTV]:** This command activates the bank that is selected by BA0/BA1 (BS) and determines the row address (AX0 to AX12). When BA0 and BA1 are Low, bank 0 is activated. When BA0 is Low and BA1 is High, bank 1 is activated. When BA0 is High and BA1 is Low, bank 2 is activated. When BA0 and BA1 are High, bank 3 is activated.

**Precharge selected bank** [**PRE**]: This command starts precharge operation for the bank selected by BA0/BA1. If BA0 and BA1 are Low, bank 0 is selected. If BA0 is Low and BA1 is High, bank 1 is selected. If BA0 is High and BA1 is Low, bank 2 is selected. If BA0 and BA1 are High, bank 3 is selected.

Precharge all banks [PALL]: This command starts a precharge operation for all banks.

**Refresh** [**REF/SELF**]: This command starts the refresh operation. There are two types of refresh operation, the one is auto-refresh, and the other is self-refresh. For details, refer to the CKE truth table section.

**Mode register set [MRS]:** The SDRAM has a mode register that defines how it operates. The mode register is specified by the address pins (A0 to BA0 and BA1) at the mode register set cycle. For details, refer to the mode register configuration. After power on, the contents of the mode register are undefined, execute the mode register set command to set up the mode register.

### **DQM Truth Table** (HM5257165B)

|                                                       |        | CKE   |   |      |      |

|-------------------------------------------------------|--------|-------|---|------|------|

| Command                                               | Symbol | n - 1 | n | DQMU | DQML |

| Upper byte (DQ8 to DQ15) write enable/output enable   | ENBU   | Н     | × | L    | ×    |

| Lower byte (DQ0 to DQ7) write enable/output enable    | ENBL   | Н     | × | ×    | L    |

| Upper byte (DQ8 to DQ15) write inhibit/output disable | MASKU  | Н     | × | Н    | ×    |

| Lower byte (DQ0 to DQ7) write inhibit/output disable  | MASKL  | Н     | × | ×    | Н    |

$\label{eq:Note:optimize} \begin{array}{ll} \text{Note:} & \text{H: } V_{\text{IH}}. \ L: V_{\text{IL}}. \times: V_{\text{IH}} \ \text{or} \ V_{\text{IL}}. \\ & \text{Write: } I_{\text{DID}} \ \text{is needed}. \\ & \text{Read: } I_{\text{DOD}} \ \text{is needed}. \end{array}$

### **DQM Truth Table** (HM5257805B/HM5257405B)

|                              |        | CKE   |   |     |

|------------------------------|--------|-------|---|-----|

| Command                      | Symbol | n - 1 | n | DQM |

| Write enable/output enable   | ENB    | Н     | × | L   |

| Write inhibit/output disable | MASK   | Н     | × | Н   |

$\label{eq:Note:optimize} \begin{array}{lll} \text{Note:} & \text{H: } V_{\text{IH}}. \text{ L: } V_{\text{IL}}. \times : V_{\text{IH}} \text{ or } V_{\text{IL}}. \\ & \text{Write: } I_{\text{DID}} \text{ is needed.} \\ & \text{Read: } I_{\text{DOD}} \text{ is needed.} \end{array}$

The SDRAM can mask input/output data by means of DQM, DQMU/DQML.

DQMU masks the upper byte and DQML masks the lower byte. (HM5257165B)

During reading, the output buffer is set to Low-Z by setting DQM, DQMU/DQML to Low, enabling data output. On the other hand, when DQM, DQMU/DQML is set to High, the output buffer becomes High-Z, disabling data output.

During writing, data is written by setting DQM, DQMU/DQML to Low. When DQM, DQMU/DQML is set to High, the previous data is held (the new data is not written). Desired data can be masked during burst read or burst write by setting DQM, DQMU/DQML. For details, refer to the DQM, DQMU/DQML control section of the SDRAM operating instructions.

#### **CKE Truth Table**

|               |                            | CKE   |   |    |     |     |    |         |

|---------------|----------------------------|-------|---|----|-----|-----|----|---------|

| Current state | Command                    | n - 1 | n | CS | RAS | CAS | WE | Address |

| Active        | Clock suspend mode entry   | Н     | L | ×  | ×   | ×   | ×  | ×       |

| Any           | Clock suspend              | L     | L | ×  | ×   | ×   | ×  | ×       |

| Clock suspend | Clock suspend mode exit    | L     | Н | ×  | ×   | ×   | ×  | ×       |

| Idle          | Auto-refresh command (REF) | Н     | Н | L  | L   | L   | Н  | ×       |

| Idle          | Self-refresh entry (SELF)  | Н     | L | L  | L   | L   | Н  | ×       |

| Idle          | Power down entry           | Н     | L | L  | Н   | Н   | Н  | ×       |

|               |                            | Н     | L | Н  | ×   | ×   | ×  | ×       |

| Self refresh  | Self refresh exit (SELFX)  | L     | Н | L  | Н   | Н   | Н  | ×       |

|               |                            | L     | Н | Н  | ×   | ×   | ×  | ×       |

| Power down    | Power down exit            | L     | Н | L  | Н   | Н   | Н  | ×       |

|               |                            | L     | Н | Н  | ×   | ×   | ×  | ×       |

Note: H:  $V_{IH}$ . L:  $V_{IL}$ .  $\times$ :  $V_{IH}$  or  $V_{IL}$ .

**Clock suspend mode entry:** The SDRAM enters clock suspend mode from active mode by setting CKE to Low. If command is input in the clock suspend mode entry cycle, the command is valid. The clock suspend mode changes depending on the current status (1 clock before) as shown below.

**ACTIVE clock suspend:** This suspend mode ignores inputs after the next clock by internally maintaining the bank active status.

**READ suspend and READ with Auto-precharge suspend:** The data being output is held (and continues to be output).

WRITE suspend and WRIT with Auto-precharge suspend: In this mode, external signals are not accepted. However, the internal state is held.

**Clock suspend:** During clock suspend mode, keep the CKE to Low.

**Clock suspend mode exit:** The SDRAM exits from clock suspend mode by setting CKE to High during the clock suspend state.

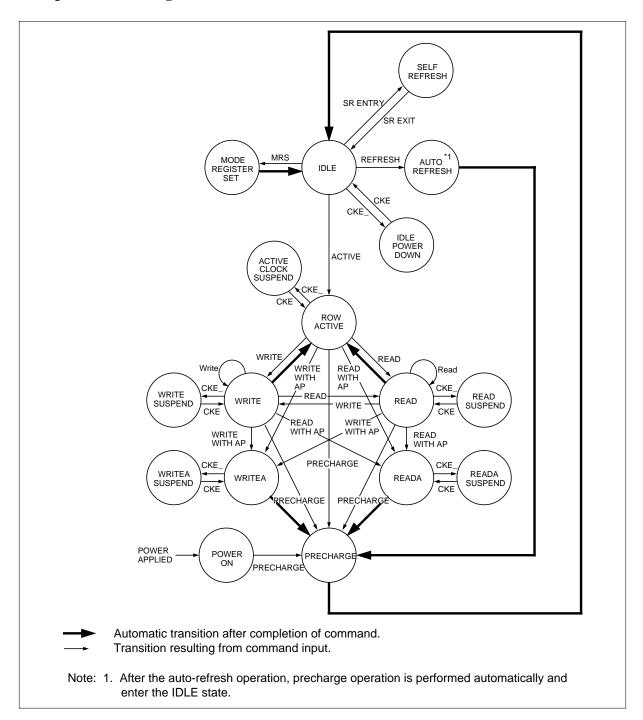

**IDLE:** In this state, all banks are not selected, and completed precharge operation.

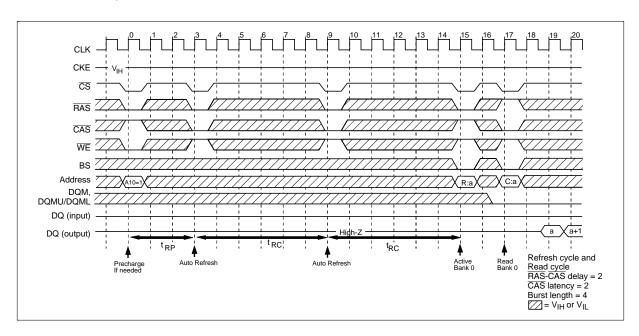

**Auto-refresh command [REF]:** When this command is input from the IDLE state, the SDRAM starts auto-refresh operation. (The auto-refresh is the same as the CBR refresh of conventional DRAMs.) During the auto-refresh operation, refresh address and bank select address are generated inside the SDRAM. For every auto-refresh cycle, the internal address counter is updated. Accordingly, 8192 times are required to refresh the entire memory. Before executing the auto-refresh command, all the banks must be in the IDLE state. In addition, since the precharge for all banks is automatically performed after auto-refresh, no precharge command is required after auto-refresh.

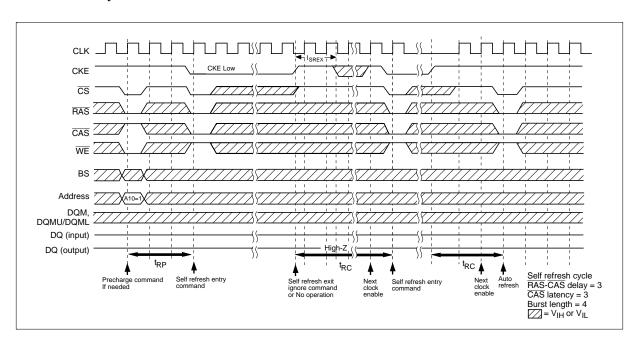

**Self-refresh entry [SELF]:** When this command is input during the IDLE state, the SDRAM starts self-refresh operation. After the execution of this command, self-refresh continues while CKE is Low. Since self-refresh is performed internally and automatically, external refresh operations are unnecessary.

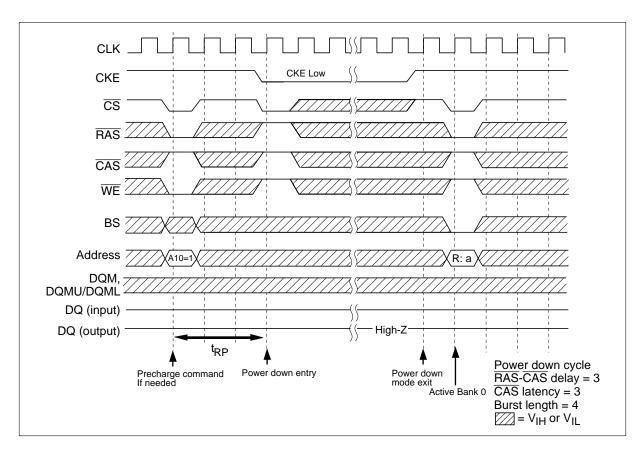

**Power down mode entry:** When this command is executed during the IDLE state, the SDRAM enters power down mode. In power down mode, power consumption is suppressed by cutting off the initial input circuit.

**Self-refresh exit:** When this command is executed during self-refresh mode, the SDRAM can exit from self-refresh mode. After exiting from self-refresh mode, the SDRAM enters the IDLE state.

**Power down exit:** When this command is executed at the power down mode, the SDRAM can exit from power down mode. After exiting from power down mode, the SDRAM enters the IDLE state.

#### **Function Truth Table**

The following table shows the operations that are performed when each command is issued in each mode of the SDRAM.

The following table assumes that CKE is high.

| Current state | CS | RAS | CAS | WE | Address     | Command     | Operation                        |

|---------------|----|-----|-----|----|-------------|-------------|----------------------------------|

| Precharge     | Н  | ×   | ×   | ×  | ×           | DESL        | Enter IDLE after t <sub>RP</sub> |

|               | L  | Н   | Н   | Н  | ×           | NOP         | Enter IDLE after t <sub>RP</sub> |

|               | L  | Н   | L   | Н  | BA, CA, A10 | READ/READ A | ILLEGAL*4                        |

|               | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRIT A | ILLEGAL*4                        |

|               | L  | L   | Н   | Н  | BA, RA      | ACTV        | ILLEGAL*4                        |

|               | L  | L   | Н   | L  | BA, A10     | PRE, PALL   | NOP*6                            |

|               | L  | L   | L   | Н  | ×           | REF, SELF   | ILLEGAL                          |

|               | L  | L   | L   | L  | MODE        | MRS         | ILLEGAL                          |

| Idle          | Н  | ×   | ×   | ×  | ×           | DESL        | NOP                              |

|               | L  | Н   | Н   | Н  | ×           | NOP         | NOP                              |

|               | L  | Н   | L   | Н  | BA, CA, A10 | READ/READ A | ILLEGAL*5                        |

|               | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRIT A | ILLEGAL*5                        |

|               | L  | L   | Н   | Н  | BA, RA      | ACTV        | Bank and row active              |

|               | L  | L   | Н   | L  | BA, A10     | PRE, PALL   | NOP                              |

|               | L  | L   | L   | Н  | ×           | REF, SELF   | Refresh                          |

|               | L  | L   | L   | L  | MODE        | MRS         | Mode register set                |

| Current state                | CS | RAS | CAS | WE | Address     | Command     | Operation                                       |

|------------------------------|----|-----|-----|----|-------------|-------------|-------------------------------------------------|

| Row active                   | Н  | ×   | ×   | ×  | ×           | DESL        | NOP                                             |

|                              | L  | Н   | Н   | Н  | ×           | NOP         | NOP                                             |

|                              | L  | Н   | L   | Н  | BA, CA, A10 | READ/READ A | Begin read                                      |

|                              | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRIT A | Begin write                                     |

|                              | L  | L   | Н   | Н  | BA, RA      | ACTV        | Other bank active ILLEGAL on same bank*3        |

|                              | L  | L   | Н   | L  | BA, A10     | PRE, PALL   | Precharge                                       |

|                              | L  | L   | L   | Н  | ×           | REF, SELF   | ILLEGAL                                         |

|                              | L  | L   | L   | L  | MODE        | MRS         | ILLEGAL                                         |

| Read                         | Н  | ×   | ×   | ×  | ×           | DESL        | Continue burst to end                           |

|                              | L  | Н   | Н   | Н  | ×           | NOP         | Continue burst to end                           |

|                              | L  | Н   | L   | Н  | BA, CA, A10 | READ/READ A | Continue burst read to CAS latency and New read |

|                              | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRIT A | Term burst read/start write                     |

|                              | L  | L   | Н   | Н  | BA, RA      | ACTV        | Other bank active ILLEGAL on same bank*3        |

|                              | L  | L   | Н   | L  | BA, A10     | PRE, PALL   | Term burst read and<br>Precharge                |

|                              | L  | L   | L   | Н  | ×           | REF, SELF   | ILLEGAL                                         |

|                              | L  | L   | L   | L  | MODE        | MRS         | ILLEGAL                                         |

| Read with auto-<br>precharge | Н  | ×   | ×   | ×  | ×           | DESL        | Continue burst to end and precharge             |

|                              | L  | Н   | Н   | Н  | ×           | NOP         | Continue burst to end and precharge             |

|                              | L  | Н   | L   | Н  | BA, CA, A10 | READ/READ A | ILLEGAL*4                                       |

|                              | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRIT A | ILLEGAL*4                                       |

|                              | L  | L   | Н   | Н  | BA, RA      | ACTV        | Other bank active ILLEGAL on same bank*3        |

|                              | L  | L   | Н   | L  | BA, A10     | PRE, PALL   | ILLEGAL*4                                       |

|                              | L  | L   | L   | Н  | ×           | REF, SELF   | ILLEGAL                                         |

|                              | L  | L   | L   | L  | MODE        | MRS         | ILLEGAL                                         |

| Current state                 | CS | RAS | CAS | WE | Address     | Command     | Operation                                |

|-------------------------------|----|-----|-----|----|-------------|-------------|------------------------------------------|

| Write                         | Н  | ×   | ×   | ×  | ×           | DESL        | Continue burst to end                    |

|                               | L  | Н   | Н   | Н  | ×           | NOP         | Continue burst to end                    |

|                               | L  | Н   | L   | Н  | BA, CA, A10 | READ/READ A | Term burst and New read                  |

|                               | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRIT A | Term burst and New write                 |

|                               | L  | L   | Н   | Н  | BA, RA      | ACTV        | Other bank active ILLEGAL on same bank*3 |

|                               | L  | L   | Н   | L  | BA, A10     | PRE, PALL   | Term burst write and<br>Precharge*2      |

|                               | L  | L   | L   | Н  | ×           | REF, SELF   | ILLEGAL                                  |

|                               | L  | L   | L   | L  | MODE        | MRS         | ILLEGAL                                  |

| Write with auto-<br>precharge | Н  | ×   | ×   | ×  | ×           | DESL        | Continue burst to end and precharge      |

|                               | L  | Н   | Н   | Н  | ×           | NOP         | Continue burst to end and precharge      |

|                               | L  | Н   | L   | Н  | BA, CA, A10 | READ/READ A | ILLEGAL*4                                |

|                               | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRIT A | ILLEGAL*4                                |

|                               | L  | L   | Н   | Н  | BA, RA      | ACTV        | Other bank active ILLEGAL on same bank*3 |

|                               | L  | L   | Н   | L  | BA, A10     | PRE, PALL   | ILLEGAL*4                                |

|                               | L  | L   | L   | Н  | ×           | REF, SELF   | ILLEGAL                                  |

|                               | L  | L   | L   | L  | MODE        | MRS         | ILLEGAL                                  |

| Refresh (auto-<br>refresh)    | Н  | ×   | ×   | ×  | ×           | DESL        | Enter IDLE after t <sub>RC</sub>         |

|                               | L  | Н   | Н   | Н  | ×           | NOP         | Enter IDLE after t <sub>RC</sub>         |

|                               | L  | Н   | L   | Н  | BA, CA, A10 | READ/READ A | ILLEGAL*5                                |

|                               | L  | Н   | L   | L  | BA, CA, A10 | WRIT/WRIT A | ILLEGAL*5                                |

|                               | L  | L   | Н   | Н  | BA, RA      | ACTV        | ILLEGAL*5                                |

|                               | L  | L   | Н   | L  | BA, A10     | PRE, PALL   | ILLEGAL*5                                |

|                               | L  | L   | L   | Н  | ×           | REF, SELF   | ILLEGAL                                  |

|                               | L  | L   | L   | L  | MODE        | MRS         | ILLEGAL                                  |

Notes: 1. H:  $V_{IH}$ . L:  $V_{IL}$   $\times$ :  $V_{IH}$  or  $V_{IL}$ . The other combinations are inhibit.

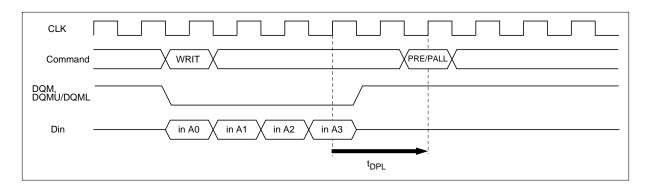

<sup>2.</sup> An interval of  $t_{\text{DPL}}$  is required between the final valid data input and the precharge command.

<sup>3.</sup> If  $t_{\text{RRD}}$  is not satisfied, this operation is illegal.

<sup>4.</sup> Illegal for same bank, except for another bank.

<sup>5.</sup> Illegal for all banks.

<sup>6.</sup> NOP for same bank, except for another bank.

### From PRECHARGE state, command operation

**To [DESL], [NOP]:** When these commands are executed, the SDRAM enters the IDLE state after  $t_{RP}$  has elapsed from the completion of precharge.

#### From IDLE state, command operation

To [DESL], [NOP], [PRE] or [PALL]: These commands result in no operation.

To [ACTV]: The bank specified by the address pins and the ROW address is activated.

**To [REF], [SELF]:** The SDRAM enters refresh mode (auto-refresh or self-refresh).

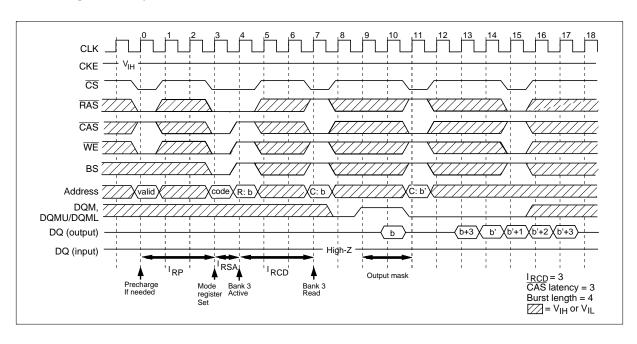

**To [MRS]:** The synchronous DRAM enters the mode register set cycle.

### From ROW ACTIVE state, command operation

**To [DESL], [NOP]:** These commands result in no operation.

**To [READ], [READ A]:** A read operation starts. (However, an interval of t<sub>RCD</sub> is required.)

**To [WRIT], [WRIT A]:** A write operation starts. (However, an interval of t<sub>RCD</sub> is required.)

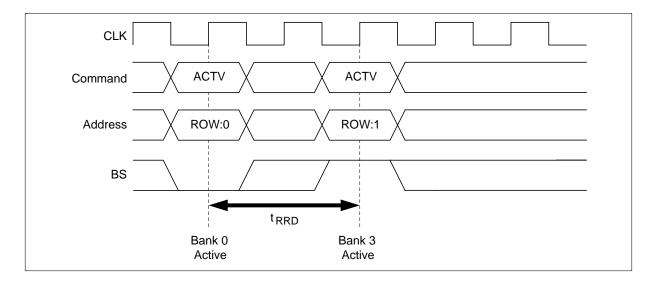

**To** [ACTV]: This command makes the other bank active. (However, an interval of  $t_{RRD}$  is required.) Attempting to make the currently active bank active results in an illegal command.

**To [PRE], [PALL]:** These commands set the SDRAM to precharge mode. (However, an interval of  $t_{RAS}$  is required.)

#### From READ state, command operation

To [DESL], [NOP]: These commands continue read operations until the burst operation is completed.

**To [READ], [READ A]:** Data output by the previous read command continues to be output. After  $\overline{CAS}$  latency, the data output resulting from the next command will start.

To [WRIT], [WRIT A]: These commands stop a burst read, and start a write cycle.

**To [ACTV]:** This command makes other banks bank active. (However, an interval of  $t_{RRD}$  is required.) Attempting to make the currently active bank active results in an illegal command.

To [PRE], [PALL]: These commands stop a burst read, and the SDRAM enters precharge mode.

### From READ with AUTO-PRECHARGE state, command operation

**To [DESL], [NOP]:** These commands continue read operations until the burst operation is completed, and the SDRAM then enters precharge mode.

**To [ACTV]:** This command makes other banks bank active. (However, an interval of  $t_{RRD}$  is required.) Attempting to make the currently active bank active results in an illegal command.

#### From WRITE state, command operation

To [DESL], [NOP]: These commands continue write operations until the burst operation is completed.

To [READ], [READ A]: These commands stop a burst and start a read cycle.

To [WRIT], [WRIT A]: These commands stop a burst and start the next write cycle.

**To** [ACTV]: This command makes the other bank active. (However, an interval of  $t_{RRD}$  is required.) Attempting to make the currently active bank active results in an illegal command.

To [PRE], [PALL]: These commands stop burst write and the SDRAM then enters precharge mode.

#### From WRITE with AUTO-PRECHARGE state, command operation

**To [DESL], [NOP]:** These commands continue write operations until the burst is completed, and the synchronous DRAM enters precharge mode.

**To** [ACTV]: This command makes the other bank active. (However, an interval of  $t_{RRD}$  is required.) Attempting to make the currently active bank active results in an illegal command.

#### From REFRESH state, command operation

**To [DESL], [NOP]:** After an auto-refresh cycle (after  $t_{RC}$ ), the SDRAM automatically enters the IDLE state.

# **Simplified State Diagram**

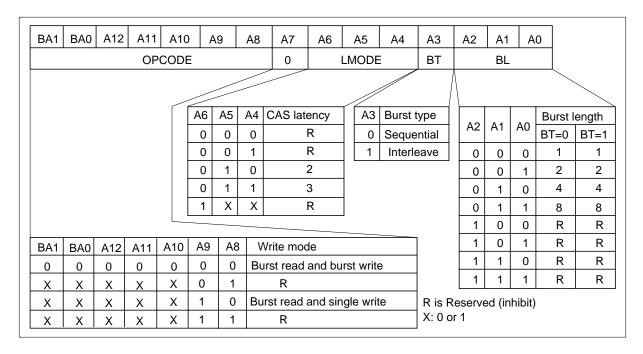

# **Mode Register Configuration**

The mode register is set by the input to the address pins (A0 to A12, BA0 and BA1) during mode register set cycles. The mode register consists of five sections, each of which is assigned to address pins.

**BA1, BA0, A11, A10, A12, A9, A8:** (OPCODE): The SDRAM has two types of write modes. One is the burst write mode, and the other is the single write mode. These bits specify write mode.

**Burst read and burst write:** Burst write is performed for the specified burst length starting from the column address specified in the write cycle.

**Burst read and single write:** Data is only written to the column address specified during the write cycle, regardless of the burst length.

A7: Keep this bit Low at the mode register set cycle. If this pin is high, the vender test mode is set.

**A6, A5, A4:** (LMODE): These pins specify the  $\overline{CAS}$  latency.

A3: (BT): A burst type is specified.

A2, A1, A0: (BL): These pins specify the burst length.

# **Burst Sequence**

Burst length = 2

| Starting Ad. | Addressing | (decimal)  |  |  |  |

|--------------|------------|------------|--|--|--|

| A0           | Sequential | Interleave |  |  |  |

| 0            | 0, 1,      | 0, 1,      |  |  |  |

| 1            | 1, 0,      | 1, 0,      |  |  |  |

Burst length = 4

| Startii | ng Ad. | Addressing(decimal)     |  |  |

|---------|--------|-------------------------|--|--|

| A1 A0   |        | Sequential Interleave   |  |  |

| 0       | 0      | 0, 1, 2, 3, 0, 1, 2, 3, |  |  |

| 0       | 1      | 1, 2, 3, 0, 1, 0, 3, 2, |  |  |

| 1       | 0      | 2, 3, 0, 1, 2, 3, 0, 1, |  |  |

| 1       | 1      | 3, 0, 1, 2, 3, 2, 1, 0, |  |  |

Burst length = 8

| Star | Starting Ad. |    | Addressing(decimal)     |                         |  |

|------|--------------|----|-------------------------|-------------------------|--|

| A2   | A1           | A0 | Sequential              | Interleave              |  |

| 0    | 0            | 0  | 0, 1, 2, 3, 4, 5, 6, 7, | 0, 1, 2, 3, 4, 5, 6, 7, |  |

| 0    | 0            | 1  | 1, 2, 3, 4, 5, 6, 7, 0, | 1, 0, 3, 2, 5, 4, 7, 6, |  |

| 0    | 1            | 0  | 2, 3, 4, 5, 6, 7, 0, 1, | 2, 3, 0, 1, 6, 7, 4, 5, |  |

| 0    | 1            | 1  | 3, 4, 5, 6, 7, 0, 1, 2, | 3, 2, 1, 0, 7, 6, 5, 4, |  |

| 1    | 0            | 0  | 4, 5, 6, 7, 0, 1, 2, 3, | 4, 5, 6, 7, 0, 1, 2, 3, |  |

| 1    | 0            | 1  | 5, 6, 7, 0, 1, 2, 3, 4, | 5, 4, 7, 6, 1, 0, 3, 2, |  |

| 1    | 1            | 0  | 6, 7, 0, 1, 2, 3, 4, 5, | 6, 7, 4, 5, 2, 3, 0, 1, |  |

| 1    | 1            | 1  | 7, 0, 1, 2, 3, 4, 5, 6, | 7, 6, 5, 4, 3, 2, 1, 0, |  |

### **Operation of the SDRAM**

The following chapter shows operation example of the products below.

| Organization                            | Input/output mask | CAS latency |

|-----------------------------------------|-------------------|-------------|

| 8-Mword $\times$ 16-bit $\times$ 4 bank | DQMU/DQML         | 2/3         |

| 16-Mword $\times$ 8-bit $\times$ 4 bank | DQM               |             |

| 32-Mword $\times$ 4-bit $\times$ 4 bank | DQM               |             |

Note: The SDRAM should be used according to the product capability (See "Features", "Pin Description" and "AC Characteristics").

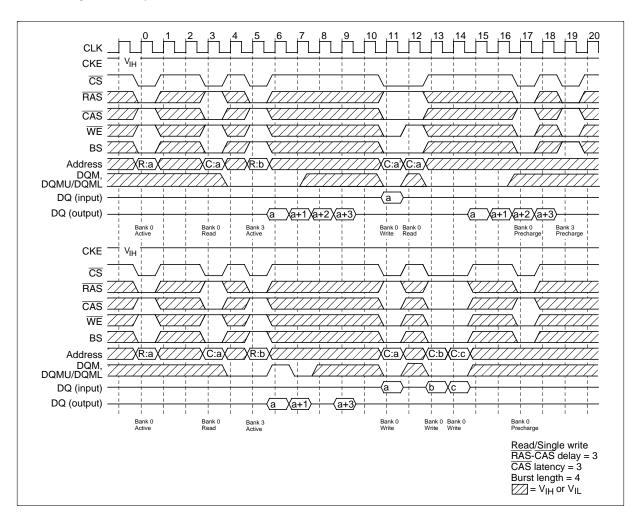

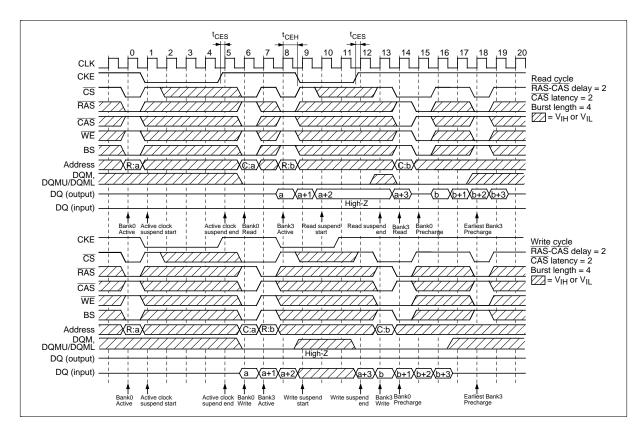

### **Read/Write Operations**

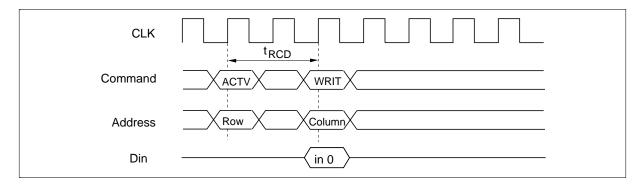

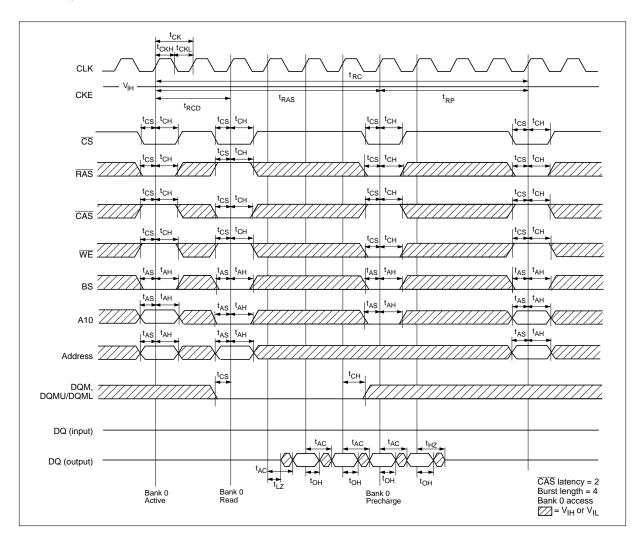

**Bank active:** Before executing a read or write operation, the corresponding bank and the row address must be activated by the bank active (ACTV) command. An interval of  $t_{RCD}$  is required between the bank active command input and the following read/write command input.

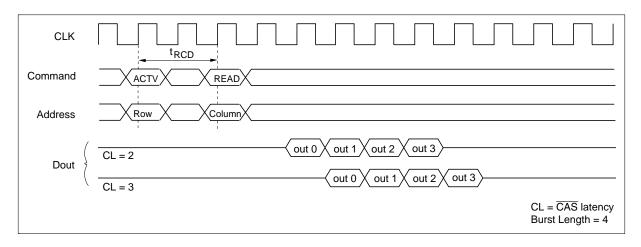

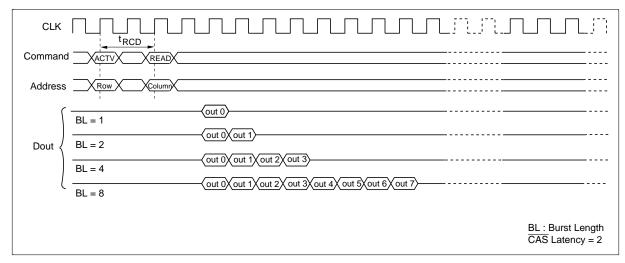

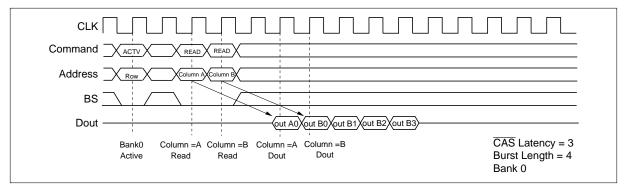

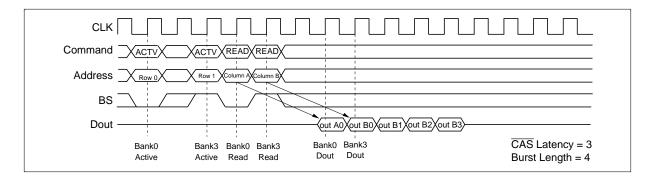

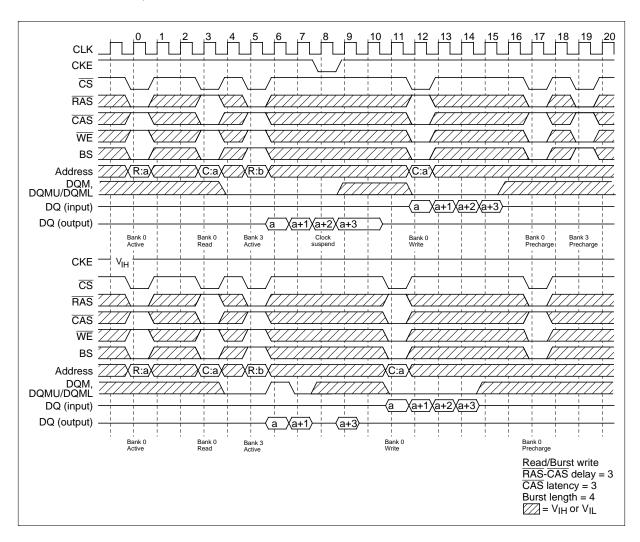

**Read operation:** A read operation starts when a read command is input. Output buffer becomes Low-Z in the (CAS Latency - 1) cycle after read command set. The SDRAM can perform a burst read operation.

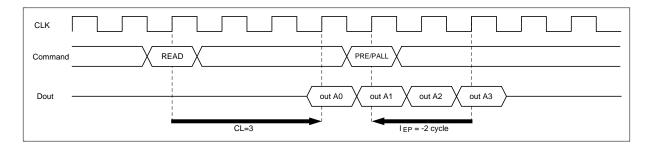

The burst length can be set to 1, 2, 4, 8. The start address for a burst read is specified by the column address and the bank select address (BA0/BA1) at the read command set cycle. In a read operation, data output starts after the number of clocks specified by the  $\overline{CAS}$  Latency. The  $\overline{CAS}$  Latency can be set to 2 or 3. When the burst length is 1, 2, 4, 8, the Dout buffer automatically becomes High-Z at the next clock after the successive burst-length data has been output. The  $\overline{CAS}$  latency and burst length must be specified at the mode register.

### **CAS** Latency

### **Burst Length**

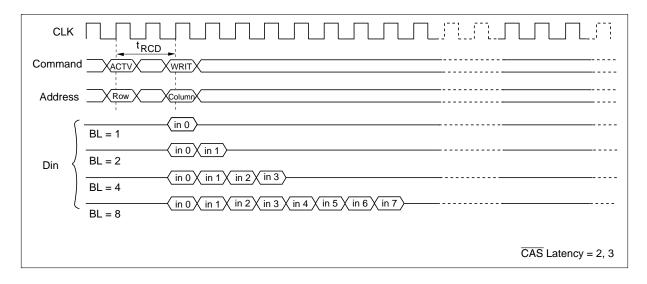

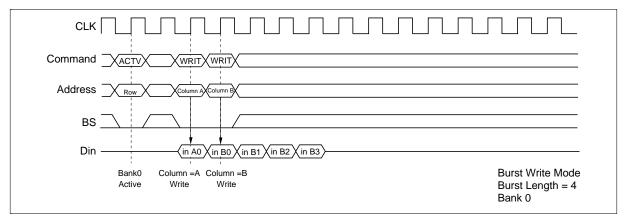

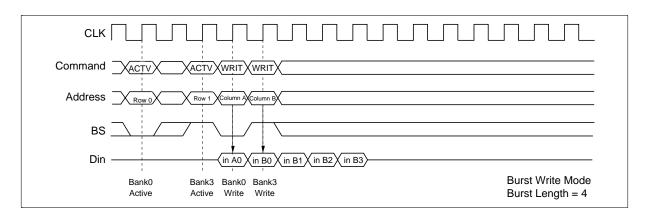

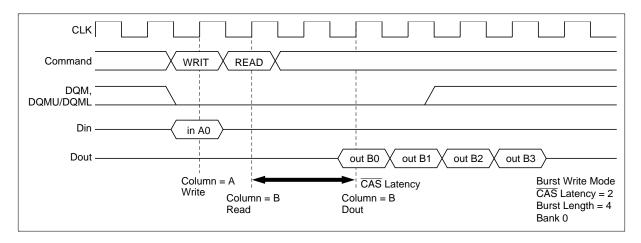

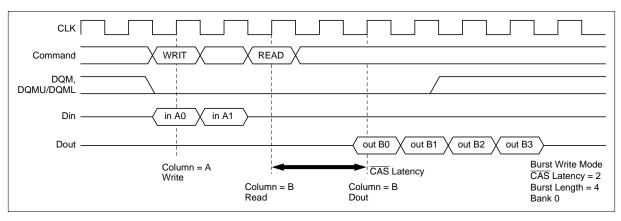

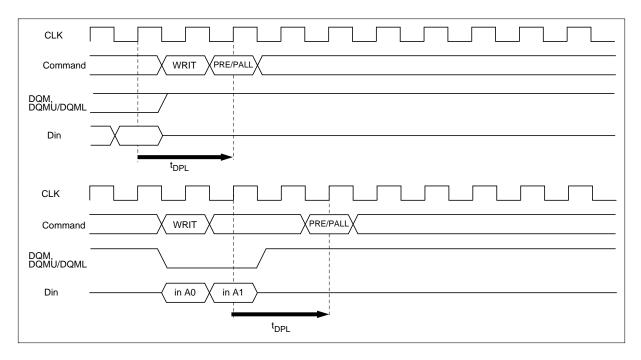

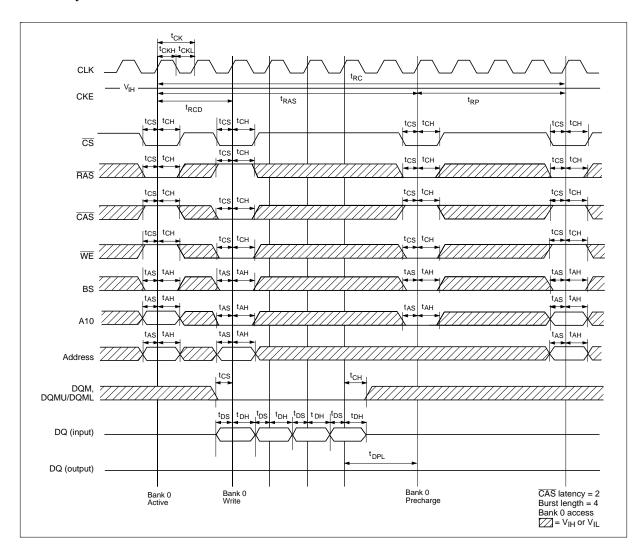

**Write operation:** Burst write or single write mode is selected by the OPCODE (BA1, BA0, A12, A11, A10, A9, A8) of the mode register.

**1. Burst write:** A burst write operation is enabled by setting OPCODE (A9, A8) to (0, 0). A burst write starts in the same clock as a write command set. (The latency of data input is 0 clock.) The burst length can be set to 1, 2, 4 and 8, like burst read operations. The write start address is specified by the column address and the bank select address (BA0/BA1) at the write command set cycle.

**2. Single write:** A single write operation is enabled by setting OPCODE (A9, A8) to (1, 0). In a single write operation, data is only written to the column address and the bank select address (BA0/BA1) specified by the write command set cycle without regard to the burst length setting. (The latency of data input is 0 clock).

### **Auto Precharge**

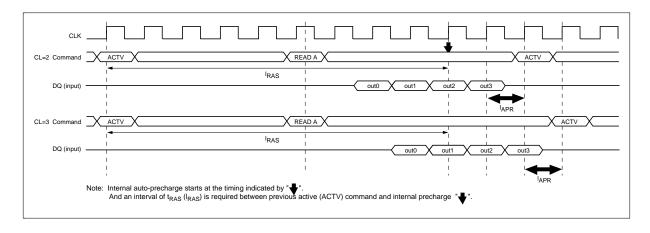

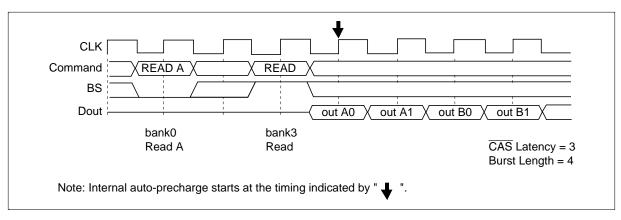

**Read with auto-precharge:** In this operation, since precharge is automatically performed after completing a read operation, a precharge command need not be executed after each read operation. The command executed for the same bank after the execution of this command must be the bank active (ACTV) command. In addition, an interval defined by  $l_{APR}$  is required before execution of the next command.

| CAS latency | Precharge start cycle                   |

|-------------|-----------------------------------------|

| 3           | 2 cycle before the final data is output |

| 2           | 1 cycle before the final data is output |

#### **Burst Read** (Burst Length = 4)

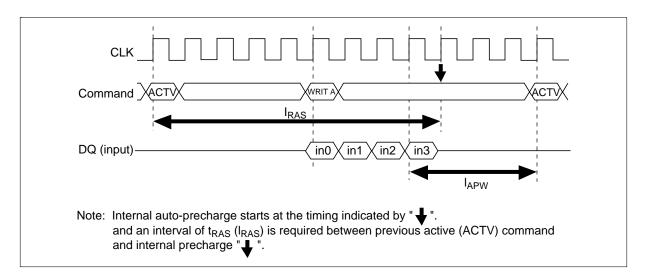

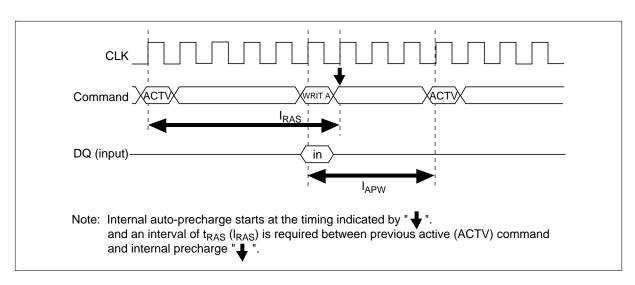

Write with auto-precharge: In this operation, since precharge is automatically performed after completing a burst write or single write operation, a precharge command need not be executed after each write operation. The command executed for the same bank after the execution of this command must be the bank active (ACTV) command. In addition, an interval of  $l_{APW}$  is required between the final valid data input and input of next command.

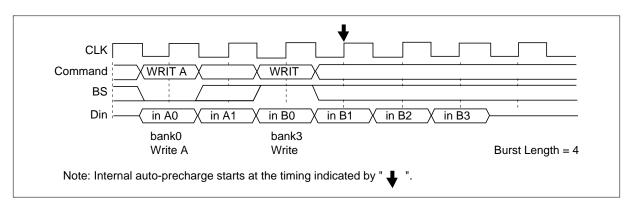

### **Burst Write (Burst Length = 4)**

### **Single Write**

#### **Command Intervals**

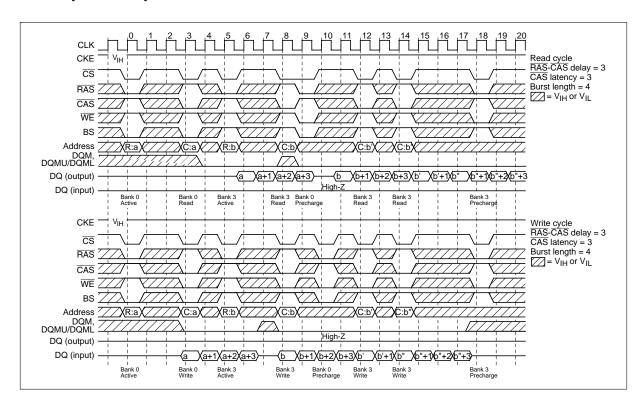

### Read command to Read command interval:

1. Same bank, same ROW address: When another read command is executed at the same ROW address of the same bank as the preceding read command execution, the second read can be performed after an interval of no less than 1 clock. Even when the first command is a burst read that is not yet finished, the data read by the second command will be valid.

**READ to READ Command Interval** (same ROW address in same bank)

- **2. Same bank, different ROW address:** When the ROW address changes on same bank, consecutive read commands cannot be executed; it is necessary to separate the two read commands with a precharge command and a bank-active command.

- **3. Different bank:** When the bank changes, the second read can be performed after an interval of no less than 1 clock, provided that the other bank is in the bank-active state. Even when the first command is a burst read that is not yet finished, the data read by the second command will be valid.

**READ to READ Command Interval** (different bank)

#### Write command to Write command interval:

**1. Same bank, same ROW address:** When another write command is executed at the same ROW address of the same bank as the preceding write command, the second write can be performed after an interval of no less than 1 clock. In the case of burst writes, the second write command has priority.

WRITE to WRITE Command Interval (same ROW address in same bank)

- **2. Same bank, different ROW address:** When the ROW address changes, consecutive write commands cannot be executed; it is necessary to separate the two write commands with a precharge command and a bank-active command.

- **3. Different bank:** When the bank changes, the second write can be performed after an interval of no less than 1 clock, provided that the other bank is in the bank-active state. In the case of burst write, the second write command has priority.

WRITE to WRITE Command Interval (different bank)

#### Read command to Write command interval:

1. Same bank, same ROW address: When the write command is executed at the same ROW address of the same bank as the preceding read command, the write command can be performed after an interval of no less than 1 clock. However, DQM, DQMU/DQML must be set High so that the output buffer becomes High-Z before data input.

#### **READ to WRITE Command Interval (1)**

### **READ to WRITE Command Interval (2)**

- 2. Same bank, different ROW address: When the ROW address changes, consecutive write commands cannot be executed; it is necessary to separate the two commands with a precharge command and a bank-active command.

- **3. Different bank:** When the bank changes, the write command can be performed after an interval of no less than 1 cycle, provided that the other bank is in the bank-active state. However, DQM, DQMU/DQML must be set High so that the output buffer becomes High-Z before data input.

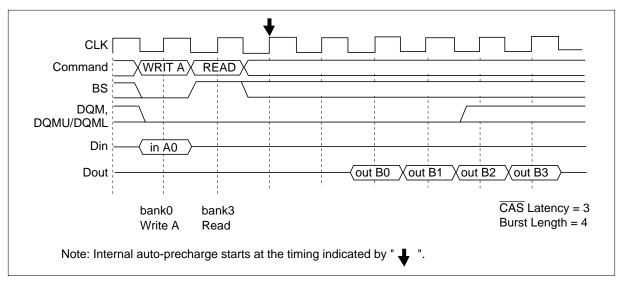

### Write command to Read command interval:

1. Same bank, same ROW address: When the read command is executed at the same ROW address of the same bank as the preceding write command, the read command can be performed after an interval of no less than 1 clock. However, in the case of a burst write, data will continue to be written until one clock before the read command is executed.

#### WRITE to READ Command Interval (1)

#### WRITE to READ Command Interval (2)

- **2. Same bank, different ROW address:** When the ROW address changes, consecutive read commands cannot be executed; it is necessary to separate the two commands with a precharge command and a bank-active command.

- **3. Different bank:** When the bank changes, the read command can be performed after an interval of no less than 1 clock, provided that the other bank is in the bank-active state. However, in the case of a burst write, data will continue to be written until one clock before the read command is executed (as in the case of the same bank and the same address).

### Read with auto precharge to Read command interval

1. Different bank: When some banks are in the active state, the second read command (another bank) is executed. Even when the first read with auto-precharge is a burst read that is not yet finished, the data read by the second command is valid. The internal auto-precharge of one bank starts at the next clock of the second command.

### Read with Auto Precharge to Read Command Interval (Different bank)

2. Same bank: The consecutive read command (the same bank) is illegal.

#### Write with auto precharge to Write command interval

1. Different bank: When some banks are in the active state, the second write command (another bank) is executed. In the case of burst writes, the second write command has priority. The internal auto-precharge of one bank starts at the next clock of the second command.

#### Write with Auto Precharge to Write Command Interval (Different bank)

**2. Same bank:** The consecutive write command (the same bank) is illegal.

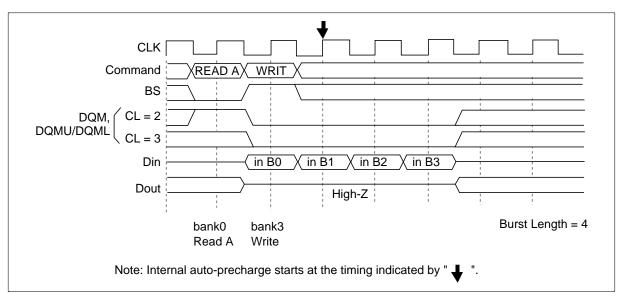

### Read with auto precharge to Write command interval

1. Different bank: When some banks are in the active state, the second write command (another bank) is executed. However, DQM, DQMU/DQML must be set High so that the output buffer becomes High-Z before data input. The internal auto-precharge of one bank starts at the next clock of the second command.

### Read with Auto Precharge to Write Command Interval (Different bank)

**2. Same bank:** The consecutive write command from read with auto precharge (the same bank) is illegal. It is necessary to separate the two commands with a bank active command.

### Write with auto precharge to Read command interval

1. Different bank: When some banks are in the active state, the second read command (another bank) is executed. However,in case of a burst write, data will continue to be written until one clock before the read command is executed. The internal auto-precharge of one bank starts at the next clock of the second command.

### Write with Auto Precharge to Read Command Interval (Different bank)

**2. Same bank:** The consecutive read command from write with auto precharge (the same bank) is illegal. It is necessary to separate the two commands with a bank active command.

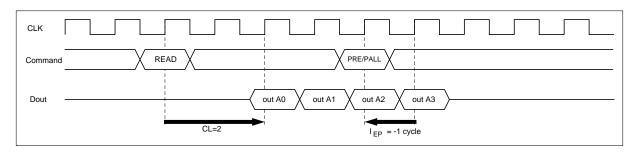

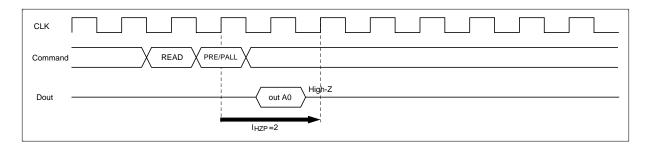

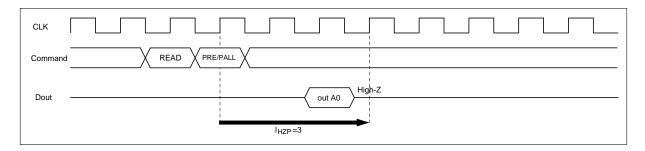

### Read command to Precharge command interval (same bank):

When the precharge command is executed for the same bank as the read command that preceded it, the minimum interval between the two commands is one clock. However, since the output buffer then becomes High-Z after the clocks defined by  $l_{HZP}$ , there is a case of interruption to burst read data output will be interrupted, if the precharge command is input during burst read. To read all data by burst read, the clocks defined by  $l_{EP}$  must be assured as an interval from the final data output to precharge command execution.

### READ to PRECHARGE Command Interval (same bank): To output all data

### $\overline{\text{CAS}}$ Latency = 2, Burst Length = 4

### $\overline{\text{CAS}}$ Latency = 3, Burst Length = 4

# READ to PRECHARGE Command Interval (same bank): To stop output data

# $\overline{\text{CAS}}$ Latency = 2, Burst Length = 1, 2, 4, 8

# $\overline{\text{CAS}}$ Latency = 3, Burst Length = 1, 2, 4, 8

Write command to Precharge command interval (same bank): When the precharge command is executed for the same bank as the write command that preceded it, the minimum interval between the two commands is 1 clock. However, if the burst write operation is unfinished, the input data must be masked by means of DQM, DQMU/DQML for assurance of the clock defined by t<sub>DPL</sub>.

### WRITE to PRECHARGE Command Interval (same bank)

**Burst Length = 4** (To stop write operation)

**Burst Length = 4** (To write all data)

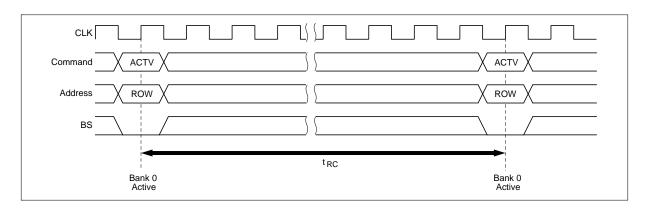

#### Bank active command interval:

- 1. Same bank: The interval between the two bank-active commands must be no less than t<sub>RC</sub>.

- 2. In the case of different bank-active commands: The interval between the two bank-active commands must be no less than  $t_{RRD}$ .

### **Bank Active to Bank Active for Same Bank**

### Bank Active to Bank Active for Different Bank

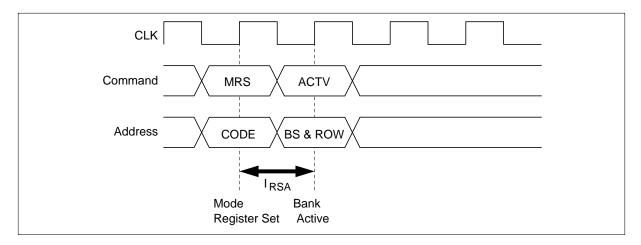

Mode register set to Bank-active command interval: The interval between setting the mode register and executing a bank-active command must be no less than  $l_{\text{RSA}}$ .

#### **DQM Control**

The DQM mask the DQ data. The DQMU and DQML mask the upper and lower bytes of the DQ data, respectively. The timing of DQMU/DQML is different during reading and writing.

**Reading:** When data is read, the output buffer can be controlled by DQM, DQMU/DQML. By setting DQM, DQMU/DQML to Low, the output buffer becomes Low-Z, enabling data output. By setting DQM, DQMU/DQML to High, the output buffer becomes High-Z, and the corresponding data is not output. However, internal reading operations continue. The latency of DQM, DQMU/DQML during reading is 2 clocks.

**Writing:** Input data can be masked by DQM, DQMU/DQML. By setting DQM, DQMU/DQML to Low, data can be written. In addition, when DQM, DQMU/DQML is set to High, the corresponding data is not written, and the previous data is held. The latency of DQM, DQMU/DQML during writing is 0 clock.

#### Reading

#### Writing

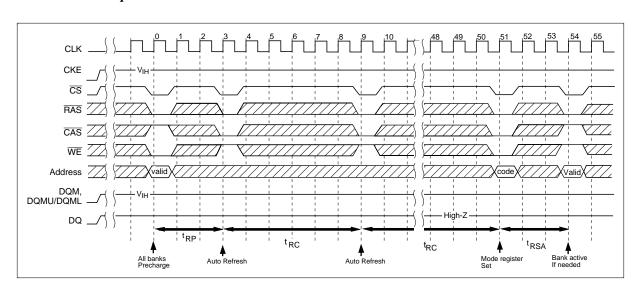

#### Refresh

**Auto-refresh:** All the banks must be precharged before executing an auto-refresh command. Since the auto-refresh command updates the internal counter every time it is executed and determines the banks and the ROW addresses to be refreshed, external address specification is not required. The refresh cycle is 8192 cycles/64 ms. (8192 cycles are required to refresh all the ROW addresses.) The output buffer becomes High-Z after auto-refresh start. In addition, since a precharge has been completed by an internal operation after the auto-refresh, an additional precharge operation by the precharge command is not required.

**Self-refresh:** After executing a self-refresh command, the self-refresh operation continues while CKE is held Low. During self-refresh operation, all ROW addresses are refreshed by the internal refresh timer. A self-refresh is terminated by a self-refresh exit command. Before and after self-refresh mode, execute auto-refresh to all refresh addresses in or within 64 ms period on the condition (1) and (2) below.

- (1) Enter self-refresh mode within 7.8 µs after either burst refresh or distributed refresh at equal interval to all refresh addresses are completed.

- (2) Start burst refresh or distributed refresh at equal interval to all refresh addresses within 7.8 µs after exiting from self-refresh mode.

#### **Others**

**Power-down mode:** The SDRAM enters power-down mode when CKE goes Low in the IDLE state. In power down mode, power consumption is suppressed by deactivating the input initial circuit. Power down mode continues while CKE is held Low. In addition, by setting CKE to High, the SDRAM exits from the power down mode, and command input is enabled from the next clock. In this mode, internal refresh is not performed.

**Clock suspend mode:** By driving CKE to Low during a bank-active or read/write operation, the SDRAM enters clock suspend mode. During clock suspend mode, external input signals are ignored and the internal state is maintained. When CKE is driven High, the SDRAM terminates clock suspend mode, and command input is enabled from the next clock. For details, refer to the "CKE Truth Table".

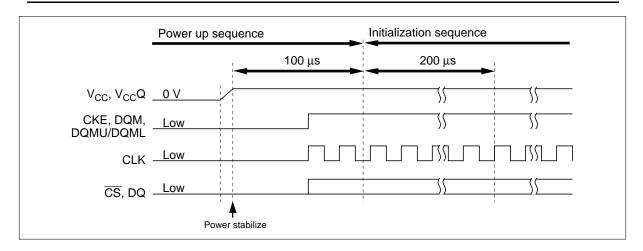

**Power-up sequence:** The SDRAM should be goes on the following sequence with power up.

The CLK, CKE,  $\overline{CS}$ , DQM, DQMU/DQML and DQ pins keep low till power stabilizes.

The CLK pin is stabilized within 100 µs after power stabilizes before the following initialization sequence. The CKE and DQM, DQMU/DQML is driven to high between power stabilizes and the initialization

The CKE and DQM, DQMU/DQML is driven to high between power stabilizes and the initialization sequence.

This SDRAM has  $V_{CC}$  clamp diodes for CLK, CKE,  $\overline{CS}$  DQM, DQMU/DQML and DQ pins. If these pins go high before power up, the large current flows from these pins to  $V_{CC}$  through the diodes.

**Initialization sequence:** When 200  $\mu$ s or more has past after the above power-up sequence, all banks must be precharged using the precharge command (PALL). After  $t_{RP}$  delay, set 8 or more auto refresh commands (REF). Set the mode register set command (MRS) to initialize the mode register. We recommend that by keeping DQM, DQMU/DQML and CKE to High, the output buffer becomes High-Z during Initialization sequence, to avoid DQ bus contention on memory system formed with a number of device.

#### **Absolute Maximum Ratings**

| Parameter                                  | Symbol          | Value                                               | Unit | Note |  |

|--------------------------------------------|-----------------|-----------------------------------------------------|------|------|--|

| Voltage on any pin relative to $V_{ss}$    | $V_{T}$         | $-0.5$ to V <sub>CC</sub> + 0.5 ( $\leq$ 4.6 (max)) | V    | 1    |  |

| Supply voltage relative to V <sub>SS</sub> | V <sub>cc</sub> | -0.5 to +4.6                                        | V    | 1    |  |

| Short circuit output current               | lout            | 50                                                  | mA   |      |  |

| Power dissipation                          | P <sub>T</sub>  | 1.2                                                 | W    |      |  |

| Operating temperature                      | Topr            | 0 to +60                                            | °C   |      |  |

| Storage temperature                        | Tstg            | -55 to +125                                         | °C   |      |  |

Note: 1. Respect to V<sub>ss</sub>.

### **DC Operating Conditions** (Ta = 0 to $+60^{\circ}$ C)

| Parameter          | Symbol                              | Min  | Max                   | Unit | Notes |

|--------------------|-------------------------------------|------|-----------------------|------|-------|

| Supply voltage     | $V_{cc}$ , $V_{cc}Q$                | 3.0  | 3.6                   | V    | 1, 2  |

|                    | V <sub>ss</sub> , V <sub>ss</sub> Q | 0    | 0                     | V    | 3     |

| Input high voltage | V <sub>IH</sub>                     | 2.0  | V <sub>cc</sub> + 0.3 | V    | 1, 4  |

| Input low voltage  | V <sub>IL</sub>                     | -0.3 | 0.8                   | V    | 1, 5  |

Notes: 1. All voltage referred to V<sub>ss</sub>.

- 2. The supply voltage with all  $V_{\text{CC}}$  and  $V_{\text{CC}}Q$  pins must be on the same level.

- 3. The supply voltage with all  $V_{\text{SS}}$  and  $V_{\text{SS}}Q$  pins must be on the same level.

- 4.  $V_{IH}$  (max) =  $V_{CC}$  + 2.0 V for pulse width  $\leq$  3 ns at  $V_{CC}$ .

- 5.  $V_{IL}$  (min) =  $V_{SS} 2.0$  V for pulse width  $\leq 3$  ns at  $V_{SS}$ .

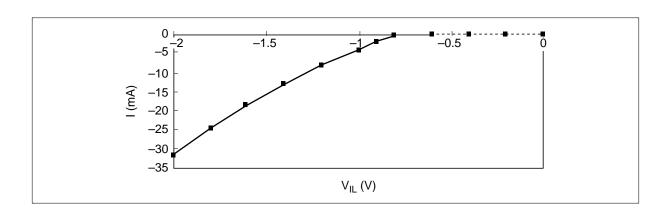

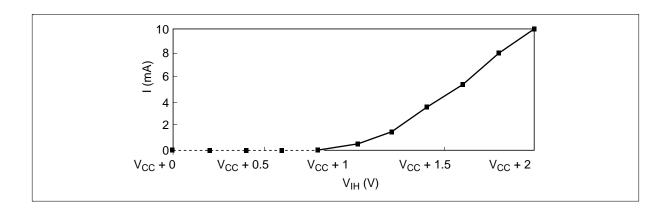

# $V_{\rm IL}/V_{\rm IH}$ Clamp

This SDRAM has  $V_{\rm IL}$  and  $V_{\rm IH}$  clamp for CLK, CKE, CS, DQM and DQ pins.

## $\label{eq:minimum} \textbf{Minimum} \ \textbf{V}_{\textbf{IL}} \ \textbf{Clamp} \ \textbf{Current}$

| V <sub>IL</sub> (V)                | I (mA) |

|------------------------------------|--------|

| -2<br>-1.8<br>-1.6<br>-1.4<br>-1.2 | -32    |

| -1.8                               | -25    |

| -1.6                               | -19    |

| -1.4                               | -13    |

| -1.2                               | -8     |

| -1                                 | -4     |

| -0.9                               | -2     |

| -0.8                               | -0.6   |

| -0.8<br>-0.6<br>-0.4<br>-0.2       | 0      |

| -0.4                               | 0      |

| -0.2                               | 0      |

| 0                                  | 0      |

# $\label{eq:minimum} \textbf{Minimum} \; \textbf{V}_{\textbf{IH}} \; \textbf{Clamp} \; \textbf{Current}$

| V <sub>IH</sub> (V)                                                     | I (mA) |

|-------------------------------------------------------------------------|--------|

| V <sub>cc</sub> + 2                                                     | 10     |

| V <sub>cc</sub> + 1.8                                                   | 8      |

| V <sub>cc</sub> + 1.6                                                   | 5.5    |

| V <sub>CC</sub> + 1.4                                                   | 3.5    |

| V <sub>cc</sub> + 1.2                                                   | 1.5    |

| V <sub>cc</sub> + 1                                                     | 0.3    |

| V <sub>CC</sub> + 0.8                                                   | 0      |

| V <sub>cc</sub> + 0.6                                                   | 0      |

| V <sub>CC</sub> + 0.4                                                   | 0      |

| $\frac{V_{cc} + 0.6}{V_{cc} + 0.4}$ $\frac{V_{cc} + 0.2}{V_{cc} + 0.2}$ | 0      |

| V <sub>cc</sub> + 0                                                     | 0      |

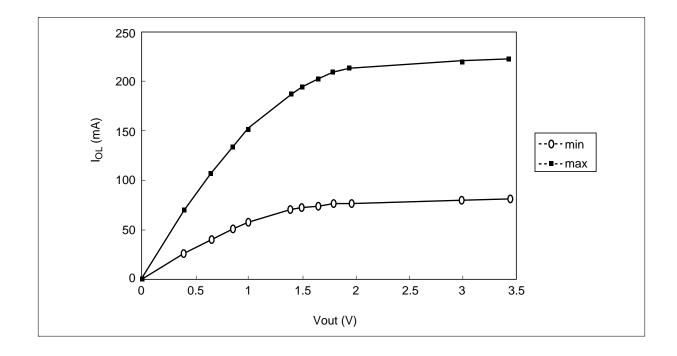

# $I_{\rm OL}/I_{\rm OH}$ Characteristics

## Output Low Current $(I_{OL})$

|          | I <sub>OL</sub> | I <sub>oL</sub> |

|----------|-----------------|-----------------|

| Vout (V) | Min (mA)        | Max (mA)        |

| 0        | 0               | 0               |

| 0.4      | 27              | 71              |

| 0.65     | 41              | 108             |

| 0.85     | 51              | 134             |

| 1        | 58              | 151             |

| 1.4      | 70              | 188             |

| 1.5      | 72              | 194             |

| 1.65     | 75              | 203             |

| 1.8      | 77              | 209             |

| 1.95     | 77              | 212             |

| 3        | 80              | 220             |

| 3.45     | 81              | 223             |

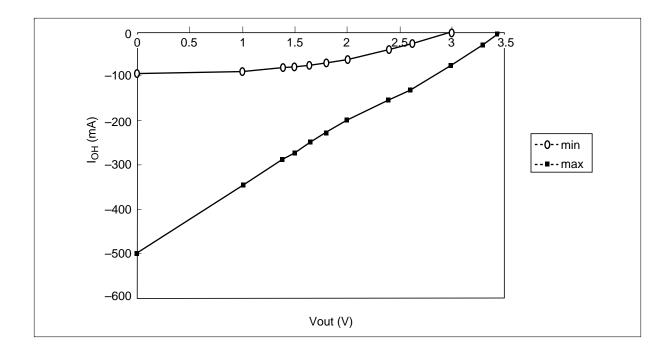

Output High Current ( $I_{OH}$ ) (Ta = 0 to +60°C,  $V_{CC}$ ,  $V_{CC}$ Q = 3.0 V to 3.45 V,  $V_{SS}$ ,  $V_{SS}$ Q = 0 V)

|          | I <sub>OH</sub> | I <sub>он</sub> |          |  |  |

|----------|-----------------|-----------------|----------|--|--|

| Vout (V) | Min (mA)        | Max (mA)        | Max (mA) |  |  |

| 3.45     | <del>-</del>    | -3              |          |  |  |

| 3.3      | <del>-</del>    | -28             |          |  |  |

| 3        | 0               | -75             |          |  |  |

| 2.6      | -21             | -130            |          |  |  |

| 2.4      | -34             | -154            |          |  |  |

| 2        | -59             | -197            |          |  |  |

| 1.8      | -67             | -227            |          |  |  |

| 1.65     | -73             | -248            |          |  |  |

| 1.5      | -78             | -270            |          |  |  |

| 1.4      | -81             | -285            |          |  |  |

| 1        | -89             | -345            |          |  |  |

| 0        | -93             | -503            |          |  |  |

**DC Characteristics** (Ta = 0 to +60°C,  $V_{CC}$ ,  $V_{CC}Q = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{SS}$ ,  $V_{SS}Q = 0 \text{ V}$ ) (HM5257165B)

#### HM5257165B

|                                                                |                    | -75  |     | -A6  |     | _         |                                                                                             |         |

|----------------------------------------------------------------|--------------------|------|-----|------|-----|-----------|---------------------------------------------------------------------------------------------|---------|

| Parameter                                                      | Symbol             | Min  | Max | Min  | Max | _<br>Unit | Test conditions                                                                             | Notes   |

| Operating current (CAS latency = 2)                            | I <sub>CC1</sub>   | _    | 220 | _    | 190 | mA        | Burst length = 1<br>t <sub>RC</sub> = min                                                   | 1, 2, 3 |

| $(\overline{CAS}   \text{latency} = 3)$                        | I <sub>CC1</sub>   | _    | 220 | _    | 190 | mA        | _                                                                                           |         |

| Standby current in power down                                  | I <sub>CC2P</sub>  | _    | 6   | _    | 6   | mA        | $CKE = V_{IL},$<br>$t_{CK} = 12 \text{ ns}$                                                 | 6       |

| Standby current in power down (input signal stable)            | I <sub>CC2PS</sub> | _    | 4   | _    | 4   | mA        | $CKE = V_{IL},t_{CK} = \infty$                                                              | 7       |

| Standby current in non power down                              | I <sub>CC2N</sub>  |      | 40  | _    | 40  | mA        | CKE, $\overline{CS} = V_{IH}$ , $t_{CK} = 12 \text{ ns}$                                    | 4       |

| Standby current in non power down (input signal stable)        | I <sub>CC2NS</sub> |      | 18  | _    | 18  | mA        | $CKE = V_{IH}, t_{CK} = \infty$                                                             | 9       |

| Active standby current in power down                           | I <sub>CC3P</sub>  | _    | 8   | _    | 8   | mA        | $CKE = V_{IL},$<br>$t_{CK} = 12 \text{ ns}$                                                 | 1, 2, 6 |

| Active standby current in power down (input signal stable)     | I <sub>CC3PS</sub> | _    | 6   |      | 6   | mA        | $CKE = V_{IL},t_{CK} = \infty$                                                              | 2, 7    |

| Active standby current in non power down                       | I <sub>CC3N</sub>  | _    | 60  | _    | 60  | mA        | CKE, $\overline{\text{CS}} = \text{V}_{\text{IH}}$ , $\text{t}_{\text{CK}} = 12 \text{ ns}$ | 1, 2, 4 |

| Active standby current in non power down (input signal stable) | I <sub>CC3NS</sub> | _    | 30  | _    | 30  | mA        | $CKE = V_{IH},t_{CK} = \infty$                                                              | 2, 9    |

| Burst operating current (CAS latency = 2)                      | I <sub>CC4</sub>   | _    | 200 | _    | 200 | mA        | t <sub>CK</sub> = min, BL = 4                                                               | 1, 2, 5 |

| $(\overline{CAS}   \text{latency} = 3)$                        | I <sub>CC4</sub>   | _    | 270 | _    | 200 | mA        | _                                                                                           |         |

| Refresh current                                                | I <sub>CC5</sub>   | _    | 330 | _    | 330 | mA        | t <sub>RC</sub> = min                                                                       | 3       |

| Self refresh current                                           | I <sub>CC6</sub>   | _    | 6   | _    | 6   | mA        | $V_{IH} \ge V_{CC} - 0.2 \text{ V}$ $V_{IL} \le 0.2 \text{ V}$                              | 8       |

| Input leakage current                                          | I <sub>LI</sub>    | -1   | 1   | -1   | 1   | μA        | $0 \le Vin \le V_{CC}$                                                                      |         |

| Output leakage current                                         | I <sub>LO</sub>    | -1.5 | 1.5 | -1.5 | 1.5 | μA        | $0 \le Vout \le V_{CC}$<br>DQ = disable                                                     |         |

| Output high voltage                                            | V <sub>OH</sub>    | 2.4  | _   | 2.4  | _   | V         | $I_{OH} = -4 \text{ mA}$                                                                    |         |

| Output low voltage                                             | V <sub>OL</sub>    | _    | 0.4 | _    | 0.4 | V         | I <sub>OL</sub> = 4 mA                                                                      |         |

**DC Characteristics** (Ta = 0 to +60°C,  $V_{CC}$ ,  $V_{CC}Q = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{SS}$ ,  $V_{SS}Q = 0 \text{ V}$ ) (HM5257805B)

|                                                                |                    | HM525 | 7805B |      |     |           |                                                                                      |         |

|----------------------------------------------------------------|--------------------|-------|-------|------|-----|-----------|--------------------------------------------------------------------------------------|---------|

|                                                                |                    | -75   |       | -A6  |     | _         |                                                                                      |         |

| Parameter                                                      | Symbol             | Min   | Max   | Min  | Max | _<br>Unit | Test conditions                                                                      | Notes   |

| Operating current (CAS latency = 2)                            | I <sub>CC1</sub>   | _     | 220   | _    | 190 | mA        | Burst length = 1<br>t <sub>RC</sub> = min                                            | 1, 2, 3 |

| $(\overline{CAS}   \text{latency} = 3)$                        | I <sub>CC1</sub>   | _     | 220   | _    | 190 | mA        |                                                                                      |         |

| Standby current in power down                                  | I <sub>CC2P</sub>  | _     | 6     |      | 6   | mA        | $CKE = V_{IL},$ $t_{CK} = 12 \text{ ns}$                                             | 6       |

| Standby current in power down (input signal stable)            | I <sub>CC2PS</sub> | _     | 4     |      | 4   | mA        | $CKE = V_{IL},t_{CK} = \infty$                                                       | 7       |

| Standby current in non power down                              | I <sub>CC2N</sub>  | _     | 40    |      | 40  | mA        | CKE, $\overline{CS} = V_{IH}$ , $t_{CK} = 12 \text{ ns}$                             | 4       |

| Standby current in non power down (input signal stable)        | I <sub>CC2NS</sub> | _     | 18    |      | 18  | mA        | $CKE = V_{IH},t_{CK} = \infty$                                                       | 9       |

| Active standby current in power down                           | I <sub>CC3P</sub>  | _     | 8     |      | 8   | mA        | $CKE = V_{IL},$<br>$t_{CK} = 12 \text{ ns}$                                          | 1, 2, 6 |

| Active standby current in power down (input signal stable)     | I <sub>CC3PS</sub> | _     | 6     | _    | 6   | mA        | $CKE = V_{IL},t_{CK} = \infty$                                                       | 2, 7    |

| Active standby current in non power down                       | I <sub>CC3N</sub>  | _     | 60    |      | 60  | mA        | CKE, $\overline{\text{CS}} = \text{V}_{\text{IH}}$ , $t_{\text{CK}} = 12 \text{ ns}$ | 1, 2, 4 |

| Active standby current in non power down (input signal stable) | I <sub>CC3NS</sub> | _     | 30    | _    | 30  | mA        | $CKE = V_{IH},t_{CK} = \infty$                                                       | 2, 9    |

| Burst operating current (CAS latency = 2)                      | I <sub>CC4</sub>   | _     | 190   | _    | 190 | mA        | $t_{CK} = min, BL = 4$                                                               | 1, 2, 5 |

| $(\overline{CAS}   \text{latency} = 3)$                        | I <sub>CC4</sub>   | _     | 260   | _    | 190 | mA        | _                                                                                    |         |

| Refresh current                                                | I <sub>CC5</sub>   | _     | 330   | _    | 330 | mA        | t <sub>RC</sub> = min                                                                | 3       |

| Self refresh current                                           | I <sub>CC6</sub>   | _     | 6     |      | 6   | mA        | $V_{IH} \ge V_{CC} - 0.2 \text{ V}$ $V_{IL} \le 0.2 \text{ V}$                       | 8       |

| Input leakage current                                          | I <sub>LI</sub>    | -1    | 1     | -1   | 1   | μΑ        | $0 \le Vin \le V_{CC}$                                                               | ,,      |

| Output leakage current                                         | I <sub>LO</sub>    | -1.5  | 1.5   | -1.5 | 1.5 | μΑ        | $0 \le Vout \le V_{CC}$<br>DQ = disable                                              |         |

| Output high voltage                                            | V <sub>OH</sub>    | 2.4   | _     | 2.4  | _   | V         | I <sub>OH</sub> = -4 mA                                                              |         |

0.4

0.4

$I_{OL} = 4 \text{ mA}$

Output low voltage

$\rm V_{\rm OL}$

**DC Characteristics** (Ta = 0 to +60°C,  $V_{CC}$ ,  $V_{CC}Q = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{SS}$ ,  $V_{SS}Q = 0 \text{ V}$ ) (HM5257405B)

| HM5257405B |  |

|------------|--|

|            |  |

|                                                                |                    | -75  |     | -A6  |     |          |                                                                                             |         |  |

|----------------------------------------------------------------|--------------------|------|-----|------|-----|----------|---------------------------------------------------------------------------------------------|---------|--|

| Parameter                                                      | Symbol             | Min  | Max | Min  | Max | <br>Unit | Test conditions                                                                             | Notes   |  |

| Operating current (CAS latency = 2)                            | I <sub>CC1</sub>   | _    | 220 | _    | 190 | mA       | Burst length = 1<br>t <sub>RC</sub> = min                                                   | 1, 2, 3 |  |

| $(\overline{CAS}   \text{latency} = 3)$                        | I <sub>CC1</sub>   | _    | 220 | _    | 190 | mA       | _                                                                                           |         |  |

| Standby current in power down                                  | I <sub>CC2P</sub>  |      | 6   | _    | 6   | mA       | $CKE = V_{IL},$<br>$t_{CK} = 12 \text{ ns}$                                                 | 6       |  |

| Standby current in power down (input signal stable)            | I <sub>CC2PS</sub> | _    | 4   | _    | 4   | mA       | $CKE = V_{IL},t_{CK} = \infty$                                                              | 7       |  |

| Standby current in non power down                              | I <sub>CC2N</sub>  | _    | 40  | _    | 40  | mA       | CKE, $\overline{\text{CS}} = \text{V}_{\text{IH}}$ , $t_{\text{CK}} = 12 \text{ ns}$        | 4       |  |

| Standby current in non power down (input signal stable)        | I <sub>CC2NS</sub> | _    | 18  | _    | 18  | mA       | $CKE = V_{IH},t_{CK} = \infty$                                                              | 9       |  |

| Active standby current in power down                           | I <sub>CC3P</sub>  | _    | 8   | _    | 8   | mA       | $CKE = V_{IL},$<br>$t_{CK} = 12 \text{ ns}$                                                 | 1, 2, 6 |  |

| Active standby current in power down (input signal stable)     | I <sub>CC3PS</sub> | _    | 6   |      | 6   | mA       | $CKE = V_{IL},t_{CK} = \infty$                                                              | 2, 7    |  |

| Active standby current in non power down                       | I <sub>CC3N</sub>  | _    | 60  | _    | 60  | mA       | CKE, $\overline{\text{CS}} = \text{V}_{\text{IH}}$ , $\text{t}_{\text{CK}} = 12 \text{ ns}$ | 1, 2, 4 |  |

| Active standby current in non power down (input signal stable) | I <sub>CC3NS</sub> |      | 30  |      | 30  | mA       | $CKE = V_{IH},t_{CK} = \infty$                                                              | 2, 9    |  |

| Burst operating current (CAS latency = 2)                      | I <sub>CC4</sub>   | _    | 190 | _    | 190 | mA       | t <sub>CK</sub> = min, BL = 4                                                               | 1, 2, 5 |  |

| $(\overline{CAS}   \text{latency} = 3)$                        | I <sub>CC4</sub>   | _    | 260 | _    | 190 | mA       | _                                                                                           |         |  |

| Refresh current                                                | I <sub>CC5</sub>   | _    | 330 | _    | 330 | mA       | $t_{RC} = min$                                                                              | 3       |  |

| Self refresh current                                           | I <sub>CC6</sub>   | _    | 6   | _    | 6   | mA       | $V_{IH} \ge V_{CC} - 0.2 \text{ V}$ $V_{IL} \le 0.2 \text{ V}$                              | 8       |  |

| Input leakage current                                          | Iu                 | -1   | 1   | -1   | 1   | μA       | $0 \le Vin \le V_{CC}$                                                                      |         |  |

| Output leakage current                                         | I <sub>LO</sub>    | -1.5 | 1.5 | -1.5 | 1.5 | μA       | $0 \le Vout \le V_{CC}$<br>DQ = disable                                                     |         |  |

| Output high voltage                                            | V <sub>OH</sub>    | 2.4  |     | 2.4  | _   | V        | $I_{OH} = -4 \text{ mA}$                                                                    |         |  |

| Output low voltage                                             | V <sub>OL</sub>    | _    | 0.4 | _    | 0.4 | V        | I <sub>OL</sub> = 4 mA                                                                      |         |  |

Notes: 1.  $I_{cc}$  depends on output load condition when the device is selected.  $I_{cc}$  (max) is specified at the output open condition.

- 2. One bank operation.

- 3. Input signals are changed once per one clock.

- 4. Input signals are changed once per two clocks.

- 5. Input signals are changed once per four clocks.

- 6. After power down mode, CLK operating current.

- 7. After power down mode, no CLK operating current.

- 8. After self refresh mode set, self refresh current.

- 9. Input signals are  $V_{IH}$  or  $V_{IL}$  fixed.

## Capacitance (Ta = 25°C, $V_{CC}$ , $V_{CC}$ Q = 3.3 V $\pm$ 0.3 V)

| Parameter                 | Symbol          | Min | Max | Unit | Notes      |

|---------------------------|-----------------|-----|-----|------|------------|

| Input capacitance (CLK)   | C <sub>I1</sub> | 2.5 | 7   | pF   | 1, 2, 4    |

| Input capacitance (Input) | C <sub>12</sub> | 2.5 | 7   | pF   | 1, 2, 4    |

| Output capacitance (DQ)   | C <sub>o</sub>  | 4   | 8   | pF   | 1, 2, 3, 4 |

Notes: 1. Capacitance measured with Boonton Meter or effective capacitance measuring method.

- 2. Measurement condition: f = 1 MHz, 1.4 V bias, 200 mV swing.

- 3. DQM, DQMU/DQML =  $V_{IH}$  to disable Dout.

- 4. This parameter is sampled and not 100% tested.

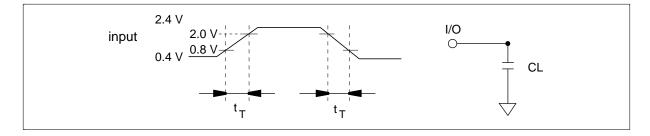

AC Characteristics (Ta = 0 to +60°C,  $V_{CC}$ ,  $V_{CC}$ ,  $V_{CC}Q$  = 3.3 V  $\pm$  0.3 V,  $V_{SS}$ ,  $V_{SS}Q$  = 0 V)

HM5257165B/ HM5257805B/ HM5257405B

|                                                     |                                   |                  |      |        |     |        | _    |         |  |

|-----------------------------------------------------|-----------------------------------|------------------|------|--------|-----|--------|------|---------|--|

|                                                     |                                   |                  | -75  |        | -A6 |        | _    |         |  |

| Parameter                                           | Symbol                            | PC/100<br>Symbol | Min  | Max    | Min | Max    | Unit | Notes   |  |

| System clock cycle time (CAS latency = 2)           | t <sub>ck</sub>                   | Tclk             | 10   | _      | 10  | _      | ns   | 1       |  |

| $(\overline{CAS}   \text{latency} = 3)$             | t <sub>CK</sub>                   | Tclk             | 7.5  |        | 10  |        | ns   |         |  |

| CLK high pulse width                                | t <sub>CKH</sub>                  | Tch              | 2.5  |        | 3   |        | ns   | 1       |  |

| CLK low pulse width                                 | t <sub>CKL</sub>                  | Tcl              | 2.5  | _      | 3   | _      | ns   | 1       |  |