# Z86250 STARSIGHTDATABASEENGINE

### **FEATURES**

■ Part Package Speed (MHz)

Z86250 84-Pin PLCC 24

- 4.3- to 5.5-Volt Operating Range

- 0°C to +70°C Temperature Range

- Low-Power Consumption

- Segmented Base Registers

- Infrared Receiver Logic

- CRC-32 Encoding and Decoding Logic

- Watch-Dog Timer (WDT) for Error Recovery

- Serial I.M. and I<sup>2</sup>C Compatible Bus for External Communication

- Test Multiplexer for Chip Debug

## GENERAL DESCRIPTION

Zilog's Z86250 StarSight Data Base Engine (DBE) is designed to process extracted data for the StarSight on-screen programming guide. The device is logically equivalent to the DBE1200 for StarSight applications.

The Z86250 provides a number of important peripheral functions, such as the IR Blaster to send command signals to the VCR, and low-power management to avoid loss of data.

For fast memory data manipulation, the Z86250 offers segmented base registers. The device also features PSRAM memory control and refresh logic.

The DBE is optimized to work with Zilog's Z89300 series of TV controller devices to provide a cost-effective solution for StarSight programming-guide data extraction and display.

### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection      | Circuit                | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power<br>Ground | V <sub>cc</sub><br>GND | $egin{array}{c} egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}$ |

CP96TEL0302 (2/96) 1

# **GENERAL DESCRIPTION** (Continued)

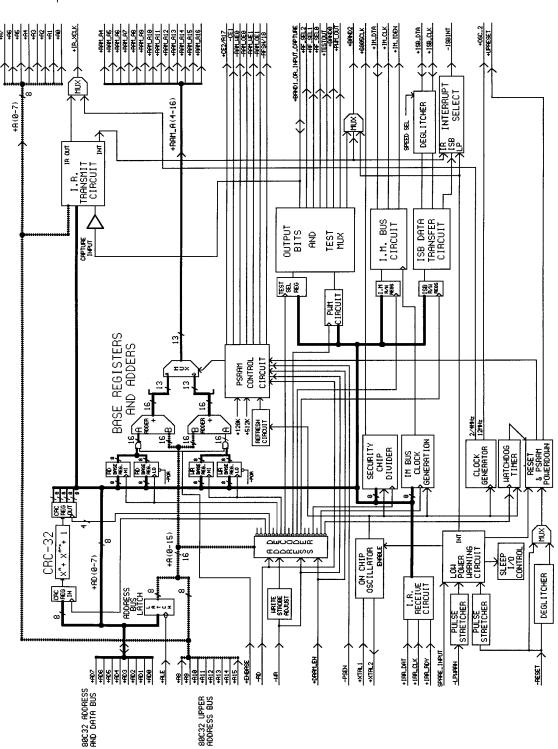

**Database Engine Block Diagram**

## PIN DESCRIPTION

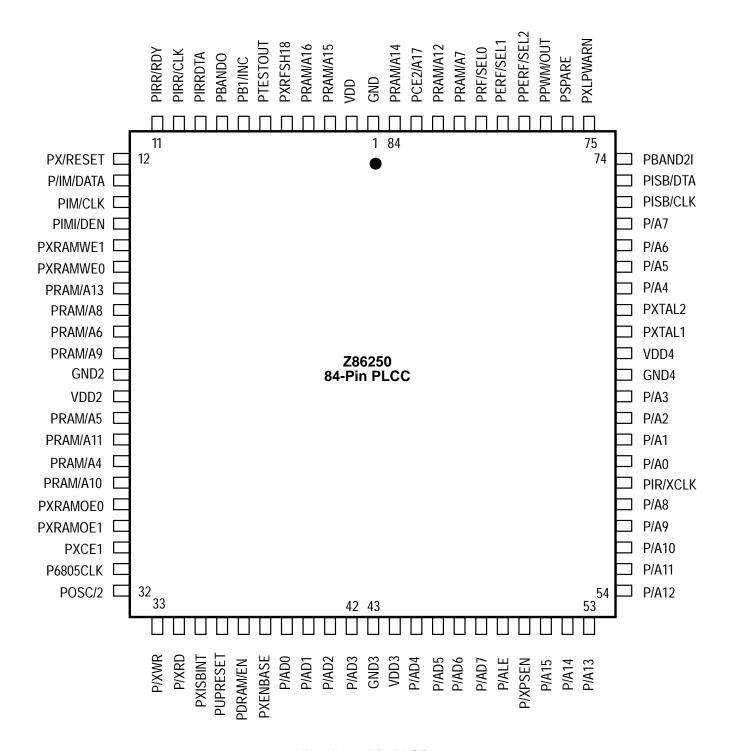

Z86250 84-Pin PLCC Pin Assignments

# PIN DESCRIPTION (Continued)

| PIN | PIN       | PIN           |

|-----|-----------|---------------|

| NO. | NAME      | ТҮРЕ          |

|     |           |               |

|     | GND1      | POWER         |

| 2   | VDD1      | POWER         |

| 3   | PRAM A15  | Out LIVE      |

| 4   | PRAM A16  | Out LIVE      |

| 5   | PXRFSH18  | Oon           |

| 6   | PTESTOUT  | Out DEAD      |

| 7   | PB1 IN C  | I/O pushpull  |

| 8   | PBAND0    | Out DEAD,hc   |

| 9   | PIRR DTA  | IN SO         |

| 10  | PIRR CLK  | IN SO         |

| 11  | PIRR RDY  | IN SO         |

| 12  | P XRESET  | IN on always  |

| 13  | P IM DTA  | I/O opendrain |

| 14  | PIM CLK   | Out DEAD      |

| 15  | PIM IDEN  | Out DEAD      |

| 16  | PXRAMWE1  | Out LIVE      |

| 17  | PXRAMWE0_ | Out LIVE      |

| 18  | PRAM A13  | Out LIVE      |

| 19  | PRAM_A8   | Out LIVE      |

| 20  | PRAM A6   | Out LIVE      |

| 21  | PRAM A9   | Out LIVE      |

| 22  | GND2      | POWER         |

| 23  | VDD2      | POWER         |

| 24  | PRAM A5   | Out LIVE      |

| 25  | PRAM A11  | Out LIVE      |

| 26  | PRAM_A4   | Out LIVE      |

| 27  | PRAM A10_ | Out LIVE      |

| 28  | PXRAMOE0  | Oon           |

| 29  | PXRAMOE1  | Out LIVE      |

| 30  | PXCE1     | Oon           |

| 31  | P6805CLK  | Out DEAD      |

| 32  | POSC 2    | Out OSC2      |

| 33  | P XWR     | IN S1         |

| 34  | P XRD     | IN S1         |

| 35  | PXISBINT  | Out INT       |

| 36  | PUPRESET  | Out DEAD      |

| 37  | PDRAM EN  | IN S0         |

| 38  | PXENBASE  | IN S0         |

| 39  | P AD0     | I/O data      |

| 40  | P AD1     | I/O data      |

| 41  | P AD2     | I/O data      |

| 42  | P AD3     | I/O data      |

|     |           |               |

| PIN | PIN      | PIN           |

|-----|----------|---------------|

| NO. | NAME     | TYPE          |

| 43  | GND3     | POWER         |

| 44  | VDD3     | POWER         |

| 45  | P AD4    | I/O data      |

| 46  | P AD5    | I/O data      |

| 47  | P AD6    | I/O data      |

| 48  | P AD7    | I/O data      |

| 49  | P ALE    | IN SO         |

| 50  | P XPSEN  | IN S1         |

| 51  | P A15    | IN SO         |

| 52  | P A14    | IN SO         |

| 53  | P A13    | IN S0         |

| 54  | P A12    | IN SO         |

| 55  | P A11    | IN SO         |

| 56  | P A10    | IN S0         |

| 57  | P A9     | IN SO         |

| 58  | P A8     | IN SO         |

| 59  | PIR XCLK | Out DEAD,hc   |

| 60  | P A0     | Out DEAD      |

| 61  | P A1     | Out DEAD      |

| 62  | P A2     | Out DEAD      |

| 63  | P A3     | Out DEAD      |

| 64  | GND4     | POWER         |

| 65  | VDD4     | POWER         |

| 66  | PXTAL1   | OSC INPUT     |

| 67  | PXTAL2   | OSC OUT       |

| 68  | P A4     | Out DEAD      |

| 69  | P A5     | Out DEAD      |

| 70  | P A6     | Out DEAD      |

| 71  | P A7     | Out DEAD      |

| 72  | PISB CLK | I/O opendrain |

| 73  | PISB DTA | I/O opendrain |

| 74  | PBAND2I  | Out INT       |

| 75  | PXLPWARN | INon          |

| 76  | PSPARE_  | INon          |

| 77  | PPWM OUT | Out DEAD_     |

| 78  | PRF SEL2 | Out DEAD      |

| 79  | PRF SEL1 | Out DEAD      |

| 80  | PRF SEL0 | Out DEAD      |

| 81  | PRAM_A7  | Out LIVE      |

| 82  | PRAM A12 | Out LIVE      |

| 83  | PCE2 A17 | Oon           |

| 84  | PRAM A14 | Out LIVE      |

**Z86250 Pinouts**

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol       | Parameter               | Min  | Max | Units | Conditions                   |

|--------------|-------------------------|------|-----|-------|------------------------------|

| $V_{DD}$     | Power Supply Voltage    | -0.3 | 7   | V     | All pins with respect to GND |

| $T_{A}^{DD}$ | Operating Ambient Temp. | 0    | 70  | °C    |                              |

| $T_s$        | Storage Temperature     | -65  | 150 | °C    |                              |

Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**DC CHARACTERISTICS**  $T_A = 0$ °C to + 70°C;  $V_{CC} = 4.3$  V to + 5.5 V

| Symbol                       | Parameter                | Min                 | Max                 | Typical                                          | Units | Conditions         | Notes    |

|------------------------------|--------------------------|---------------------|---------------------|--------------------------------------------------|-------|--------------------|----------|

| $\overline{V_{_{\rm I\!L}}}$ | Input Voltage Low        | 0                   | 0.2 V <sub>DD</sub> | 0.4                                              | V     | (except XTAL1)     |          |

| $V_{IH}$                     | Input Voltage High       | $0.5 V_{DD}$        | $V_{DD}$            | 3.6                                              | V     | (except XTAL1)     |          |

| $V_{OL1}$                    | Output Voltage Low       | DD                  | 0.16                | 0.4                                              | V     | @ I <sub>OH1</sub> |          |

| $V_{OH1}$                    | Output Voltage High      | $V_{_{DD}}\!-\!0.4$ | 4.75                | $V_{_{D\!D}}$                                    | V     | @ I <sub>OH1</sub> |          |

| $\overline{V}_{OL2}$         | Output Voltage Low       |                     | 0.16                | 0.4                                              | V     | @ I <sub>OH2</sub> |          |

| V <sub>OH2</sub>             | Output Voltage High      | $V_{\rm DD} - 0.4$  | 4.75                | $V_{DD}$                                         | V     | @ I <sub>OH2</sub> |          |

| VX                           | Input Voltage Low        | DD                  |                     | $0.2 \stackrel{\text{DD}}{\text{V}}_{\text{DD}}$ | V     | for XTAL1          |          |

| $VX_{IH1}$                   | Input Voltage High       | $0.7 V_{_{DD}}$     |                     | DD                                               | V     | for XTAL1          |          |

| VX <sub>OL2</sub>            | Output Voltage Low       |                     | 0.16                | 0.4                                              | V     | for XTAL2          | @ 4.5 mA |

| VX <sub>OH2</sub>            | Output Voltage High      | $V_{_{DD}} - 0.4$   | 4.75                | $V_{_{DD}}$                                      | V     | for XTAL2          | @ 3.7 mA |

| $\overline{I_{OL1}}$         | Output Current Low       | 2.5                 |                     |                                                  | mA    |                    |          |

| I <sub>OL1</sub>             | Output Current High      | 1.5                 |                     |                                                  | mA    |                    |          |

| I <sub>OL2</sub>             | Output Current Low       | 10                  |                     |                                                  | mA    |                    |          |

| I <sub>OL2</sub>             | Output Current High      | 6                   |                     |                                                  | mA    |                    |          |

| $\overline{V_{_{DD1}}}$      | Operating Supply Voltage | 4.3                 | 5.0                 | 5.5                                              | V     |                    |          |

| $V_{DD2}$                    | Sleep Supply Voltage     | 3.0                 |                     | 5.5                                              | V     |                    |          |

| $\overline{I_{DD1}}$         | Operating Supply Current |                     |                     | 40                                               | mA    |                    |          |

| $I_{DD2}$                    | Operating Supply Current |                     |                     | 10                                               | μΑ    |                    |          |

AC CHARACTERISTICS  $T_{_A} = 0^{\circ}C \ to + 70^{\circ}C; \ V_{_{DD}} = 4.3 \ \ V \ to + 5.5 \ V$

| Symbol                  | Parameter                                | Min  | Max            | Typical | Units | Conditions | Notes |

|-------------------------|------------------------------------------|------|----------------|---------|-------|------------|-------|

| fosc<br>V <sub>IN</sub> | Oscillator Frequency<br>Absolute Min/Max |      |                | 24      | MHz   |            |       |

| IN                      | Input Voltage Range                      | -0.3 | $V_{DD} + 0.3$ |         | V     |            |       |

| $\overline{V}_{OUT}$    | Absolute Min/Max<br>Output Voltage Range | -0.3 | $V_{DD} + 0.3$ |         | V     |            |       |

# I/O READ ADDRESS REGISTER SUMMARY

| Read Address | Pg | Read Register Accessed             | 86250 Name |

|--------------|----|------------------------------------|------------|

| 0400H        | 31 | Read Test Multiplexer Register     | XRD_MUX    |

| H0080        | 5  | I.R. Receive Data Register         | XIRR_REG   |

| 0C00H        | 6  | ISB Interrupt Status Register      | XRD_STAT   |

| 1000H        | 12 | I.M. Read Data Byte # 1            | XRD_BYT1   |

| 1400H        | 12 | I.M. Read Data Byte # 2            | XRD_BYT2   |

| 1800H        | 6  | I.M. Status and Chip I.D. Register | XSW_LO     |

| 1C00H        | 6  | I.R. Receiver Status Register      | XSW_HI     |

| 6000Н        | 37 | I.R. Blaster Status Register       | XIRB_RD    |

| 6400H        | 38 | Low Power Status Register          | XLP_STAT   |

| 6800H        | 24 | ISB Receive Data Register          | XRRECREG   |

| 6C00H        | 29 | ISB Status Register 2              | XISB_ST2   |

| 7000H        | 16 | CRC-32 Read Register 3             | XRDCRC3    |

| 7400H        | 16 | CRC-32 Read Register 2             | XRDCRC2    |

| 7800H .      | 17 | CRC-32 Read Register 1             | XRDCRC1    |

| 7C00H        | 17 | CRC-32 Read Register 0             | XRDCRC0    |

| 8000H        | 37 | IRB T8 Control Register            |            |

| 8001H        | 37 | IRB T8 / T16 Common Control Reg    |            |

| 8002H        | 37 | IRB T16 Control Register           |            |

| 8003H        | 37 | Reserved                           |            |

| 8004H        | 37 | IRB T8 Low Hold Register           |            |

| 8005H        | 37 | IRB T8 High Hold Register          |            |

| 8006H        | 37 | IRB T16 Low Hold Register          |            |

| 8007H        | 37 | IRB T16 High Hold Register         |            |

| 8008H        | 37 | IRB T16 Low Capture Register       |            |

| 8009H        | 37 | IRB T16 High Capture Register      |            |

| 800AH        | 37 | IRB T8 Low Capture Register        | ·          |

| 800BH        | 37 | IRB T8 High Capture Register       |            |

The Page numbers refer to the schematic page where the register can be found.

I/O Read Address Register Summary Table

# I/O WRITE ADDRESS REGISTER SUMMARY

| Write Address | Pg | Write Register Accessed              | 86250 Name |

|---------------|----|--------------------------------------|------------|

| 80C32 PORT 1  | X  | Various Output Control BITS          |            |

| 80C32 PORT 3  | X  | Various Control and I/O BITS         |            |

| 0000Н         | 3  | Read_BASE_Register_LOW               | XRBASELO   |

| 0400H         | 3  | Read_BASE_Register_HIGH              | XRBASEHI   |

| 0800Н         | 3  | Write_BASE_Register_LOW              | XWBASELO   |

| 0C00H         | 3  | Write_BASE_Register_HIGH             | XWBASEHI   |

| 1000H         | 10 | PWM_Control_Register_LOW             | XPWM_LO    |

| 1400H         | 10 | PWM_Control_Register_HI              | XPWM_HI    |

| 2000H         | 12 | I.M. BUS Address Register            | XL_IM_AD   |

| 2400H         | 12 | I.M. Write Data 1 Register           | XL_IM_D1   |

| 2800H         | 12 | I.M. Write Data 2 Register           | XL_IM_D2   |

| 2C00H         | 12 | I.M. BUS Start Transfer Register     | XSTRT_IM   |

| 3000H         | 9  | I.M. BUS Control Register            | XIM_CTRL   |

| 3400H         | 39 | Low Power Control Register           | XLP_CTRL   |

| 3600H         | 39 | Sleep Start Register                 | XWRSLEEP   |

| 3C00H         | 9  | Security Chip Clock Freq Register    | XCLK_REG   |

| 6000H         | 9  | Output Control Register              | XCNTRL_1   |

| 6400H         | 13 | Refresh Watchdog Register            | XWDOG_CS   |

| 6800H         | 18 | CRÇ-32 Data Register                 | XWR_CRC    |

| 6C00H         | 29 | ISB Control Register                 | XISBCTRL   |

| 7000H         | 24 | ISB Transmit Data Register           | XISBXMIT   |

| 7400H         | 31 | RAM Sequence and 86250 Test Register | XWR_TEST   |

| 7800H         | 38 | I.R. Blaster Control Register 1      | XIRB_WR1   |

| 7C00H         | 38 | I.R. Blaster Control Register 2      | XIRB_WR2   |

| 8000H         | 37 | IRB T8 Control Register              |            |

| 8001H         | 37 | IRB T8 / T16 Common Control Reg      |            |

| 8002H         | 37 | IRB T16 Control Register             |            |

| 8004H         | 37 | IRB T8 Low Hold Register             |            |

| 8005H         | 37 | IRB T8 High Hold Register            |            |

| 8006H         | 37 | IRB T16 Low Hold Register            |            |

| 8007H         | 37 | IRB T16 High Hold Register           |            |

|               |    |                                      | L          |

I/O Write Address Register Summary Table

© 1996 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 FAX 408 370-8056 Internet: http://www.zilog.com